Содержание

- 2. Сумматоры Сумматором называется устройство, предназначенное для выполнения операции сложения над многоразрядными числами. Многоразрядный сумматор состоит из

- 3. Полусумматор Таблица истинности Булевы функции для выходов имеют вид: _ _ Si = AiBi + AiBi

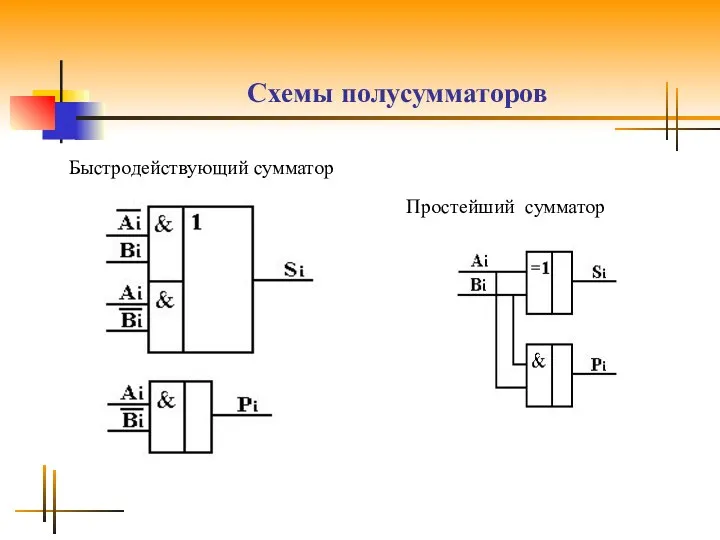

- 4. Схемы полусумматоров Быстродействующий сумматор Простейший сумматор

- 5. Полный сумматор Многоразрядный сумматор, начиная со второго разряда, должен иметь три входа: два входа для слагаемых

- 6. Таблица истинности полного сумматора

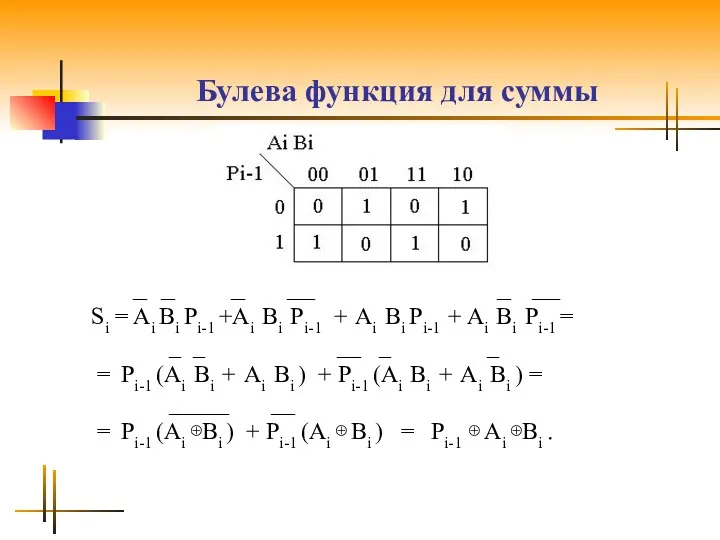

- 7. Булева функция для суммы _ _ _ __ _ __ Si = Ai Bi Pi-1 +Ai

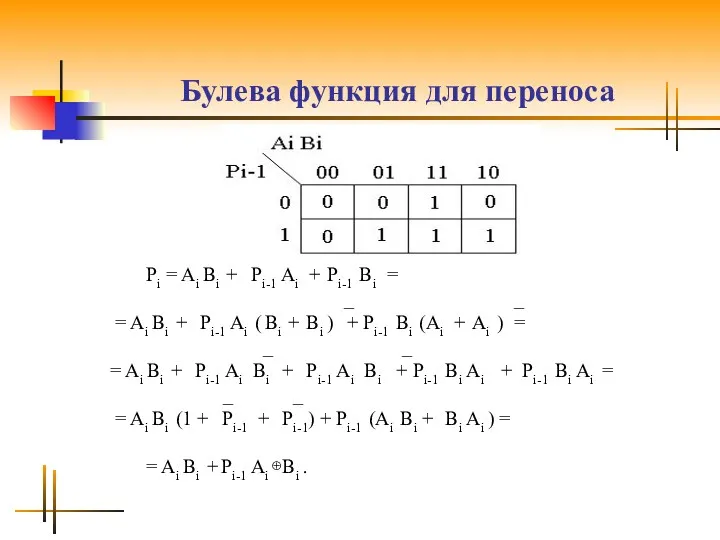

- 8. Булева функция для переноса Pi = Ai Bi + Pi-1 Ai + Pi-1 Bi = _

- 9. Быстродействующий сумматор

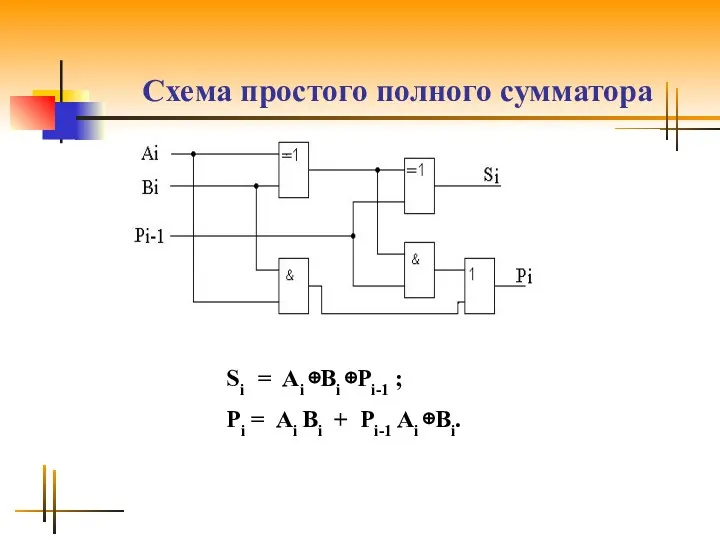

- 10. Схема простого полного сумматора Si = Ai ⊕Bi ⊕Pi-1 ; Pi = Ai Bi + Pi-1

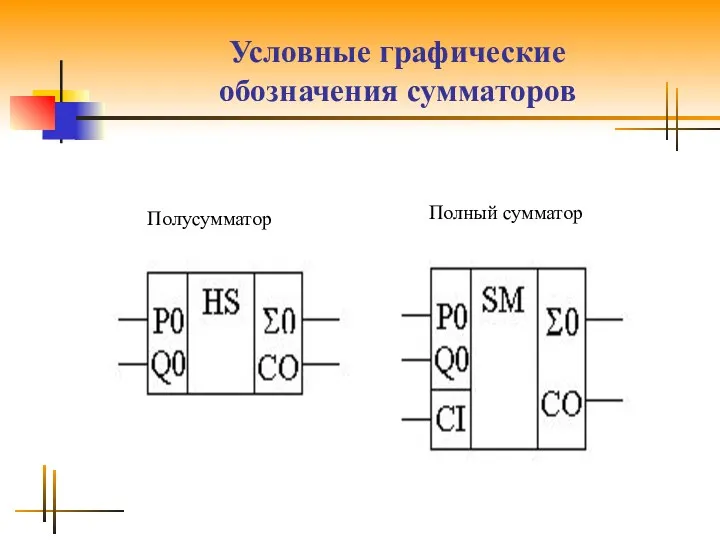

- 11. Условные графические обозначения сумматоров Полусумматор Полный сумматор

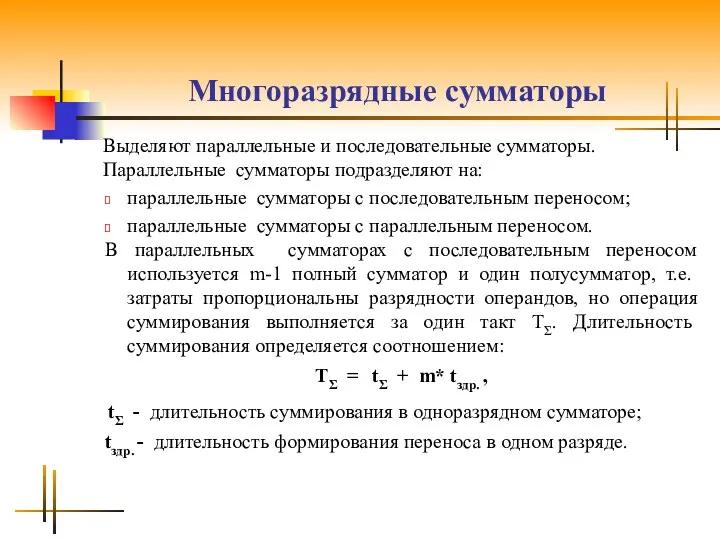

- 12. Многоразрядные сумматоры Выделяют параллельные и последовательные сумматоры. Параллельные сумматоры подразделяют на: параллельные сумматоры с последовательным переносом;

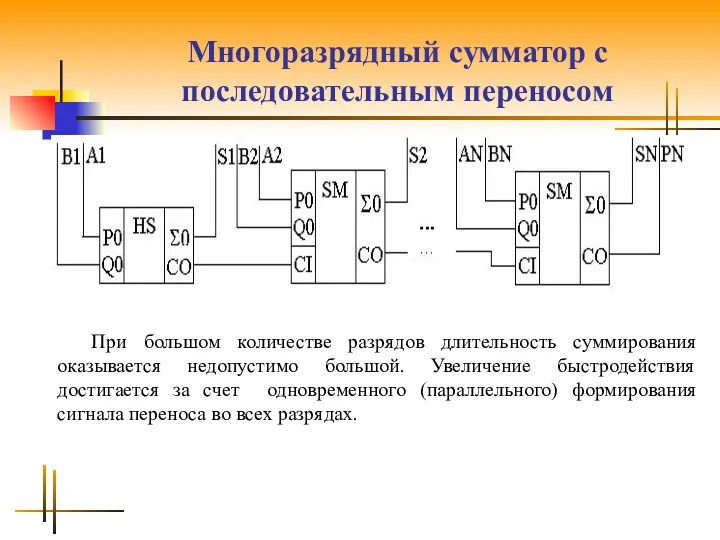

- 13. Многоразрядный сумматор с последовательным переносом При большом количестве разрядов длительность суммирования оказывается недопустимо большой. Увеличение быстродействия

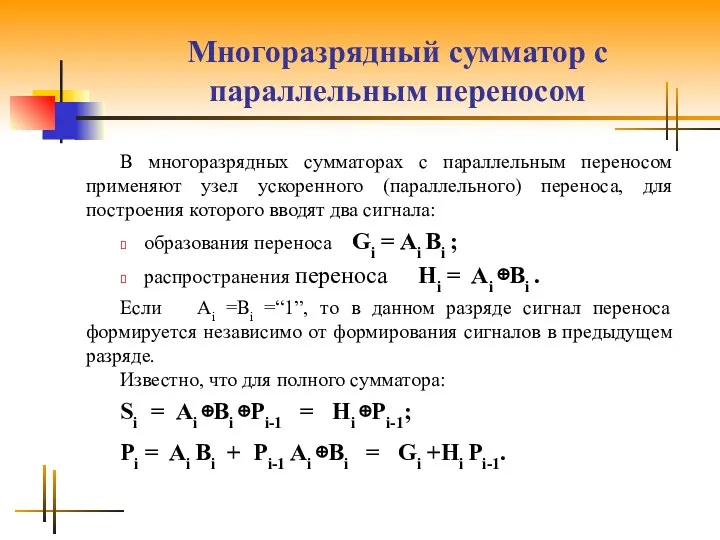

- 14. Многоразрядный сумматор с параллельным переносом В многоразрядных сумматорах с параллельным переносом применяют узел ускоренного (параллельного) переноса,

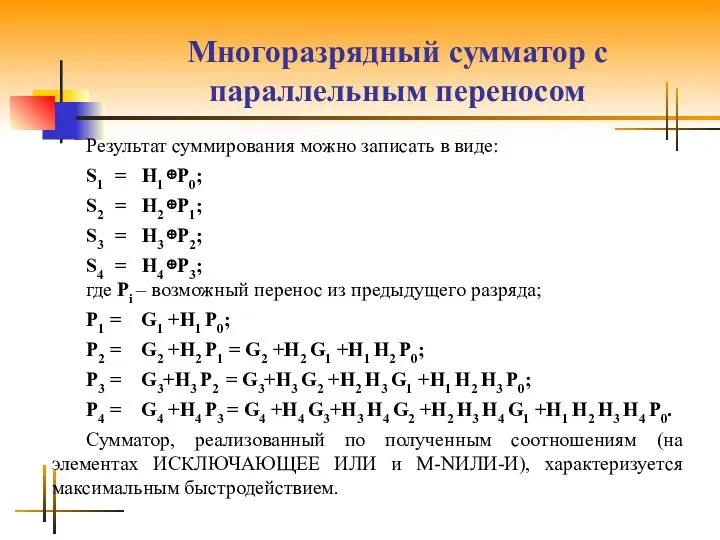

- 15. Многоразрядный сумматор с параллельным переносом Результат суммирования можно записать в виде: S1 = H1 ⊕P0; S2

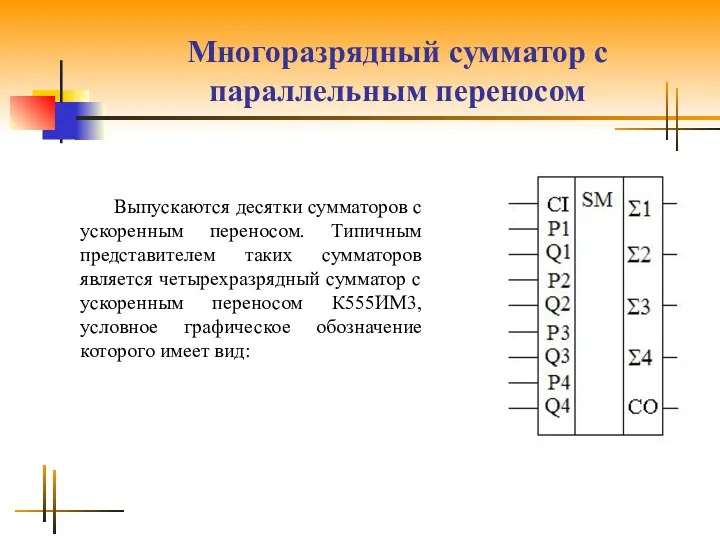

- 16. Многоразрядный сумматор с параллельным переносом Выпускаются десятки сумматоров с ускоренным переносом. Типичным представителем таких сумматоров является

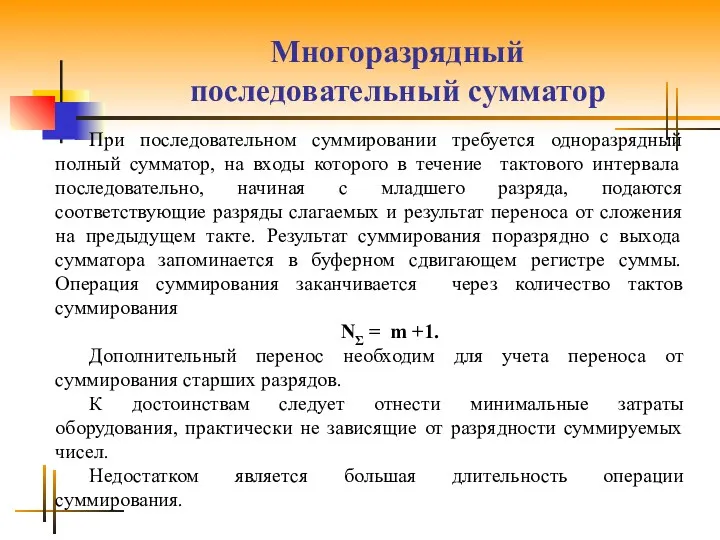

- 17. Многоразрядный последовательный сумматор При последовательном суммировании требуется одноразрядный полный сумматор, на входы которого в течение тактового

- 18. Схема многоразрядного последовательного сумматора

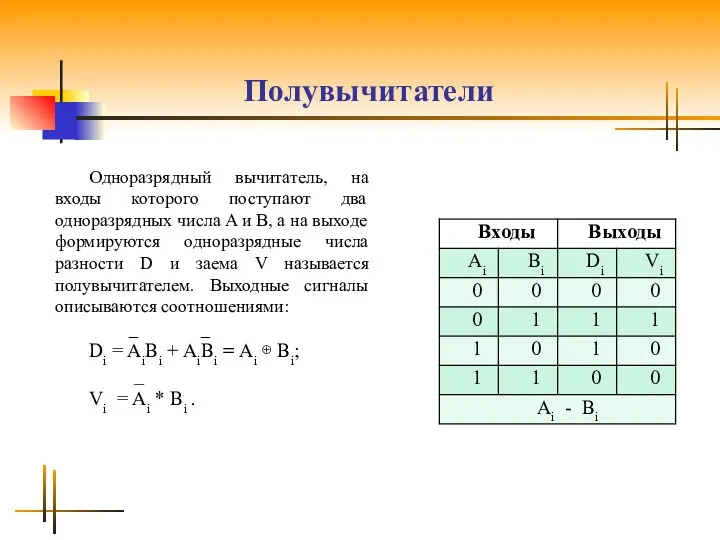

- 19. Полувычитатели Одноразрядный вычитатель, на входы которого поступают два одноразрядных числа A и B, а на выходе

- 20. Полувычитатели Возможны различные реализации полувычитателей на основании тождественных преобразований полученных функций. Схема полувычитателя отличается от схемы

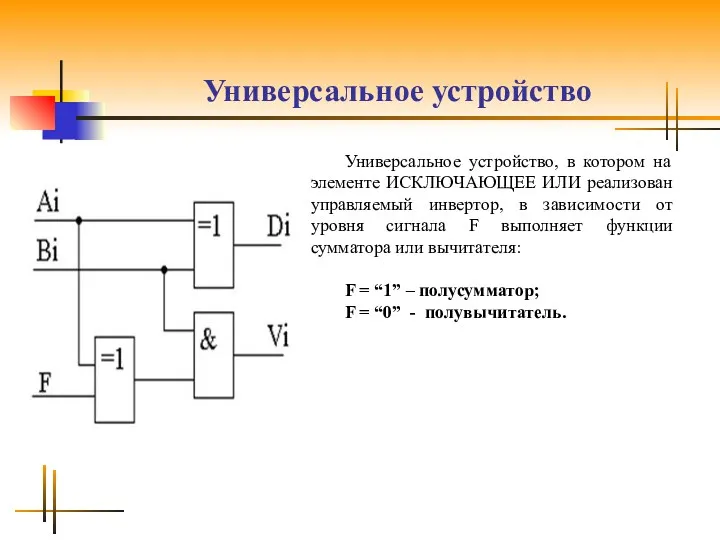

- 21. Универсальное устройство Универсальное устройство, в котором на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ реализован управляемый инвертор, в зависимости от

- 22. Полный вычитатель Полным вычитателем называется устройство, реализующее операцию вычитания одноразрядных чисел с учетом заема из предыдущего

- 23. Таблица истинности полного вычитателя

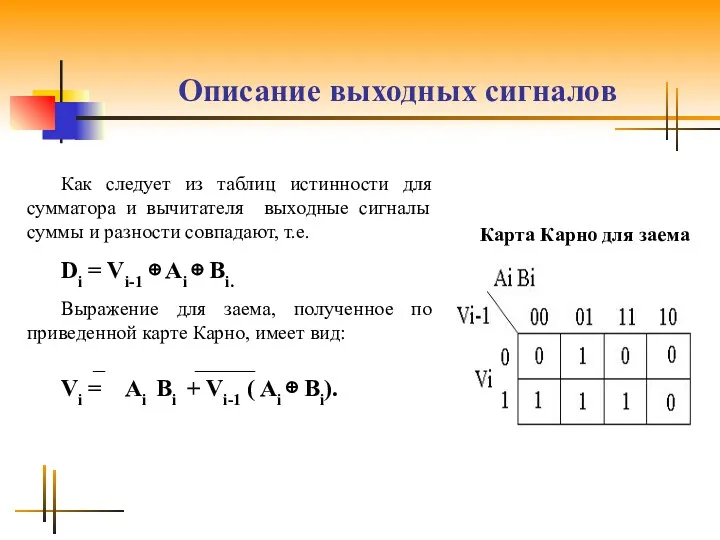

- 24. Описание выходных сигналов Как следует из таблиц истинности для сумматора и вычитателя выходные сигналы суммы и

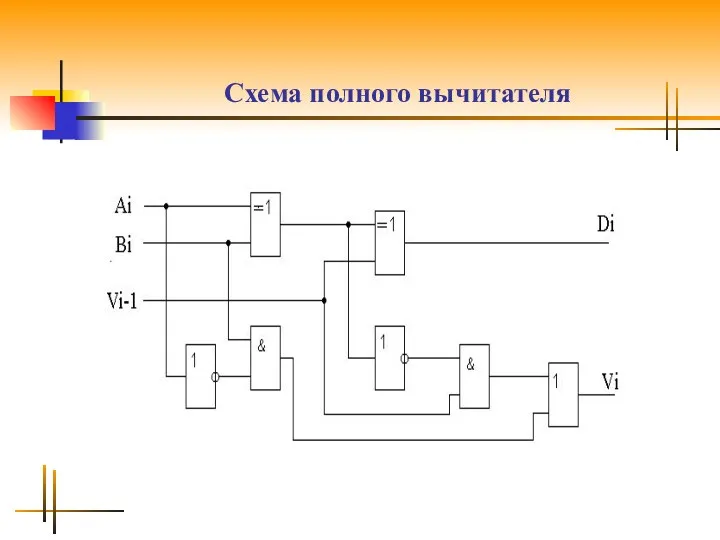

- 25. Схема полного вычитателя

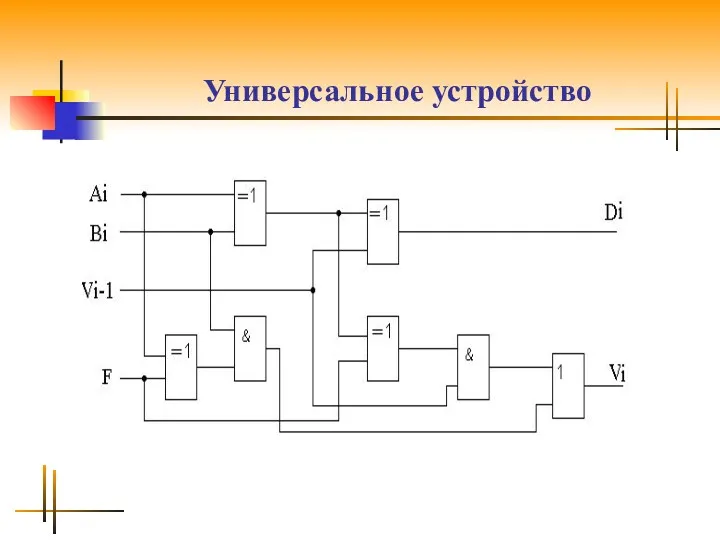

- 26. Универсальное устройство

- 27. Построение универсальных устройств В вычислительных устройствах применяют сумматоры и вычитатели. Для упрощения схемной реализации вычислительных устройств

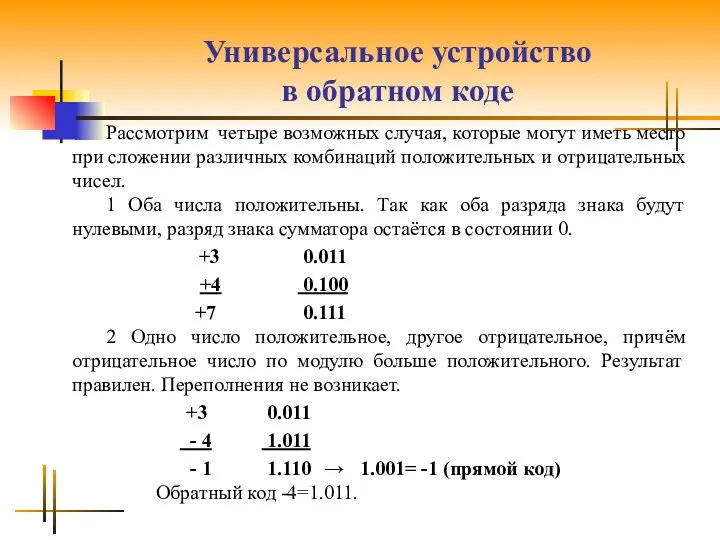

- 28. Универсальное устройство в обратном коде Рассмотрим четыре возможных случая, которые могут иметь место при сложении различных

- 29. Универсальное устройство в обратном коде 3 Положительное число по модулю больше отрицательного. Сумма неправильна! Прибавление к

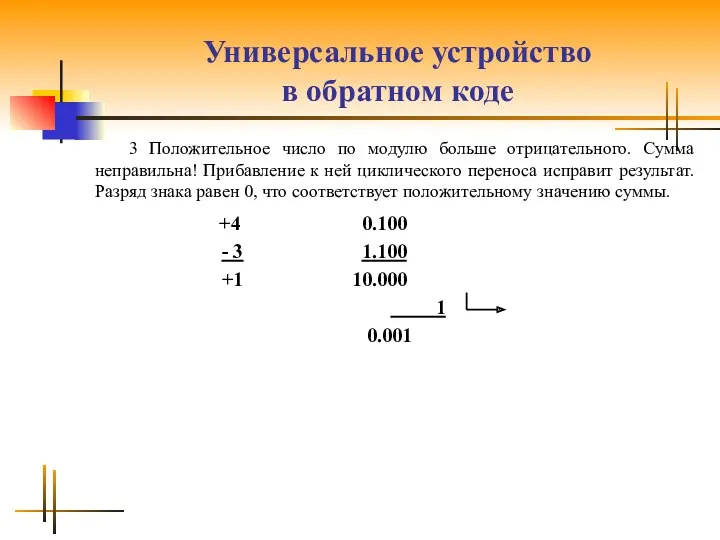

- 30. Универсальное устройство в обратном коде 4 Оба числа отрицательны, всегда возникает циклический перенос. Поэтому разряд знака

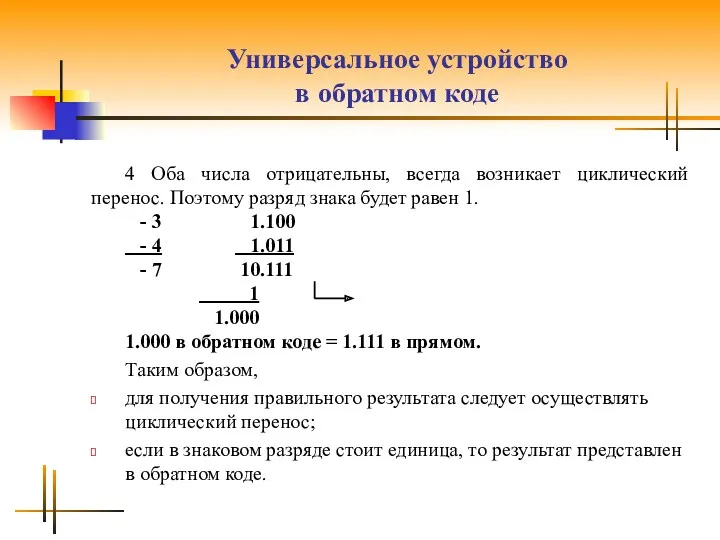

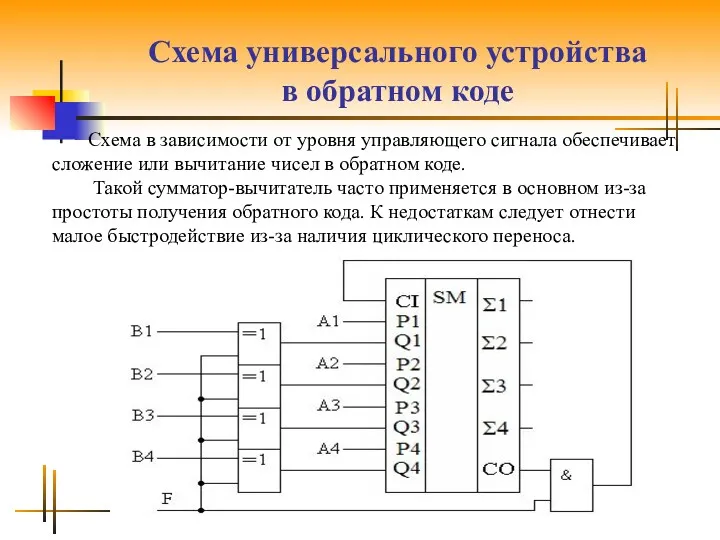

- 31. Схема универсального устройства в обратном коде Схема в зависимости от уровня управляющего сигнала обеспечивает сложение или

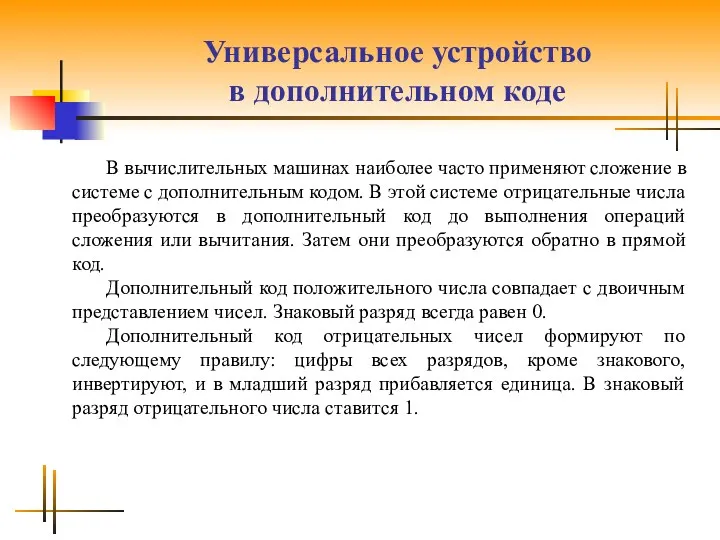

- 32. Универсальное устройство в дополнительном коде В вычислительных машинах наиболее часто применяют сложение в системе с дополнительным

- 33. Универсальное устройство в дополнительном коде Возможны четыре случая, которые могут иметь место при сложении различных комбинаций

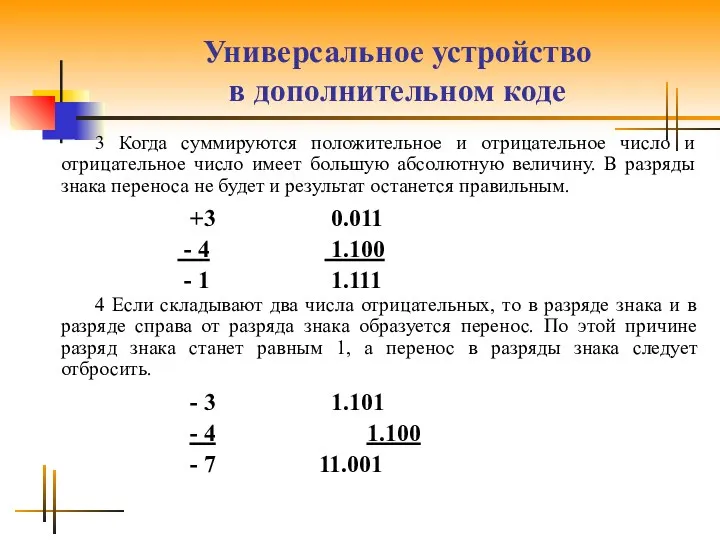

- 34. Универсальное устройство в дополнительном коде 3 Когда суммируются положительное и отрицательное число и отрицательное число имеет

- 35. Схема универсального устройства в дополнительном коде

- 37. Скачать презентацию

Активное долголетие

Активное долголетие Концептуальная модель UML и ее элементы. Лекция 3

Концептуальная модель UML и ее элементы. Лекция 3 Основные принципы построения компьютеров

Основные принципы построения компьютеров Презентация Строки

Презентация Строки Операциялық жүйелер. Операциялық жүйелердің даму тарихы

Операциялық жүйелер. Операциялық жүйелердің даму тарихы Создание второго кампуса Университета ИТМО – комплексный проект ИТМО Хайпарк

Создание второго кампуса Университета ИТМО – комплексный проект ИТМО Хайпарк Деректер қорыдағы деректердің түрлі ұсыныстары. Деректер қорын жобалаудың негізгі кезеңдері

Деректер қорыдағы деректердің түрлі ұсыныстары. Деректер қорын жобалаудың негізгі кезеңдері Программирование реконфигурируемой вычислительной системы

Программирование реконфигурируемой вычислительной системы Уровни и виды тестирования

Уровни и виды тестирования Организация тестирования в команде разработчиков. Виды и методы тестирования

Организация тестирования в команде разработчиков. Виды и методы тестирования Creation of a simple network configuration

Creation of a simple network configuration Система межпроцессного взаимодействия IPC

Система межпроцессного взаимодействия IPC История вычислительной техники

История вычислительной техники Принципы организации внутренней и внешней памяти компьютера

Принципы организации внутренней и внешней памяти компьютера Install Linux 10.2 and Caldera 14.1

Install Linux 10.2 and Caldera 14.1 Социальная память. Функция социальной памяти

Социальная память. Функция социальной памяти Windows 10

Windows 10 Как создать свой сайт?

Как создать свой сайт? Операционные системы, среды и оболочки. Процессы в операционных системах

Операционные системы, среды и оболочки. Процессы в операционных системах Основные функции современной офисной автоматизации. Занятие №2

Основные функции современной офисной автоматизации. Занятие №2 Замісник (проксі). Патерни проектування

Замісник (проксі). Патерни проектування DS Графический дизайн. Композиция

DS Графический дизайн. Композиция Объектно-ориентированное программирование на алгоритмическом языке С++

Объектно-ориентированное программирование на алгоритмическом языке С++ Двоичная сс. Двоичная арифметика

Двоичная сс. Двоичная арифметика Системи масового обслуговування

Системи масового обслуговування Вступ. Історія розвитку мови програмування С++

Вступ. Історія розвитку мови програмування С++ Операційна система Windows

Операційна система Windows Macroscop. Технический минимум

Macroscop. Технический минимум