Содержание

- 2. ПРЕИМУЩЕСТВА ПРЕДЛАГАЕМОГО РЕШЕНИЯ Единое языковое пространство для синтеза вычислительной структуры и программирования информационных потоков 2. Ресурсонезависимое

- 3. ЯЗЫК COLAMO Основные отличительные особенности: Массивы различаются по типу доступа: Stream(последовательный доступ) и Vector(параллельный доступ); Переменные

- 4. Системное программное обеспечение Направления исследований: 1) Трансляция языка высокого уровня COLAMO. 2) Синтез схемотехнических решений на

- 5. Трансляция языка высокого уровня COLAMO Области исследований: – масштабирование параллельной программы; – преобразование типов данных; –

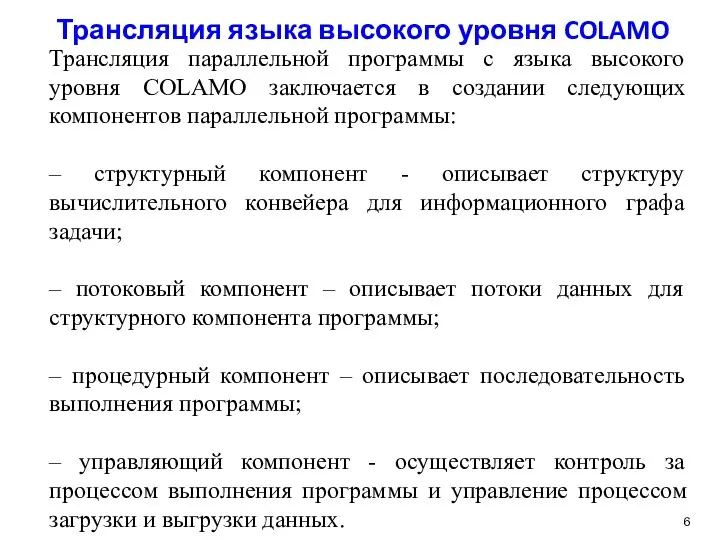

- 6. Трансляция языка высокого уровня COLAMO Трансляция параллельной программы с языка высокого уровня COLAMO заключается в создании

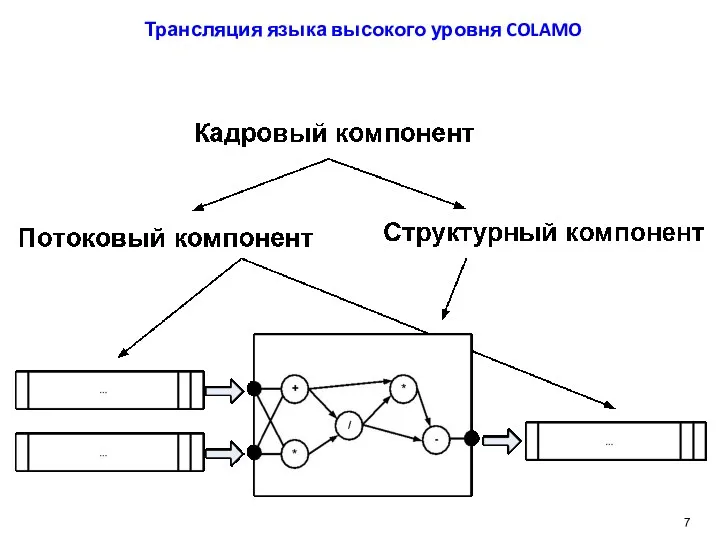

- 7. Трансляция языка высокого уровня COLAMO

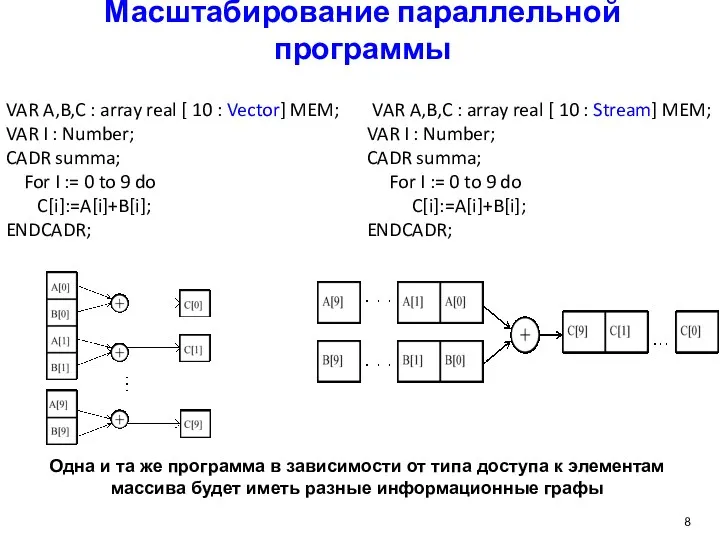

- 8. Масштабирование параллельной программы VAR A,B,C : array real [ 10 : Stream] MEM; VAR I :

- 9. Масштабирование параллельной программы Var a : Array Integer [10:Vector] Mem; Var c : Array Integer [10:Stream]

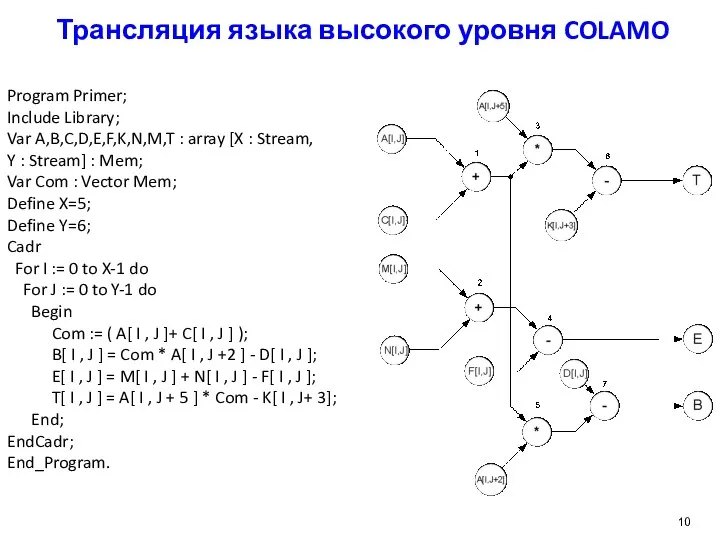

- 10. Трансляция языка высокого уровня COLAMO Program Primer; Include Library; Var A,B,C,D,E,F,K,N,M,T : array [X : Stream,

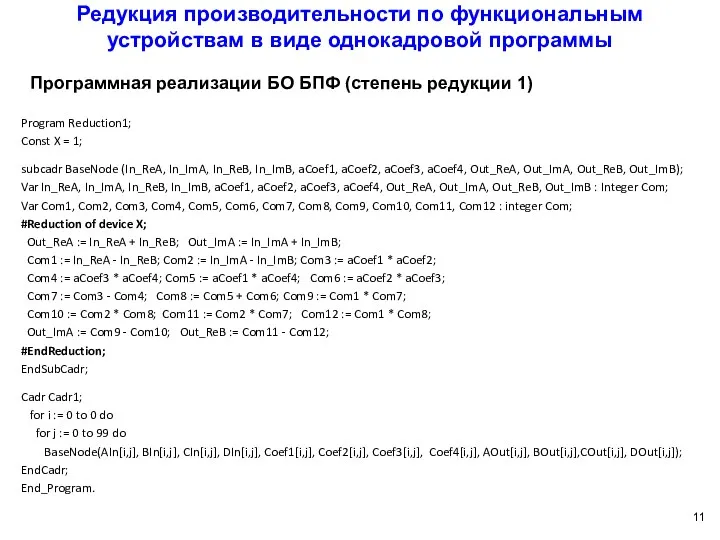

- 11. Редукция производительности по функциональным устройствам в виде однокадровой программы Program Reduction1; Const X = 1; subcadr

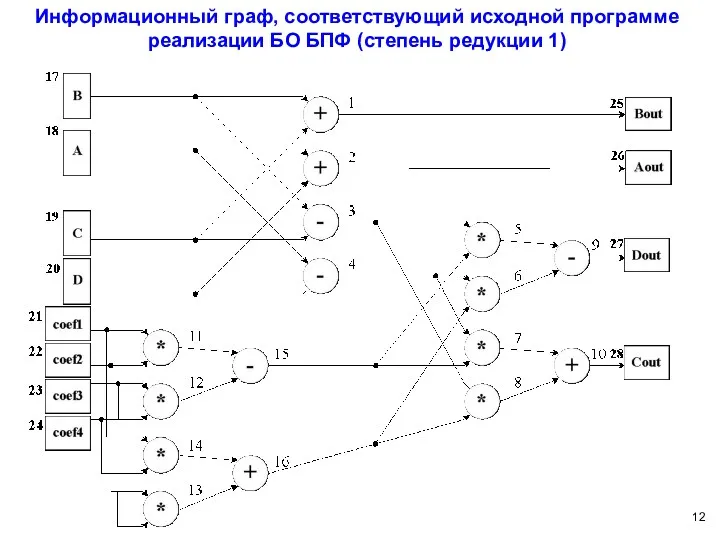

- 12. Информационный граф, соответствующий исходной программе реализации БО БПФ (степень редукции 1)

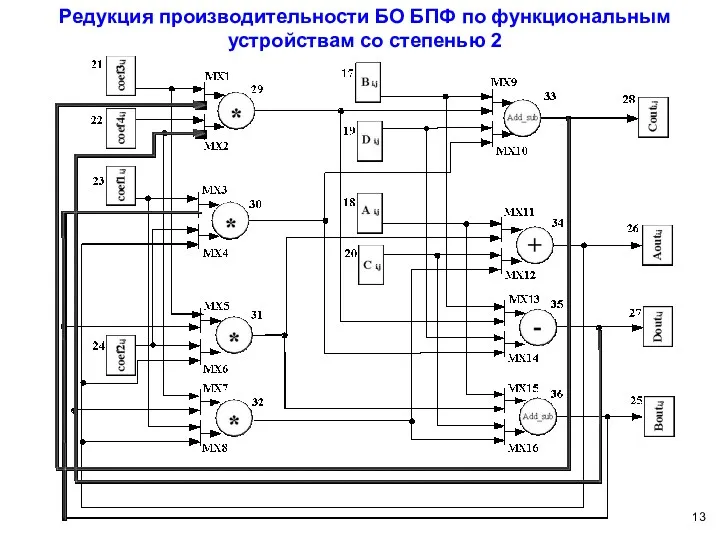

- 13. Редукция производительности БО БПФ по функциональным устройствам со степенью 2

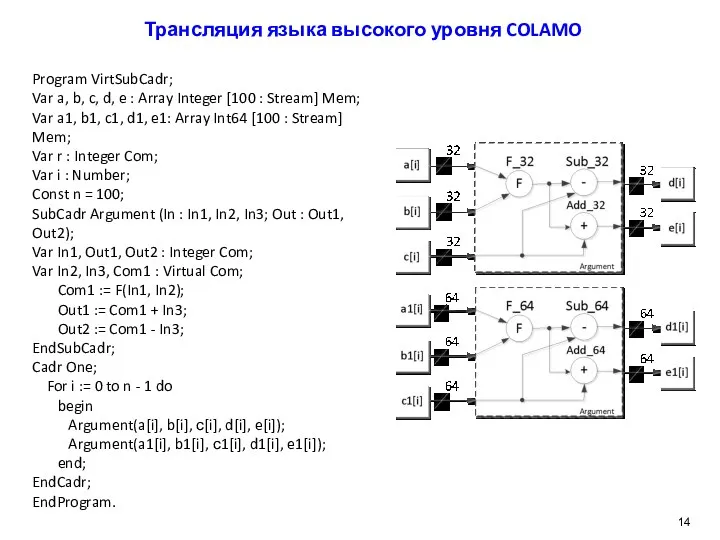

- 14. Трансляция языка высокого уровня COLAMO Program VirtSubCadr; Var a, b, c, d, e : Array Integer

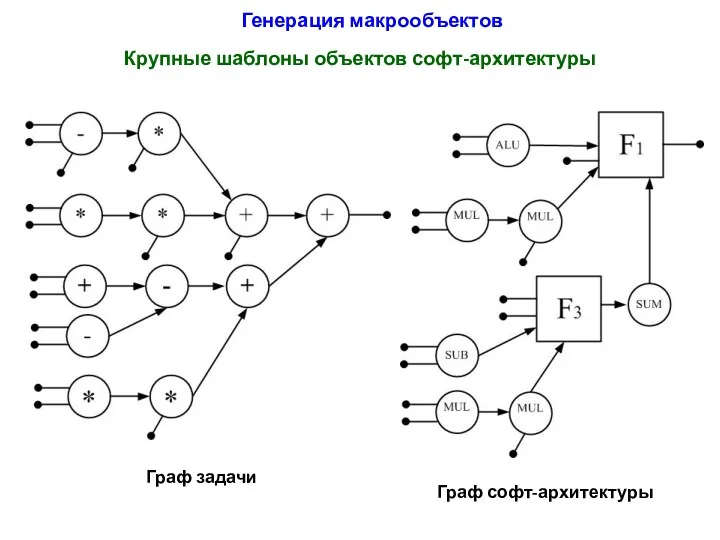

- 15. Граф задачи Крупные шаблоны объектов софт-архитектуры Граф софт-архитектуры Генерация макрообъектов

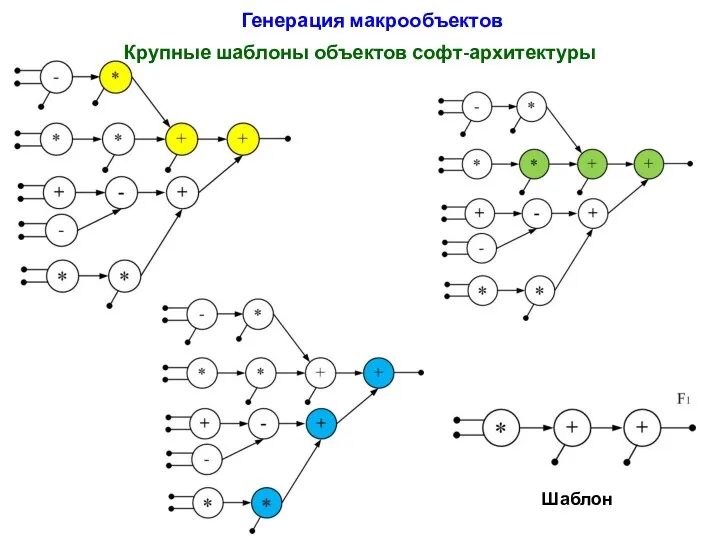

- 16. Крупные шаблоны объектов софт-архитектуры Шаблон Генерация макрообъектов

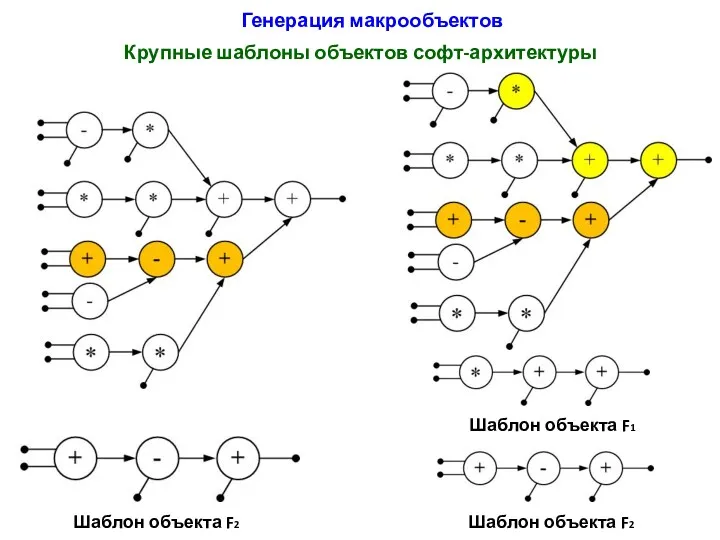

- 17. Крупные шаблоны объектов софт-архитектуры Шаблон объекта F2 Шаблон объекта F1 Шаблон объекта F2 Генерация макрообъектов

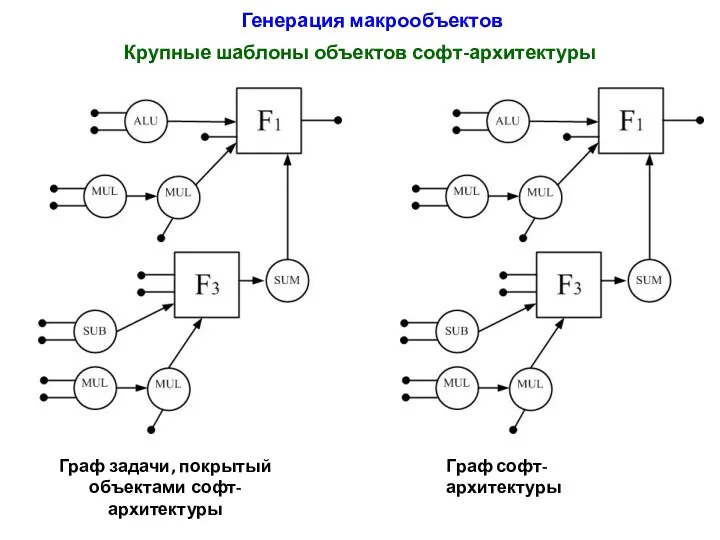

- 18. Крупные шаблоны объектов софт-архитектуры Граф задачи, покрытый объектами софт-архитектуры Граф софт-архитектуры Генерация макрообъектов

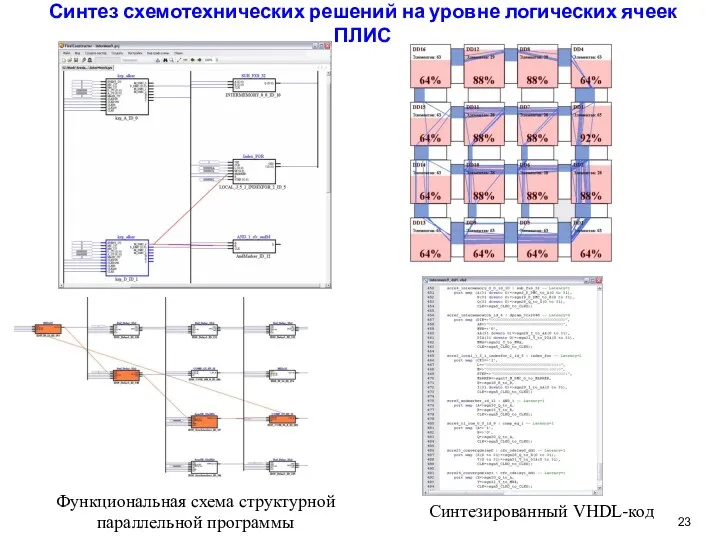

- 19. Синтез схемотехнических решений на уровне логических ячеек ПЛИС Области исследований: -поиск сильносвязных фрагментов вычислительных структур параллельных

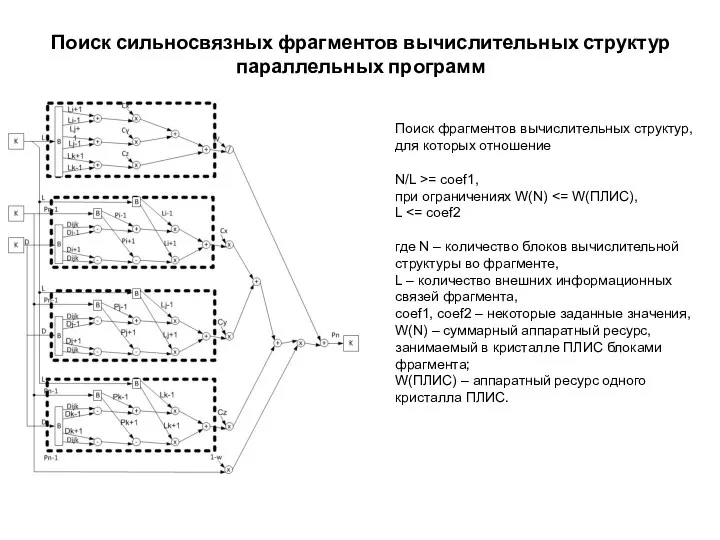

- 20. Поиск сильносвязных фрагментов вычислительных структур параллельных программ Поиск фрагментов вычислительных структур, для которых отношение N/L >=

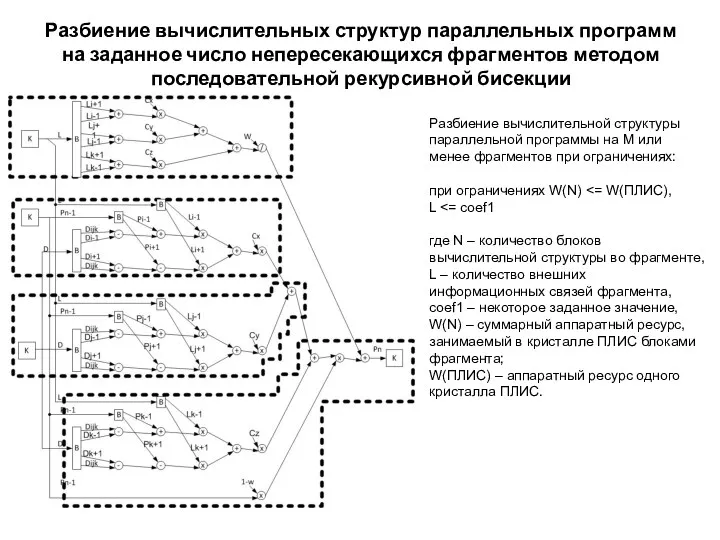

- 21. Разбиение вычислительных структур параллельных программ на заданное число непересекающихся фрагментов методом последовательной рекурсивной бисекции Разбиение вычислительной

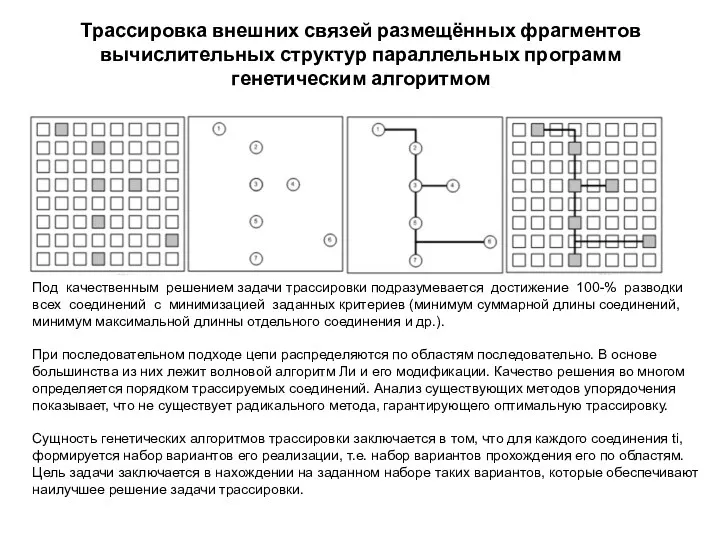

- 22. Трассировка внешних связей размещённых фрагментов вычислительных структур параллельных программ генетическим алгоритмом Под качественным решением задачи трассировки

- 23. Синтез схемотехнических решений на уровне логических ячеек ПЛИС Функциональная схема структурной параллельной программы Синтезированный VHDL-код

- 24. Синтез конфигурации на уровне макрообъектов Области исследований: -многоуровневая визуализация результатов отображения многокадровых задач на софт-архитектуру РВС;

- 25. Многоуровневая визуализация результатов отображения многокадровых задач на софт-архитектуру РВС Необходимо обеспечить возможность визуализации: софт-архитектуры РВС без

- 26. Проверка возможности успешного отображения многокадровой задачи на софт-архитектуру РВС путем анализа структуры кадров задачи и имеющегося

- 27. Поиск вариантов размещения Complex-структур информационного графа кадра многокадровой задачи на множество объектов софт-архитектуры РВС Complex-структуры информационного

- 28. Процедура трассировки внешних связей между размещенными вершинами информационного графа кадра прикладной задачи Процедура трассировки должна обеспечивать

- 29. Трансляция языка описания софт-архитектур на языке SADL Области исследований и разработки: –портация прикладных программ на различные

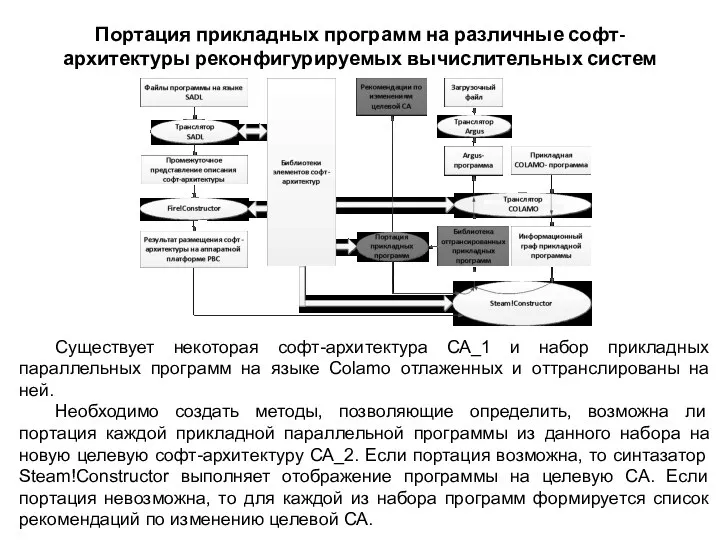

- 30. Портация прикладных программ на различные софт-архитектуры реконфигурируемых вычислительных систем Существует некоторая софт-архитектура СА_1 и набор прикладных

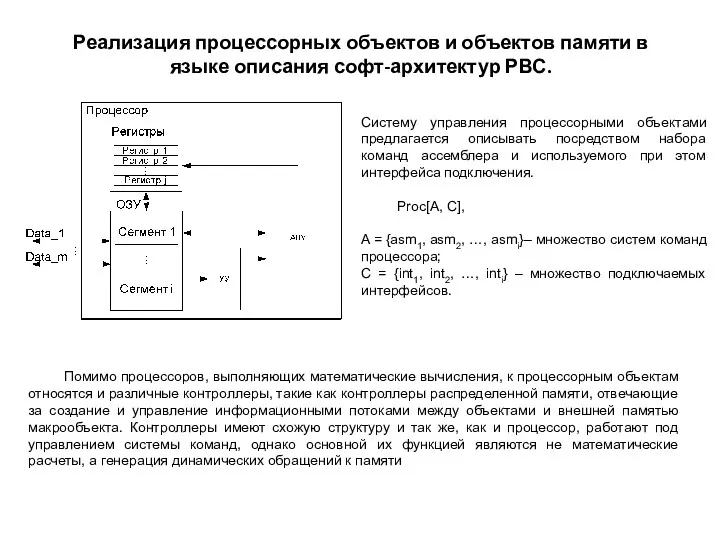

- 31. Реализация процессорных объектов и объектов памяти в языке описания софт-архитектур РВС. Помимо процессоров, выполняющих математические вычисления,

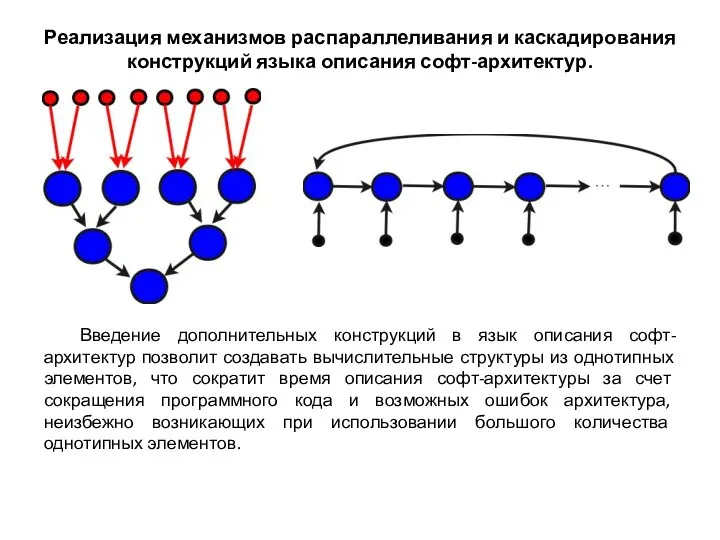

- 32. Введение дополнительных конструкций в язык описания софт-архитектур позволит создавать вычислительные структуры из однотипных элементов, что сократит

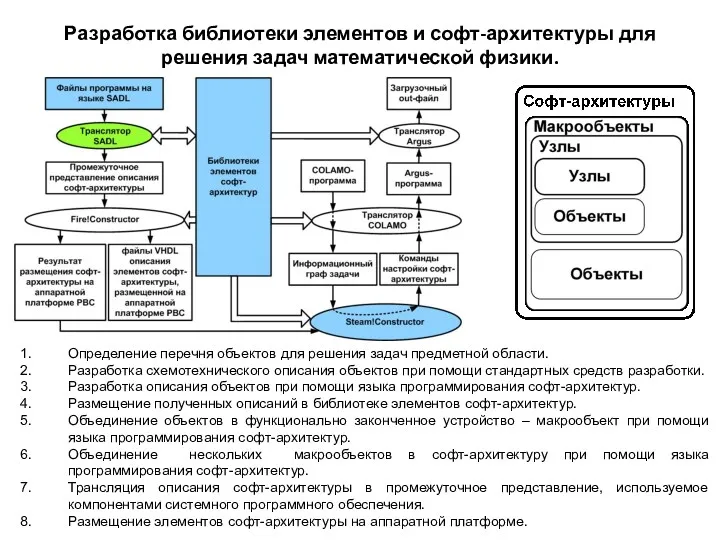

- 33. Разработка библиотеки элементов и софт-архитектуры для решения задач математической физики. Определение перечня объектов для решения задач

- 34. Оптимизация вычислительной структуры прикладной задачи Области исследований и разработки: –декомпозиция графа; –модификация смежных комбинационных схем; –оптимизация

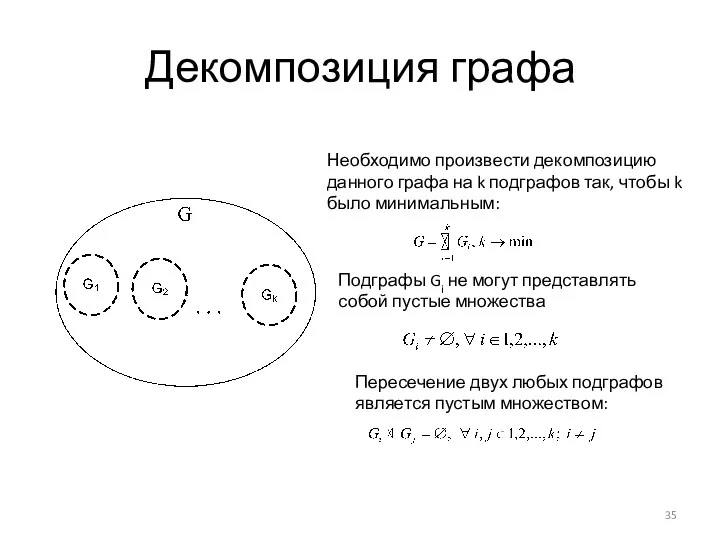

- 35. Декомпозиция графа Необходимо произвести декомпозицию данного графа на k подграфов так, чтобы k было минимальным: Пересечение

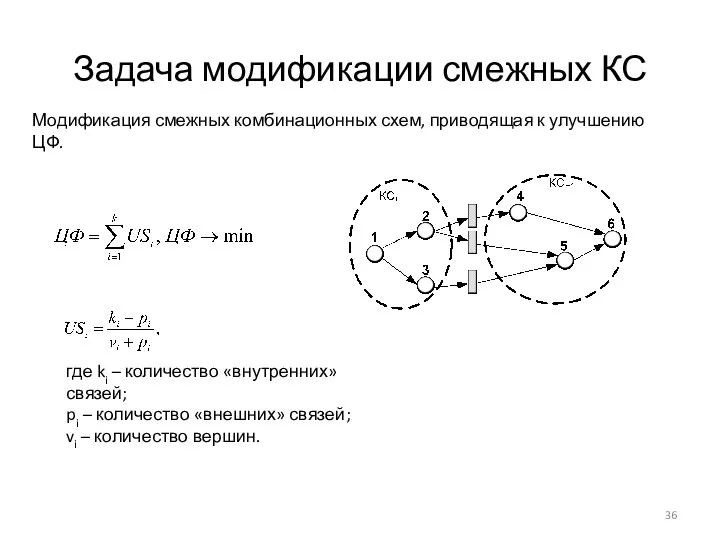

- 36. Задача модификации смежных КС Модификация смежных комбинационных схем, приводящая к улучшению ЦФ. где ki – количество

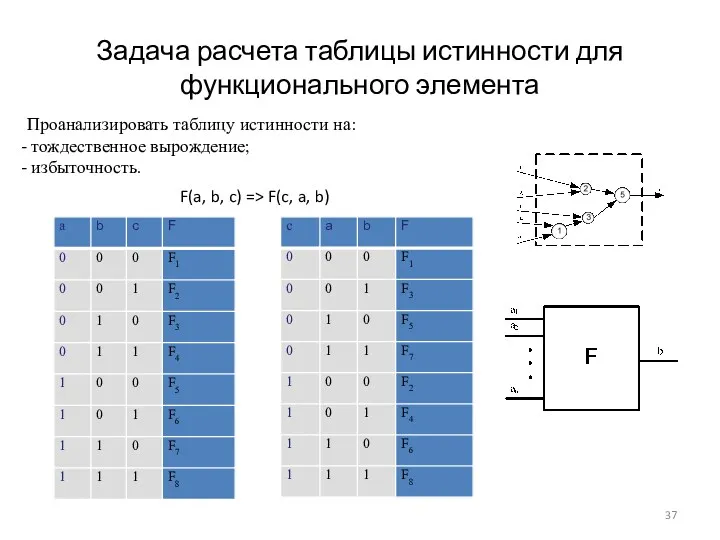

- 37. Задача расчета таблицы истинности для функционального элемента F(a, b, c) => F(c, a, b) Проанализировать таблицу

- 39. Скачать презентацию

![Масштабирование параллельной программы Var a : Array Integer [10:Vector] Mem;](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/323444/slide-8.jpg)

Азбука журналистики

Азбука журналистики Методы и средства хранения информации

Методы и средства хранения информации Сел қауіптілігін карторграфиялауға арналған геоақпараттық жүйелер

Сел қауіптілігін карторграфиялауға арналған геоақпараттық жүйелер Защита информации в базах данных

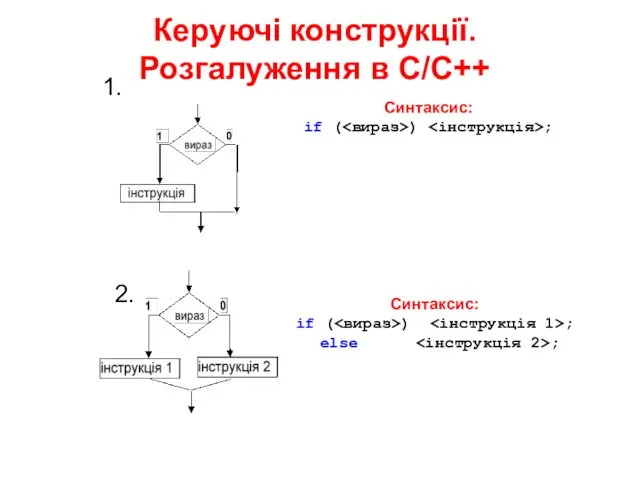

Защита информации в базах данных Керуючі конструкції. Розгалуження в С/C++

Керуючі конструкції. Розгалуження в С/C++ Вёрстка и дизайн газетной статьи

Вёрстка и дизайн газетной статьи Всемирная компьютерная сеть интернет. Опорный конспект

Всемирная компьютерная сеть интернет. Опорный конспект Составляющие информационной технологии

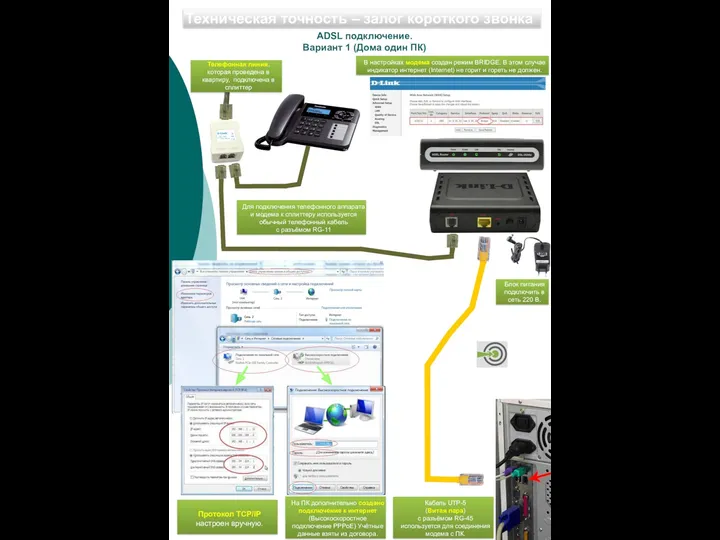

Составляющие информационной технологии Шесть видов подключения интернета

Шесть видов подключения интернета NAVY. Проблемы в создании рекламных роликов

NAVY. Проблемы в создании рекламных роликов Программирование в компьютерных системах

Программирование в компьютерных системах FaceByte UI Review

FaceByte UI Review Операционная система

Операционная система Минимальные маршруты и покрытия. Лекция 5

Минимальные маршруты и покрытия. Лекция 5 Измерение информации

Измерение информации Современная поэзия. Где смотреть

Современная поэзия. Где смотреть Презентация по теме Основы алгоритмизации

Презентация по теме Основы алгоритмизации Компьютерная лексикография (электронные словари в интернете)

Компьютерная лексикография (электронные словари в интернете) Проектная деятельность на уроках информатики

Проектная деятельность на уроках информатики Право и этика в Интернете

Право и этика в Интернете Графика в Quick Basic

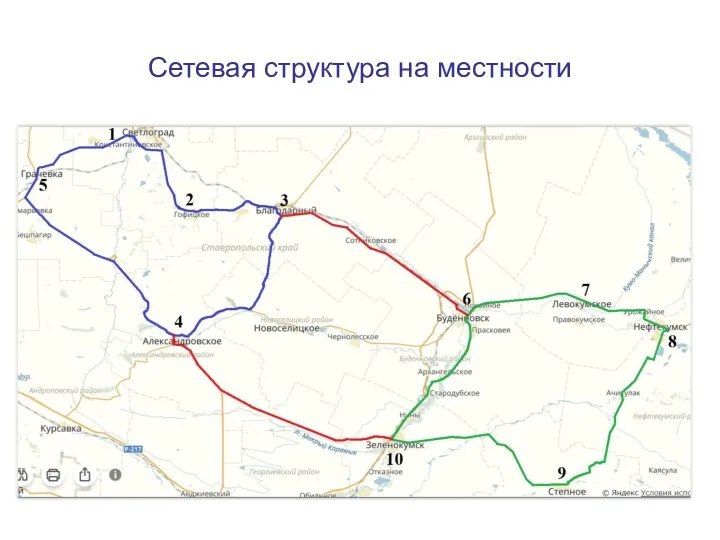

Графика в Quick Basic Сетевая структура на местности

Сетевая структура на местности Информация. Аппаратура компьютера

Информация. Аппаратура компьютера Правила создания презентаций.Урок родного (русского) языка.. 6 класс

Правила создания презентаций.Урок родного (русского) языка.. 6 класс Создание видеоклипа из цифровых фотографий

Создание видеоклипа из цифровых фотографий Сжатие, архивация и разархивация данных. Архиваторы. Работа с архивами

Сжатие, архивация и разархивация данных. Архиваторы. Работа с архивами Widgets. Custom Widgets Types

Widgets. Custom Widgets Types Презентация:Базы данных Урок 11 класс; Урок: Моделирование как метод познания.

Презентация:Базы данных Урок 11 класс; Урок: Моделирование как метод познания.