Содержание

- 2. Оператор параллельного назначения сигналов Простое назначение сигналов: status even arith_out Как можно оптимизировать схему, чтобы уменьшить

- 3. Назначение сигналов с обратной связью Нельзя назначать сигналы с обратной связью! q q architecture right_arch of

- 4. Оператор условного назначения сигналов сигнал выражение_2 when условие_2 else .... выражение_(n-1) when условие_(n-1) else выражение_n;

- 5. Пример 1. Мультиплексор 8 бит 4-в-1 library ieee; use ieee.std_logic_1164.all; entity mux4 is port( a, b,

- 6. Пример 2. Бинарный дешифратор library ieee; use ieee.std_logic_1164.all; entity decoder4 is port( s: in std_logic_vector(1 downto

- 7. Пример 3. Шифратор приоритета library ieee; use ieee.std_logic_1164.all; entity prio_encoder42 is port( r: in std_logic_vector(3 downto

- 8. Семантика оператора условного назначения сигнала подразумевает создание приоритетной схемы, т.е. условия, стоящие выше имеют больший приоритет.

- 9. Одноуровневая схема приоритета i1, i2, o – n-битные шины sel – boolean Реализуется на основе абстрактного

- 10. Трехуровневая схема приоритета

- 11. Трехуровневая схема приоритета Например, мультиплексор 4-в-1 может быть реализован следующим образом:

- 12. Оператор выборочного назначения сигналов Выборочные значения должны быть взаимно исключающими (значения не должны перекрываться или повторяться)

- 13. Пример 1. Мультиплексор 8 бит 4-в-1 architecture sel_arch of mux4 is begin with s select x

- 14. Пример 2. Бинарный дешифратор architecture sel_arch of decoder4 is begin with sel select x "0010" when

- 15. Пример 3. Шифратор приоритета architecture sel_arch of prio_encoder42 is begin with r select code "1100" |

- 16. Синтез оператора выборочного назначения сигналов Мультиплексор 4-в-1. Симметричная схема, все входы равноправны, приоритета нет. Абстрактный мультиплексор

- 17. Сравнение операторов На примере мультиплексора 4-в-1. Оператор условного назначения (when-else) Оператор выборочного назначения (with-select-when) Логика одна

- 18. Последовательные операторы. Оператор процесса. process(список_чувствительности) объявления; begin последовательные_операторы; последовательные_операторы; end process; Сам оператор процесса является параллельным

- 19. Последовательные операторы. Оператор процесса Синтаксис: имя_сигнала Внутри процесса сигналу можно присвоить значение несколько раз. При этом

- 20. Последовательные операторы. Оператор wait Процесс с операторами ожидания имеет один или более операторов wait, но не

- 21. Оператор IF Какой язык программирования обходится без этого оператора? ) if условие_1 then последовательные_операторы; elsif условие_2

- 22. Пример 1. Мультиплексор 4-в-1 architecture if_arch of mux4 is begin process (a, b, c, d, s)

- 23. Пример 2. Бинарный дешифратор architecture if_arch of decoder4 is begin process (s) begin if (s =

- 24. Пример 3. Шифратор приоритета architecture if_arch of prio_encoder42 is begin process (r) begin if (r(3) =

- 25. Оператор IF. Сравнение с оператором условного назначения Для простых случаев полностью совпадает (по семантике). Отличия: По

- 26. Проблема неполного дерева условий оператора IF Пример неправильного использования оператора IF: process(a,b) begin if (a =

- 27. Проблема неполного дерева условий оператора IF Правильно: Для описания комбинационной цепи необходимо всегда включать ветку else,

- 28. В общем случае оператор IF имеет несколько веток. Возможно, что сигналу присваивается значение не во всех

- 29. Правильно: Проблема неполного назначения сигналов в операторе IF process(a,b) begin gt eq lt if (a >

- 30. Оператор CASE Выборочные значения должны быть полными и взаимоисключающими. case задающее_выражение is when выбор_1 => последовательные_операторы;

- 31. Пример 1. Мультиплексор 4-в-1 architecture case_arch of mux4 is begin process (a, b, c, d, s)

- 32. Пример 2. Бинарный дешифратор architecture case_arch of decoder4 is begin proc1: process (s) begin case s

- 33. Пример 3. Шифратор приоритета architecture case_arch of prio_encoder42 is begin process (r) begin case r is

- 34. Оператор CASE. Сравнение с оператором выборочного назначения with задающее_выражение select сигнал выражение_1 when выбор_1, выражение_2 when

- 35. Оператор CASE. Проблема неполного назначения сигналов Рассмотрим простой шифратор приоритета: Подразумевается, что в один момент времени

- 36. Оператор CASE. Проблема неполного назначения сигналов process(a) begin high middle low case a is when "100"

- 38. Скачать презентацию

Многопоточное программирование

Многопоточное программирование Численные методы решения задач

Численные методы решения задач Основы программирования ФИСТ. Двухмерные массивы. Практика 3

Основы программирования ФИСТ. Двухмерные массивы. Практика 3 Организационные и технические способы и средства защиты информации. Шифровальная (криптографическая) защита информации

Организационные и технические способы и средства защиты информации. Шифровальная (криптографическая) защита информации Implementation. Communication plan

Implementation. Communication plan Дерево целей - как метод исследования

Дерево целей - как метод исследования Мы в современном медиапространстве

Мы в современном медиапространстве Декоративно-прикладне мистецтво. Підручник

Декоративно-прикладне мистецтво. Підручник п. 2-4-2 (8 кл. дистант)

п. 2-4-2 (8 кл. дистант) Алгоритмы с ветвлениями

Алгоритмы с ветвлениями Социальные сети

Социальные сети 1С: Предприятие

1С: Предприятие Целевая аудитория логистического портала в электронной торговле

Целевая аудитория логистического портала в электронной торговле Інформатика. Комплексна практична робота: Комп'ютерні презентації та публікації. (10 клас)

Інформатика. Комплексна практична робота: Комп'ютерні презентації та публікації. (10 клас) Construction and optimization of algorithms

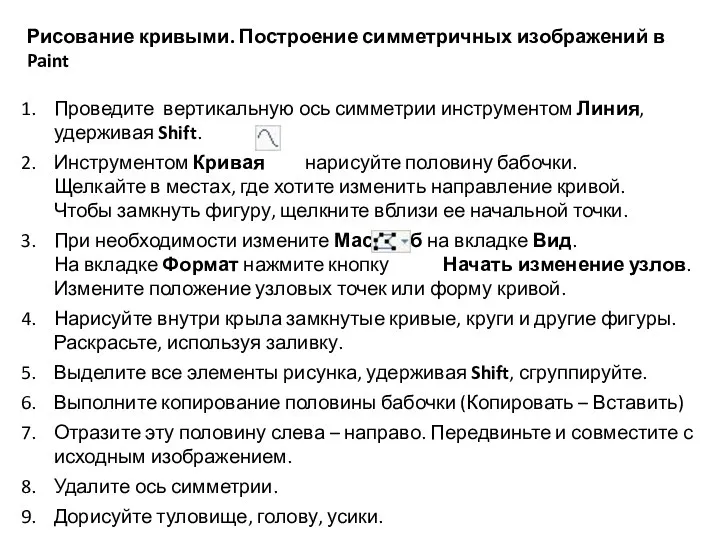

Construction and optimization of algorithms Построение симметричных изображений в Paint

Построение симметричных изображений в Paint Методическая разработка по информатике и ИКТ на тему Форматирование абзацев и стили форматирования в Microsoft Office Word

Методическая разработка по информатике и ИКТ на тему Форматирование абзацев и стили форматирования в Microsoft Office Word Адреса и серверы электронной почты (E-mail addresses and servers)

Адреса и серверы электронной почты (E-mail addresses and servers) Базы данных. Теоретические основы

Базы данных. Теоретические основы Гиперссылки. Фреймы в HTML документе

Гиперссылки. Фреймы в HTML документе Презентация Представление числовой информации с помощью систем счисления

Презентация Представление числовой информации с помощью систем счисления Выполнение программы

Выполнение программы Разработка системы обеспечения безопасности данных корпоративной сети организации

Разработка системы обеспечения безопасности данных корпоративной сети организации Информационные технологии

Информационные технологии Представление информации в форме 5 класс

Представление информации в форме 5 класс Cover title. Cover subtitile

Cover title. Cover subtitile Презентация Симметрия фигур к уроку информатики в 1 классе.

Презентация Симметрия фигур к уроку информатики в 1 классе. Mass media and media literacy

Mass media and media literacy