Параллельное программирование для ресурсоёмких задач численного моделирования в физике. Лекция 2 презентация

Содержание

- 2. Физический факультет МГУ им М.В.Ломоносова Лекция № 2

- 3. Физический факультет МГУ им М.В.Ломоносова Содержание лекции Структуры аппаратного обеспечения Принципы построения мультипроцессорных систем Многообразие архитектур

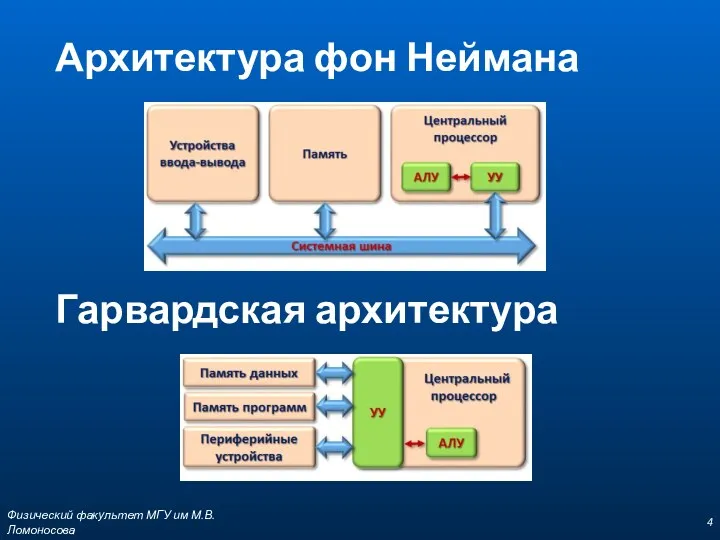

- 4. Физический факультет МГУ им М.В.Ломоносова Архитектура фон Неймана Гарвардская архитектура

- 5. Физический факультет МГУ им М.В.Ломоносова Основные архитектуры процессоров CISC (Complex Instruction Set Computing) Нефиксированным значением длины

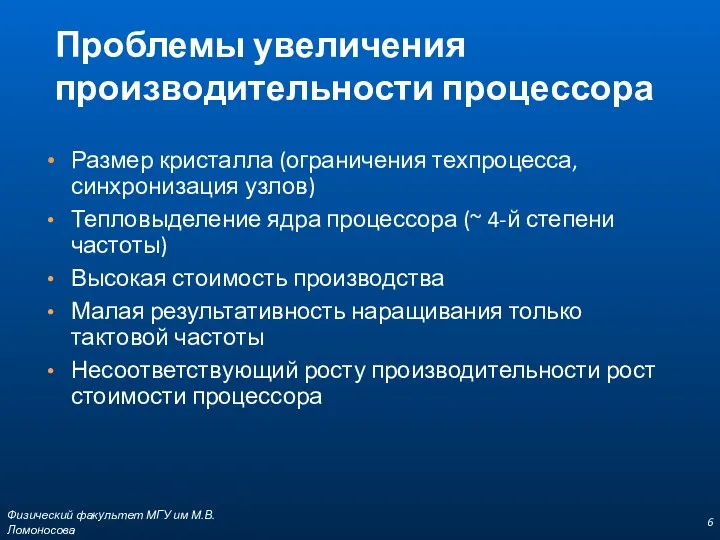

- 6. Физический факультет МГУ им М.В.Ломоносова Проблемы увеличения производительности процессора Размер кристалла (ограничения техпроцесса, синхронизация узлов) Тепловыделение

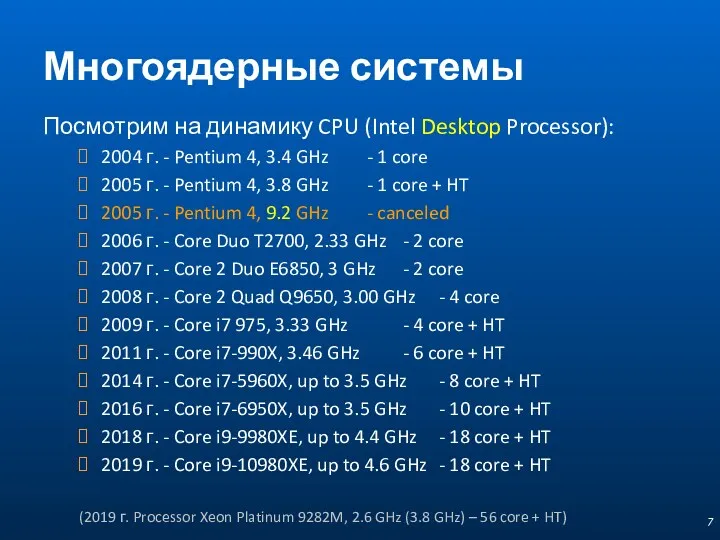

- 7. Многоядерные системы Посмотрим на динамику CPU (Intel Desktop Processor): 2004 г. - Pentium 4, 3.4 GHz

- 8. Повышение быстродействия Параллельность Конвейер Multithreading SIMD/Векторизация (SSE / AVX …)

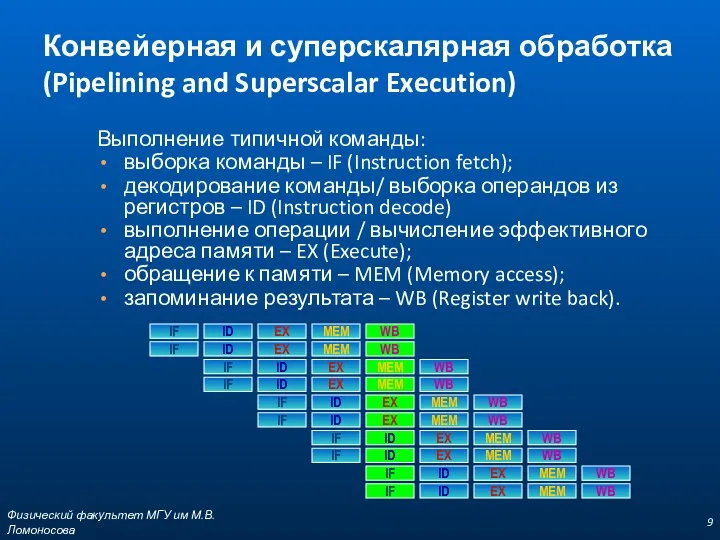

- 9. Физический факультет МГУ им М.В.Ломоносова Выполнение типичной команды: выборка команды – IF (Instruction fetch); декодирование команды/

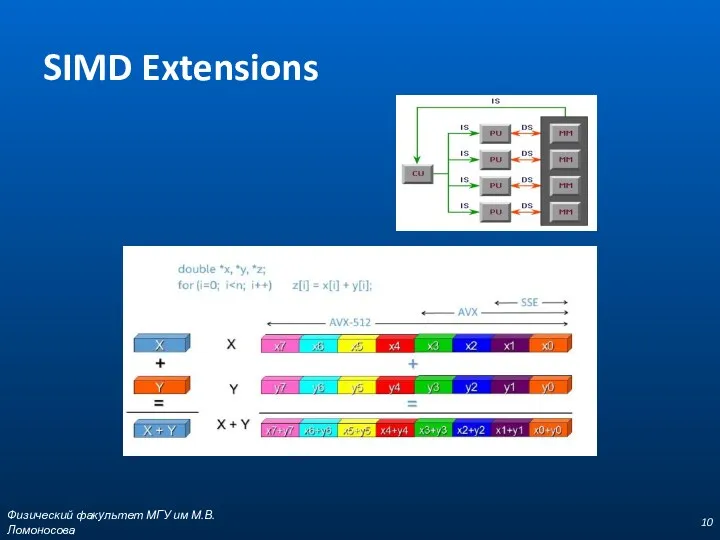

- 10. SIMD Extensions Физический факультет МГУ им М.В.Ломоносова

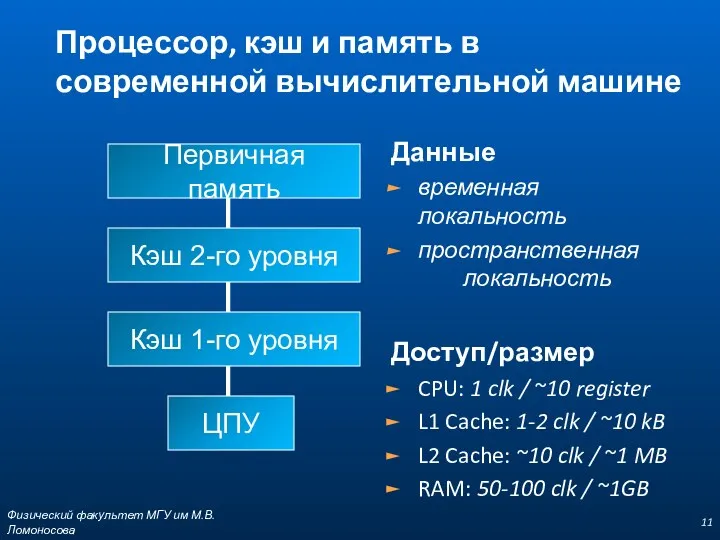

- 11. Физический факультет МГУ им М.В.Ломоносова Процессор, кэш и память в современной вычислительной машине Первичная память Кэш

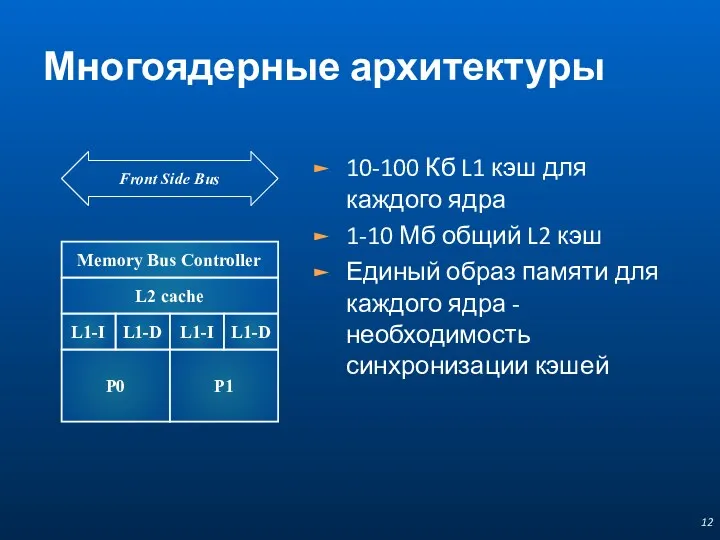

- 12. Многоядерные архитектуры 10-100 Кб L1 кэш для каждого ядра 1-10 Мб общий L2 кэш Единый образ

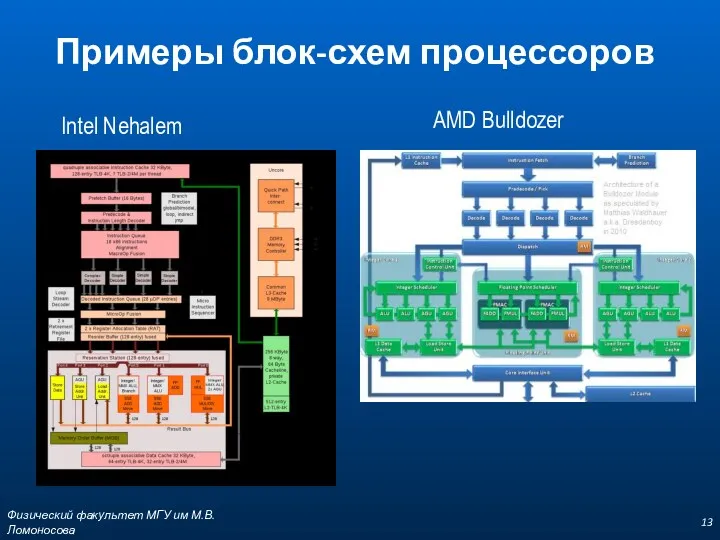

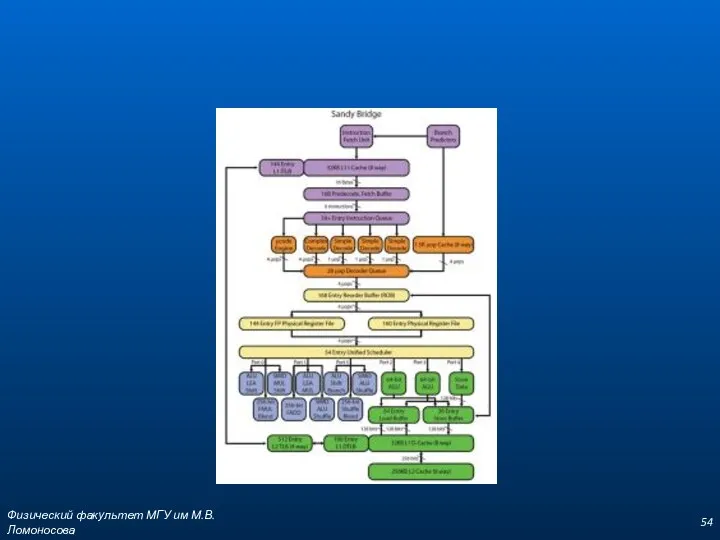

- 13. Физический факультет МГУ им М.В.Ломоносова Примеры блок-схем процессоров Intel Nehalem AMD Bulldozer

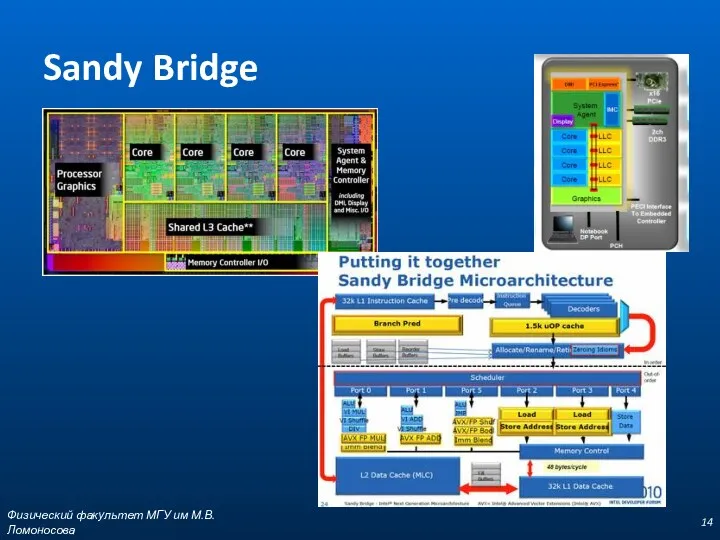

- 14. Sandy Bridge Физический факультет МГУ им М.В.Ломоносова

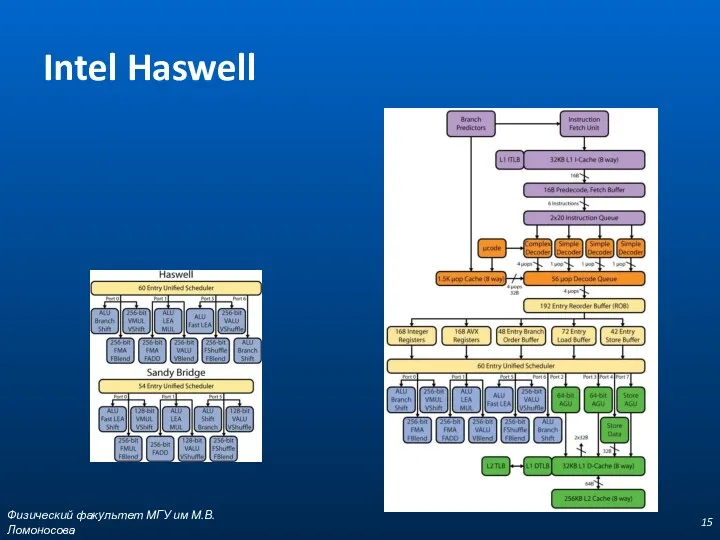

- 15. Intel Haswell Физический факультет МГУ им М.В.Ломоносова

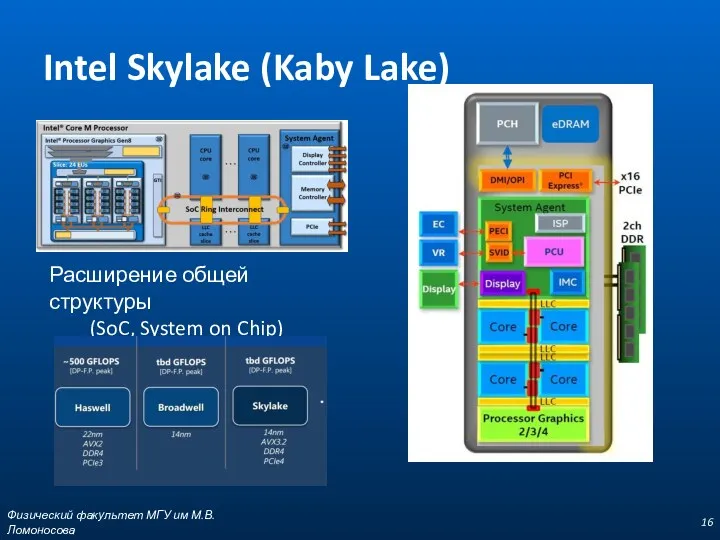

- 16. Intel Skylake (Kaby Lake) Физический факультет МГУ им М.В.Ломоносова Расширение общей структуры (SoC, System on Chip)

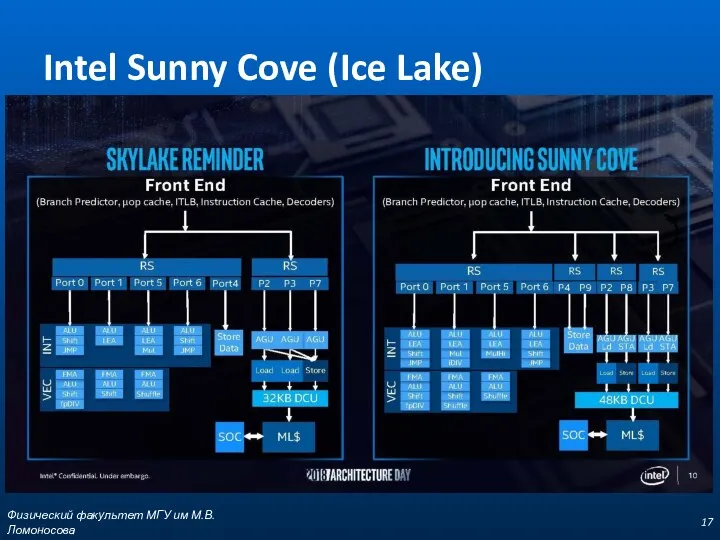

- 17. Intel Sunny Cove (Ice Lake) Физический факультет МГУ им М.В.Ломоносова

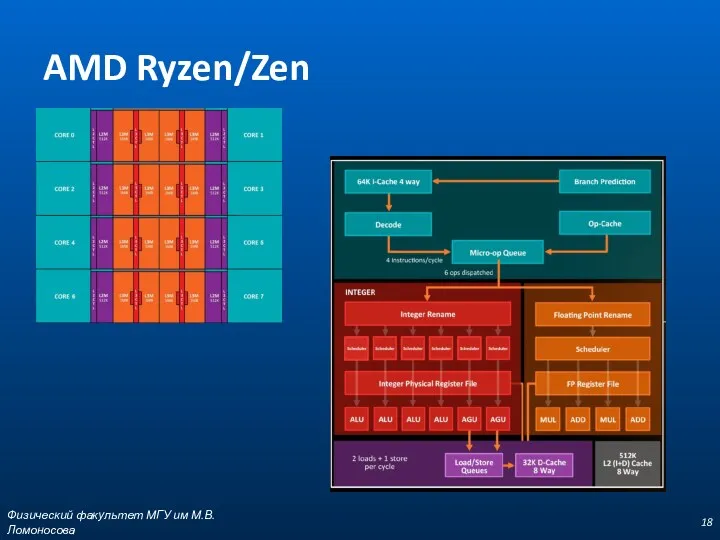

- 18. AMD Ryzen/Zen Физический факультет МГУ им М.В.Ломоносова

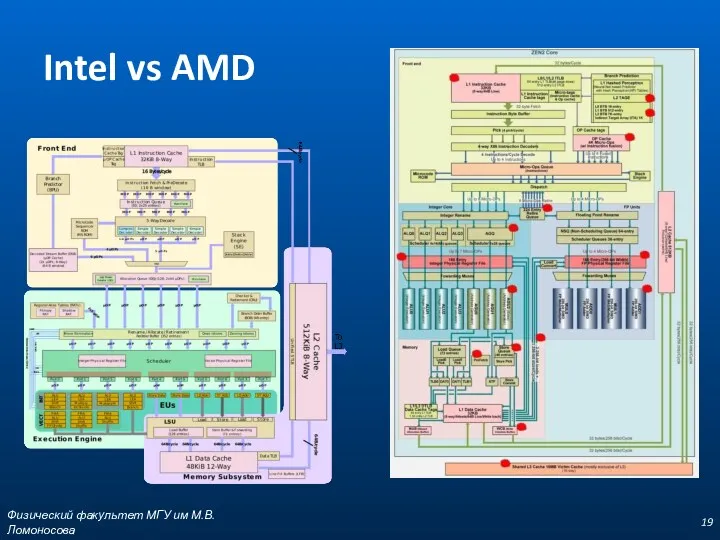

- 19. Intel vs AMD Физический факультет МГУ им М.В.Ломоносова

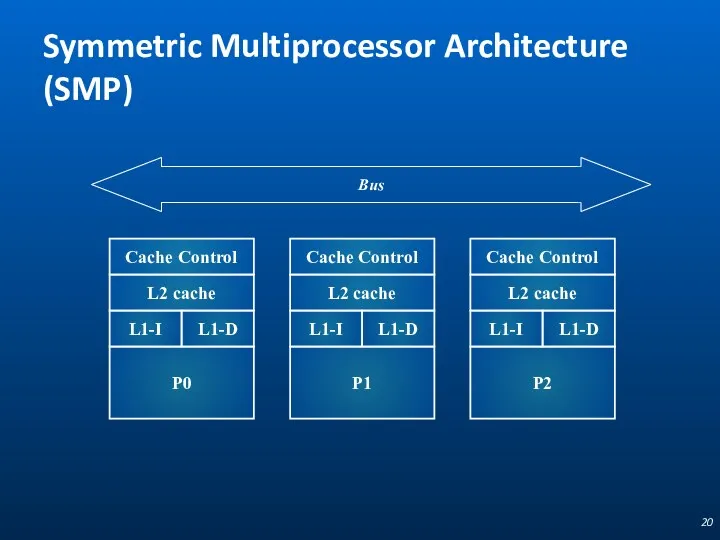

- 20. Symmetric Multiprocessor Architecture (SMP) Cache Control L2 cache L1-I L1-D P0 Bus Cache Control L2 cache

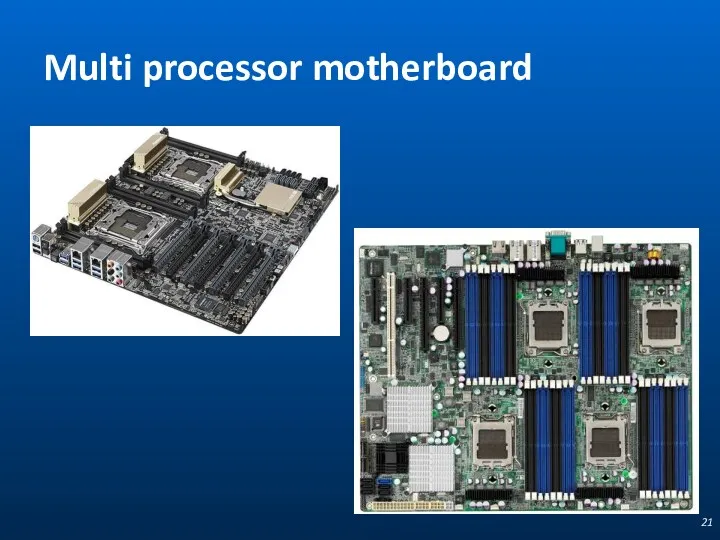

- 21. Multi processor motherboard

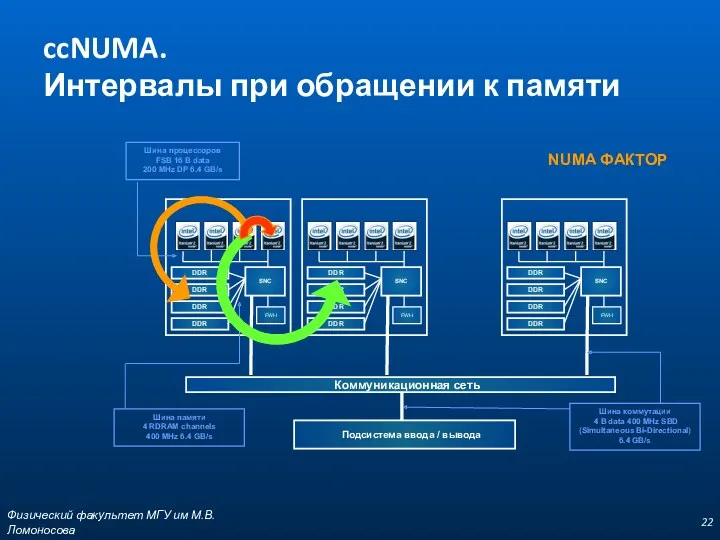

- 22. Физический факультет МГУ им М.В.Ломоносова ccNUMA. Интервалы при обращении к памяти NUMA ФАКТОР Коммуникационная сеть Подсистема

- 23. Физический факультет МГУ им М.В.Ломоносова

- 24. Многообразие архитектур ЭВМ Физический факультет МГУ им М.В.Ломоносова

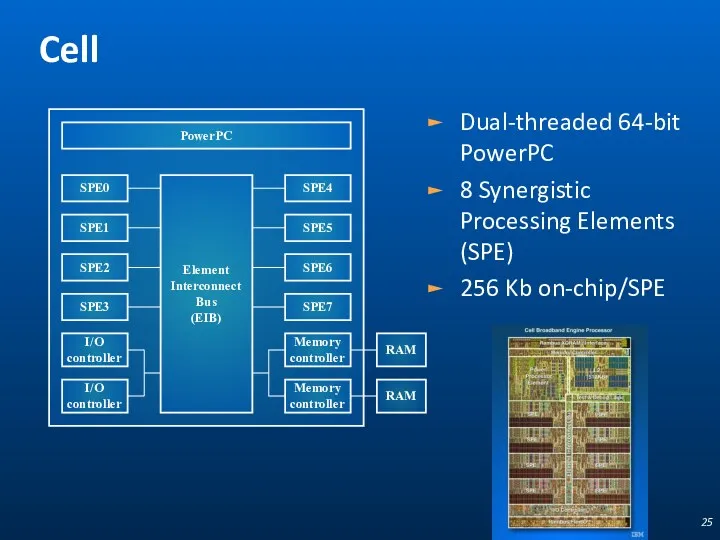

- 25. Cell Dual-threaded 64-bit PowerPC 8 Synergistic Processing Elements (SPE) 256 Kb on-chip/SPE SPE0 PowerPC SPE4 Element

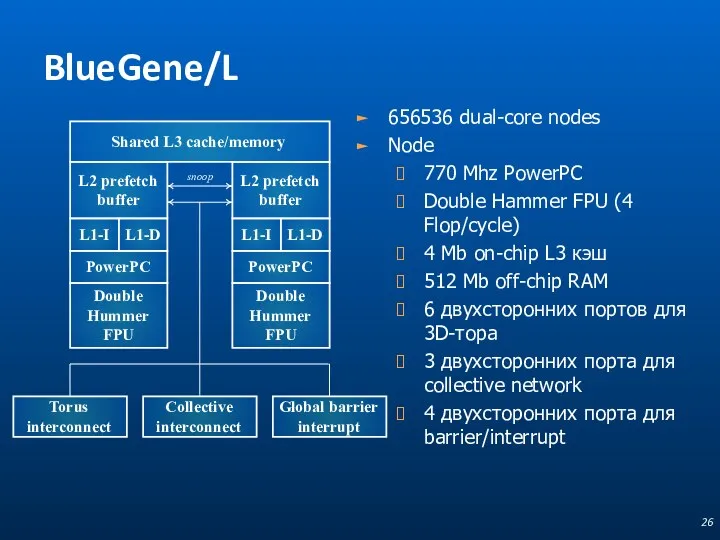

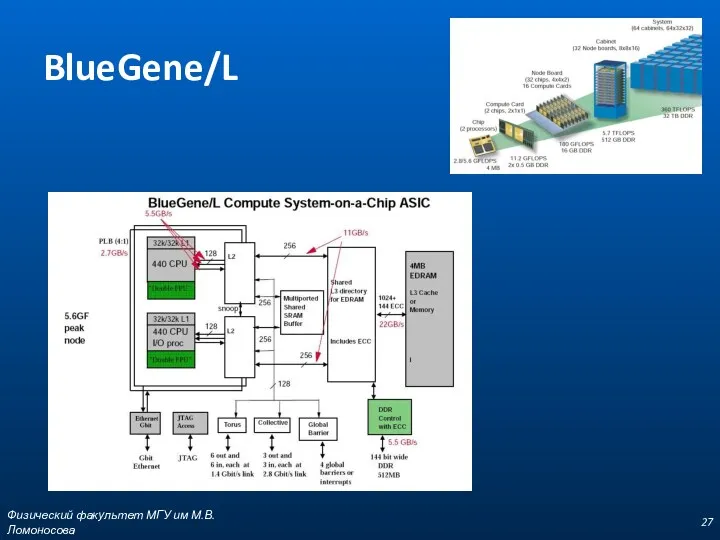

- 26. BlueGene/L 656536 dual-core nodes Node 770 Mhz PowerPC Double Hammer FPU (4 Flop/cycle) 4 Mb on-chip

- 27. BlueGene/L Физический факультет МГУ им М.В.Ломоносова

- 28. Архитектура G80 Массив из потоковых мультипроцессоров Streaming Multiprocessor (SM) Streaming Multiprocessor (SM) Streaming Multiprocessor (SM) Streaming

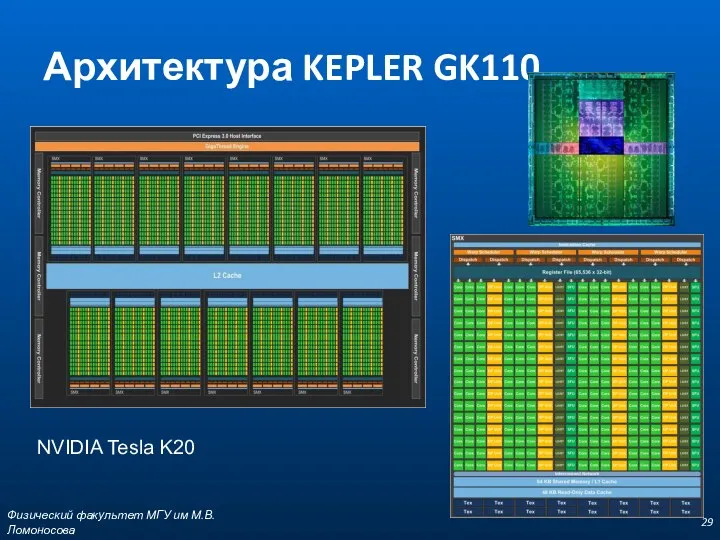

- 29. Архитектура KEPLER GK110 Физический факультет МГУ им М.В.Ломоносова NVIDIA Tesla K20

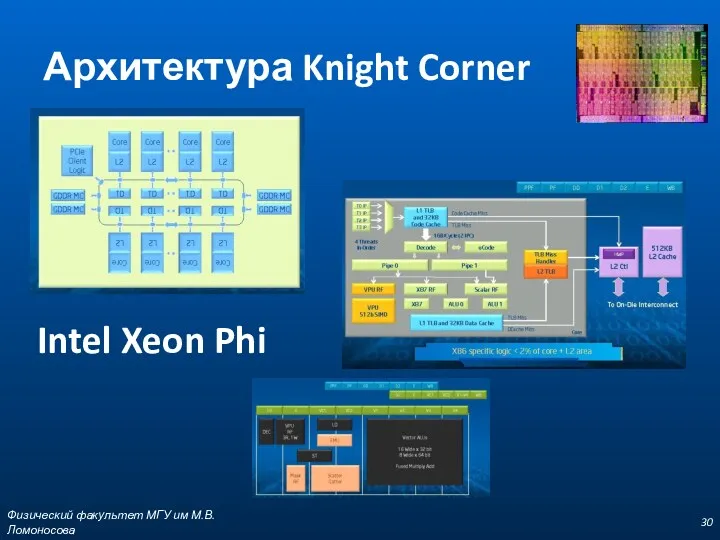

- 30. Архитектура Knight Corner Физический факультет МГУ им М.В.Ломоносова Intel Xeon Phi

- 31. Компьютерная/системная шина computer bus Физический факультет МГУ им М.В.Ломоносова

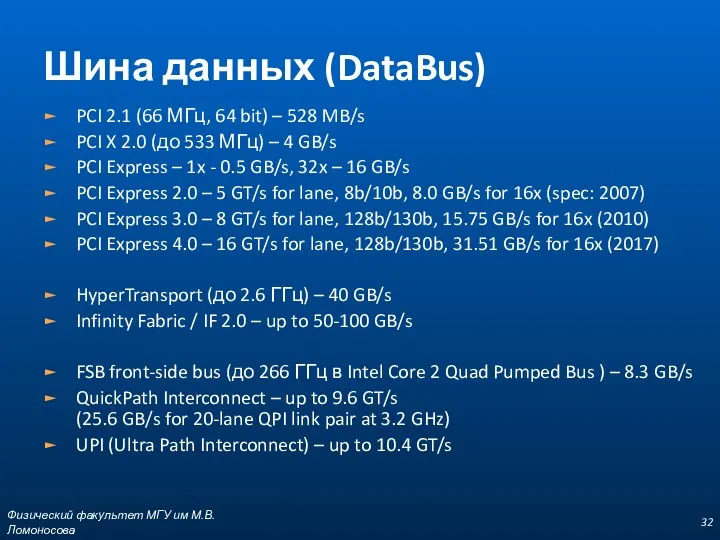

- 32. Физический факультет МГУ им М.В.Ломоносова Шина данных (DataBus) PCI 2.1 (66 МГц, 64 bit) – 528

- 33. Пропускная способность и латентность Физический факультет МГУ им М.В.Ломоносова

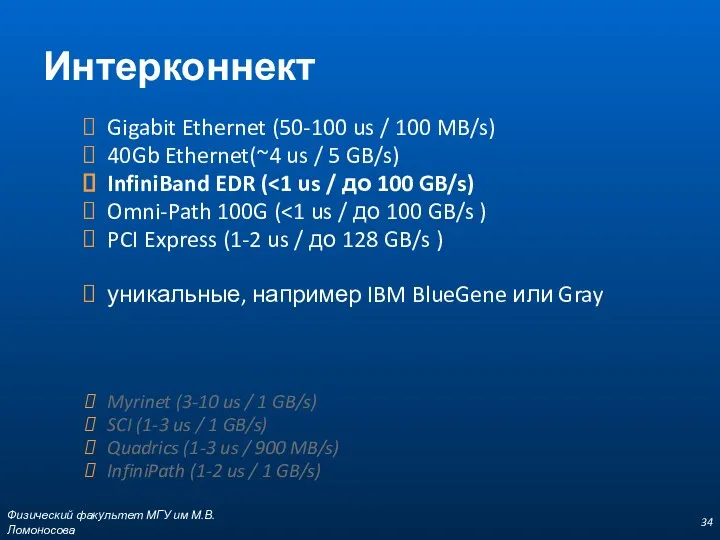

- 34. Физический факультет МГУ им М.В.Ломоносова Интерконнект Gigabit Ethernet (50-100 us / 100 MB/s) 40Gb Ethernet(~4 us

- 35. Использование в top500 Физический факультет МГУ им М.В.Ломоносова

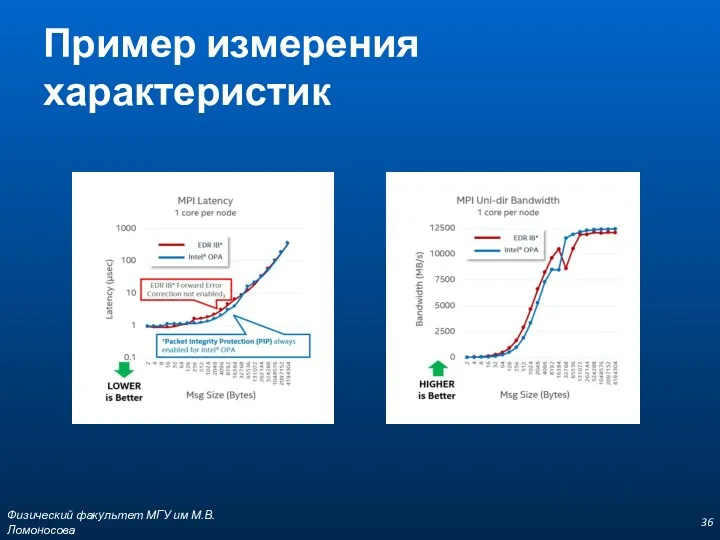

- 36. Пример измерения характеристик Физический факультет МГУ им М.В.Ломоносова

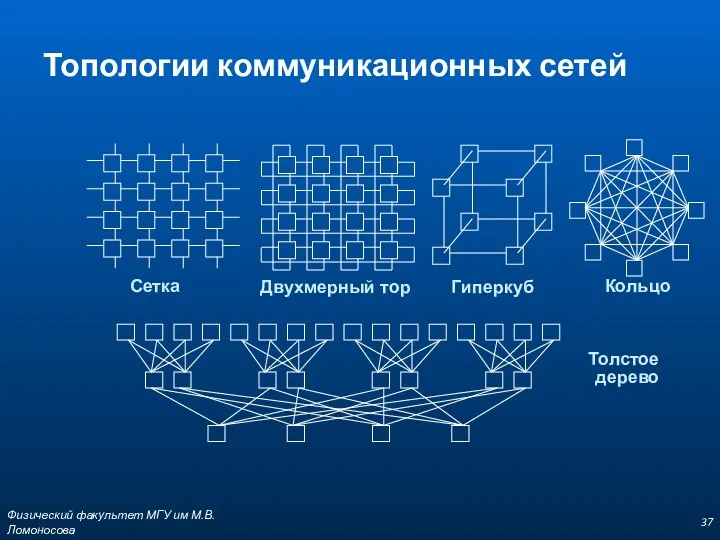

- 37. Физический факультет МГУ им М.В.Ломоносова Топологии коммуникационных сетей Толстое дерево Сетка Гиперкуб Кольцо

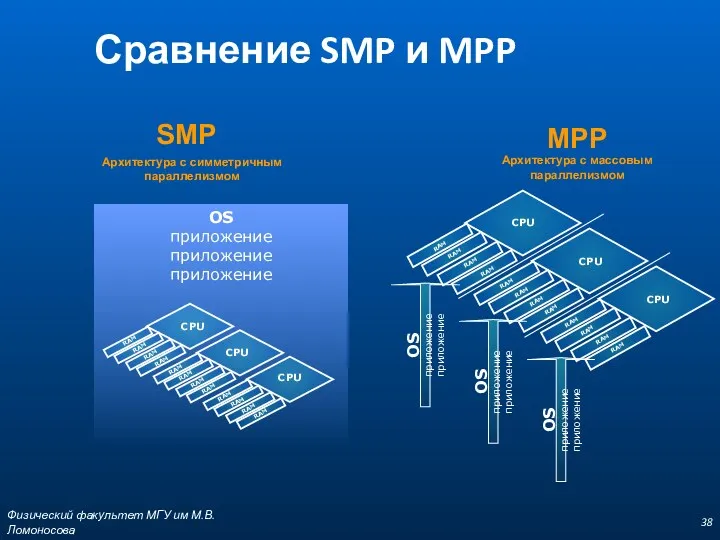

- 38. Физический факультет МГУ им М.В.Ломоносова Сравнение SMP и MPP

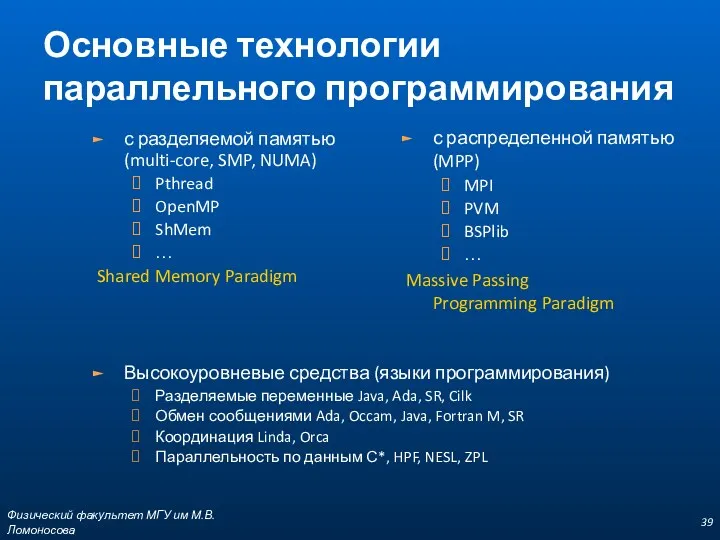

- 39. Физический факультет МГУ им М.В.Ломоносова Основные технологии параллельного программирования с разделяемой памятью (multi-core, SMP, NUMA) Pthread

- 40. Физический факультет МГУ им М.В.Ломоносова Определения Один из первых архитекторов кластерной технологии Грегори Пфистер дал кластеру

- 41. Физический факультет МГУ им М.В.Ломоносова Beowulf Кластер, который состоит из широко распространённого аппаратного обеспечения, работающий под

- 42. Физический факультет МГУ им М.В.Ломоносова Преимущества Beowulf-систем стоимость системы гораздо ниже стоимости суперкомпьютера; возможность увеличения производительности

- 43. Физический факультет МГУ им М.В.Ломоносова Вычислительный кластер IBM eServer 345 -1 IBM eServer 335 -6 HP

- 44. Физический факультет МГУ им М.В.Ломоносова Топология сети …………………… internet compute-0-0 compute-0-1 compute-0-5 frontend switch IB-switch

- 45. Физический факультет МГУ им М.В.Ломоносова Организация кластера

- 46. OpenMP Server openSUSE Intel Xeon X5660 @ 2.80GHz (8 core available) Терминальный Linux сервер (SSH) Компилятор

- 47. Суперкомпьютер "Ломоносов" http://parallel.ru/cluster/lomonosov.html Физический факультет МГУ им М.В.Ломоносова

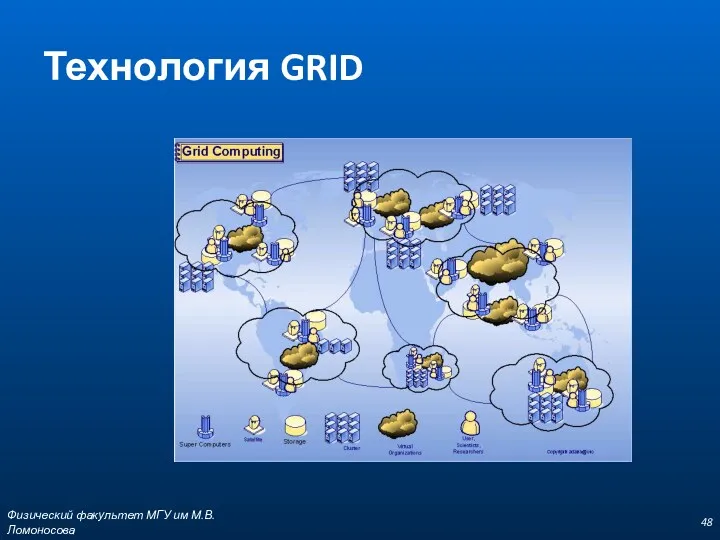

- 48. Физический факультет МГУ им М.В.Ломоносова Технология GRID

- 49. Физический факультет МГУ им М.В.Ломоносова

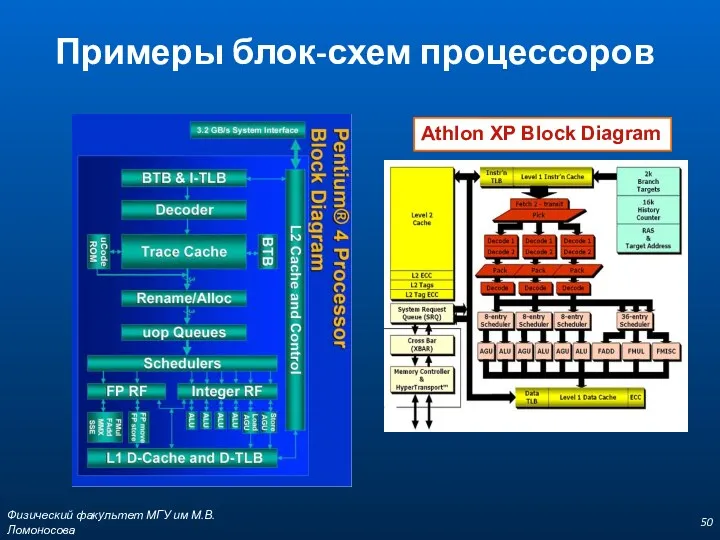

- 50. Физический факультет МГУ им М.В.Ломоносова Примеры блок-схем процессоров Athlon XP Block Diagram

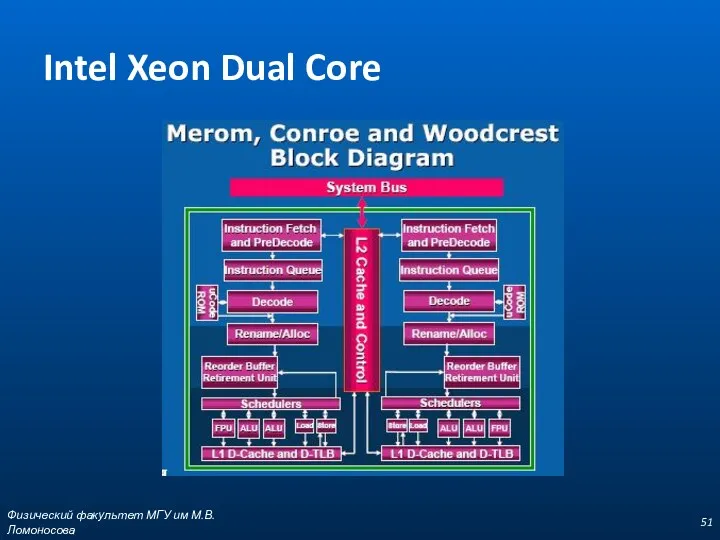

- 51. Физический факультет МГУ им М.В.Ломоносова Intel Xeon Dual Core

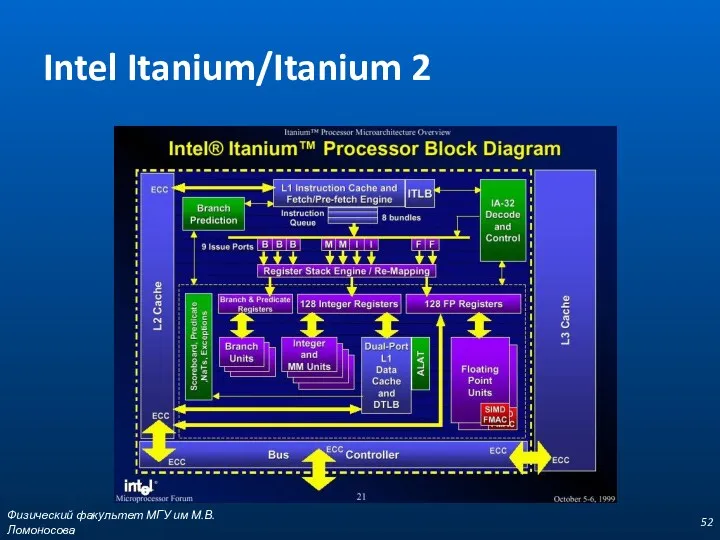

- 52. Физический факультет МГУ им М.В.Ломоносова Intel Itanium/Itanium 2

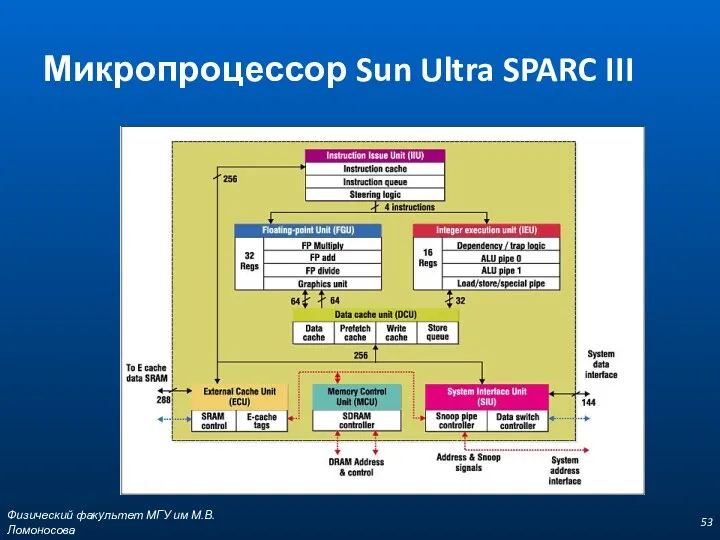

- 53. Физический факультет МГУ им М.В.Ломоносова Микропроцессор Sun Ultra SPARC III

- 54. Физический факультет МГУ им М.В.Ломоносова

- 56. Скачать презентацию

Создание приложения, используя Spring Framework. Java. (Лекция 23)

Создание приложения, используя Spring Framework. Java. (Лекция 23) Программирование игр на C# в среде Unity

Программирование игр на C# в среде Unity Алгоритм создания рабочей программы

Алгоритм создания рабочей программы Журналистика: что это такое и зачем она нужна

Журналистика: что это такое и зачем она нужна Что такое программное обеспечение. (10 класс)

Что такое программное обеспечение. (10 класс) Графика MS WORD редакторында

Графика MS WORD редакторында Веб-сериал

Веб-сериал Minta. Presentation template

Minta. Presentation template 1С:Архив. Решение для долговременного хранения документов

1С:Архив. Решение для долговременного хранения документов Журналистика деген не?

Журналистика деген не? Системы Электронного Документооборота. Лекция 2

Системы Электронного Документооборота. Лекция 2 Защита компьютерной информации

Защита компьютерной информации 1. Обработка символьной информации. Символьные переменные

1. Обработка символьной информации. Символьные переменные Запросы СУБД Microsoft Access

Запросы СУБД Microsoft Access Библиографическое описание разных видов документов

Библиографическое описание разных видов документов Розрахунок показників надійності по специфічним даним. ЛР №3

Розрахунок показників надійності по специфічним даним. ЛР №3 Взаємодія з користувачем та оператори умови JavaScript

Взаємодія з користувачем та оператори умови JavaScript Логические основы ЭВМ

Логические основы ЭВМ Защищенные компьютерные технологии: миф или реальность?

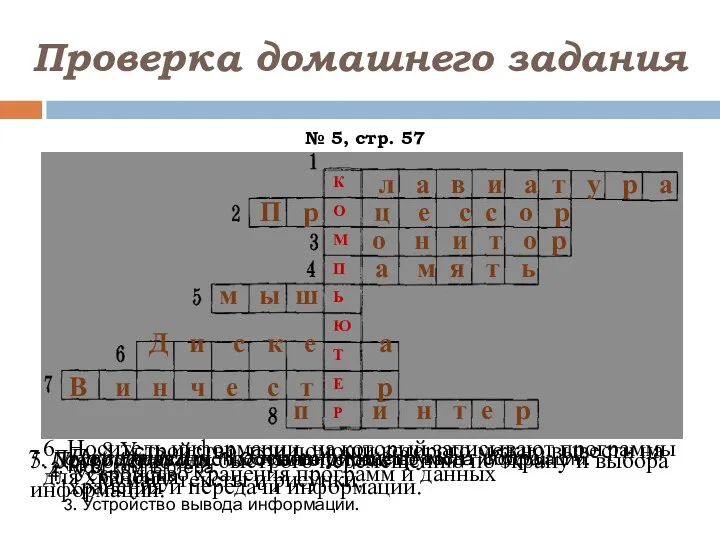

Защищенные компьютерные технологии: миф или реальность? Материал к уроку информатики в 5 классе: Управление компьютером с помощью мыши

Материал к уроку информатики в 5 классе: Управление компьютером с помощью мыши Технологии физического уровня передачи данных. Компьютерные сети

Технологии физического уровня передачи данных. Компьютерные сети Електронна пошта

Електронна пошта Программирование циклических алгоритмов. Операции с памятью. Обработка структур данных (массивов)

Программирование циклических алгоритмов. Операции с памятью. Обработка структур данных (массивов) Графика в Pascal ABC.NET

Графика в Pascal ABC.NET Розничные продажи в 1С

Розничные продажи в 1С Social Networks

Social Networks Принципы автоматизированного управления тепловыми пунктами

Принципы автоматизированного управления тепловыми пунктами Основы программной инженерии

Основы программной инженерии