Содержание

- 2. Содержание Основные понятия Полусумматор Сумматор Построение схемы последовательного сумматора Работа сумматора

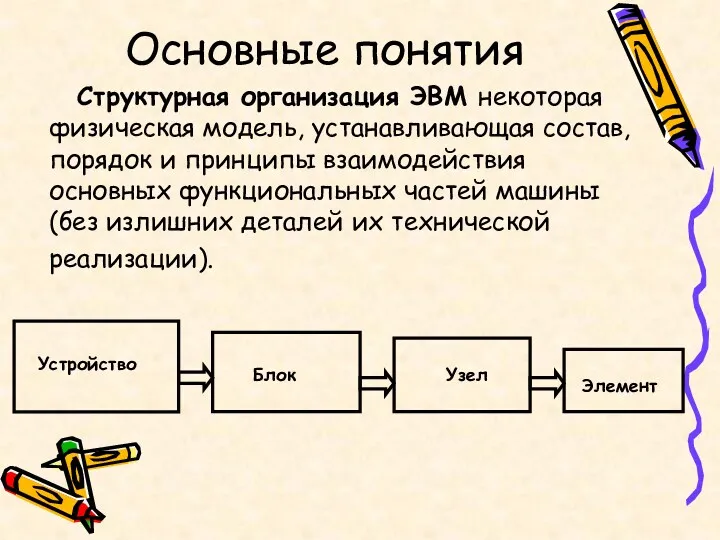

- 3. Основные понятия Структурная организация ЭВМ некоторая физическая модель, устанавливающая состав, порядок и принципы взаимодействия основных функциональных

- 4. Элемент, простейшее устройство ЭВМ, выполняющее одну операцию над входными сигналами (пример – логический элемент).

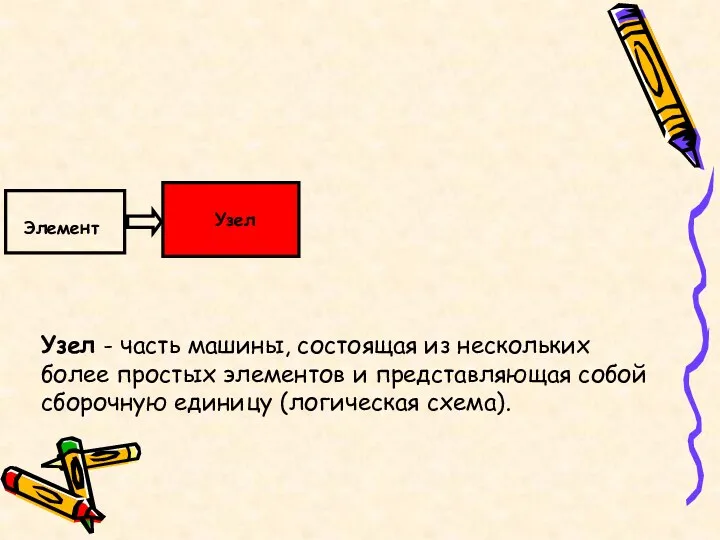

- 5. Узел - часть машины, состоящая из нескольких более простых элементов и представляющая собой сборочную единицу (логическая

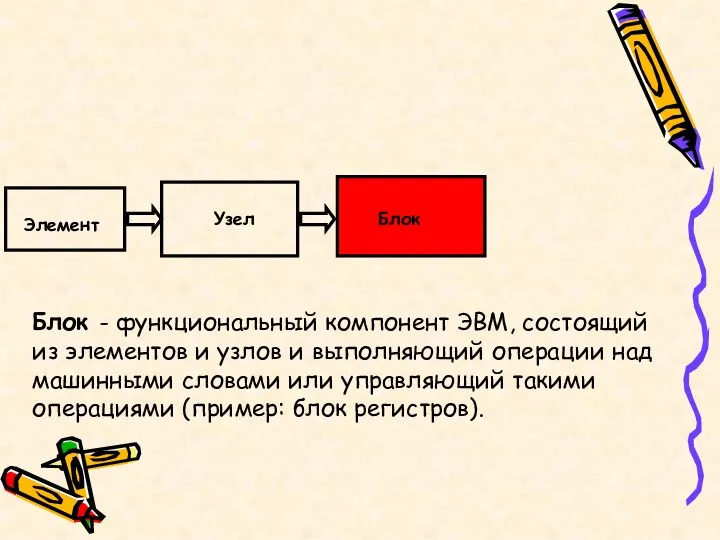

- 6. Блок - функциональный компонент ЭВМ, состоящий из элементов и узлов и выполняющий операции над машинными словами

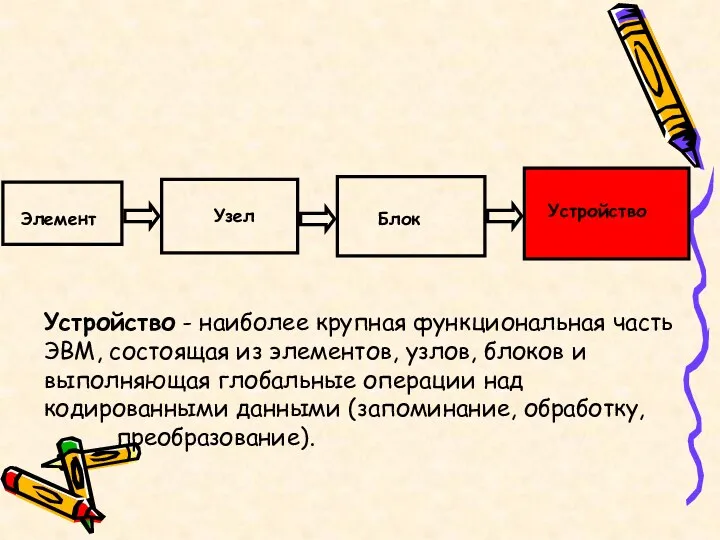

- 7. Устройство - наиболее крупная функциональная часть ЭВМ, состоящая из элементов, узлов, блоков и выполняющая глобальные операции

- 8. Узел ЭВМ выполняющий арифметическое суммирование кодов чисел, называется сумматором.

- 9. Операция суммирования осуществляется в сумматорах поразрядно с использованием одноразрядных суммирующих схем. При этом в каждом разряде

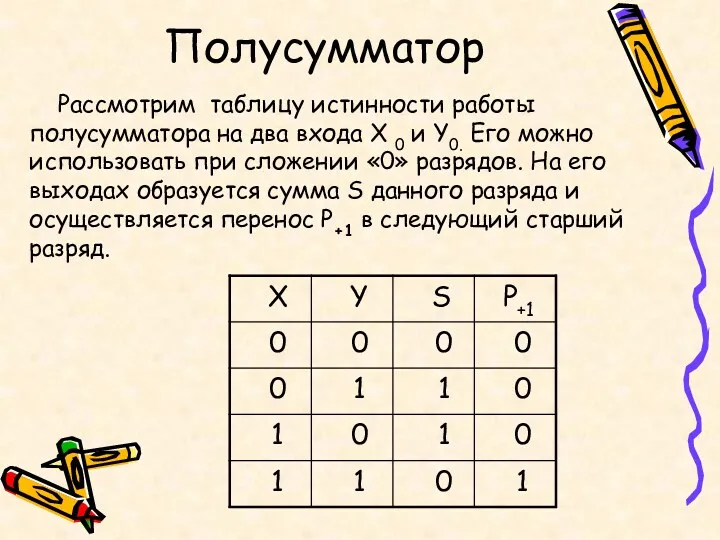

- 10. Полусумматор Рассмотрим таблицу истинности работы полусумматора на два входа X 0 и Y0. Его можно использовать

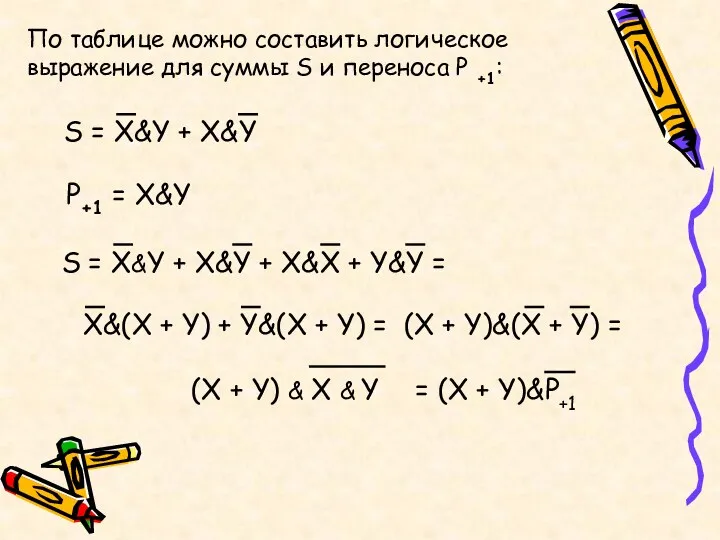

- 11. По таблице можно составить логическое выражение для суммы S и переноса Р +1: P+1 = X&Y

- 12. Структурная схема полусумматора

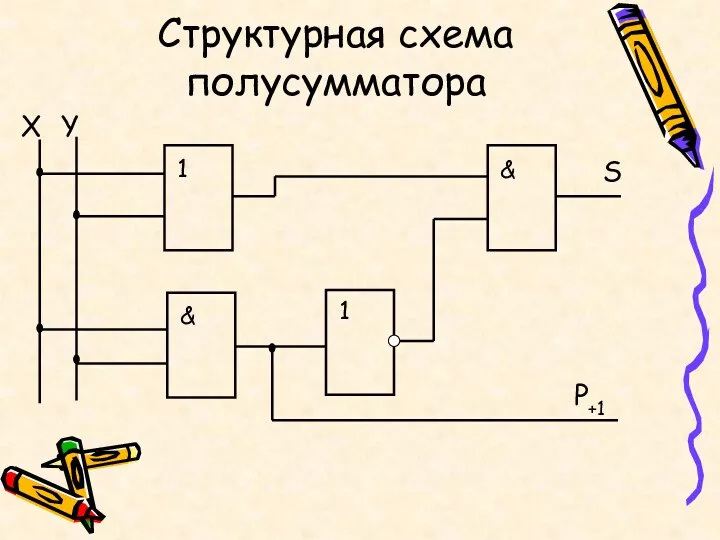

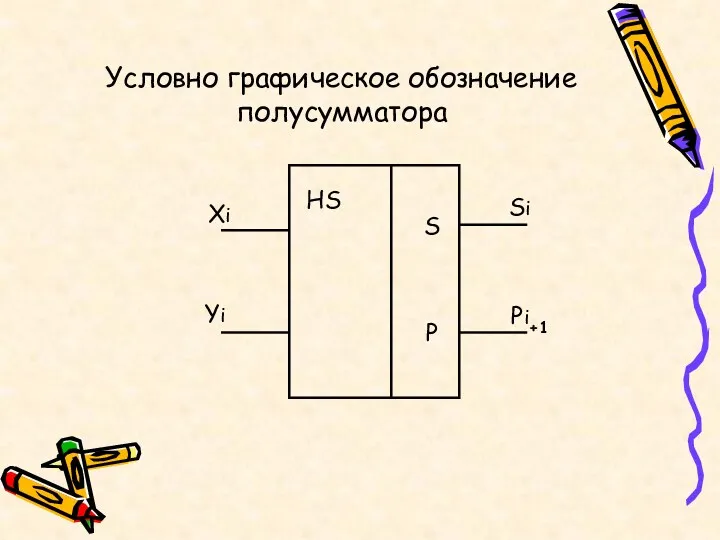

- 13. Условно графическое обозначение полусумматора HS S P Xi Yi Si Pi+1

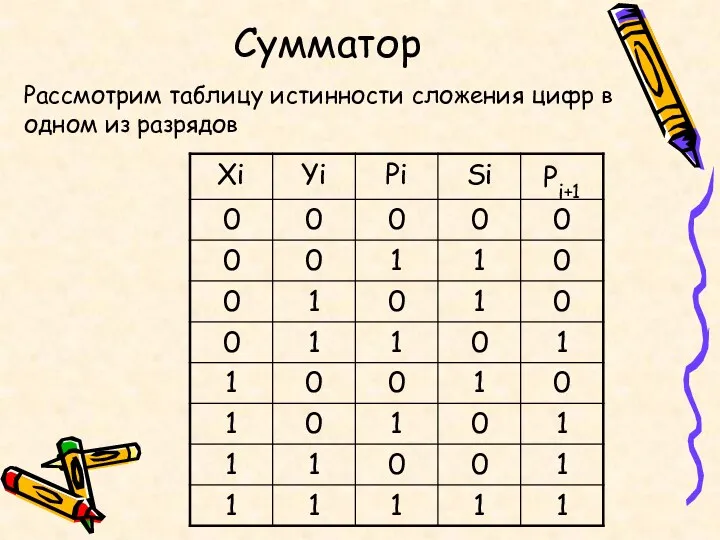

- 14. Сумматор Рассмотрим таблицу истинности сложения цифр в одном из разрядов

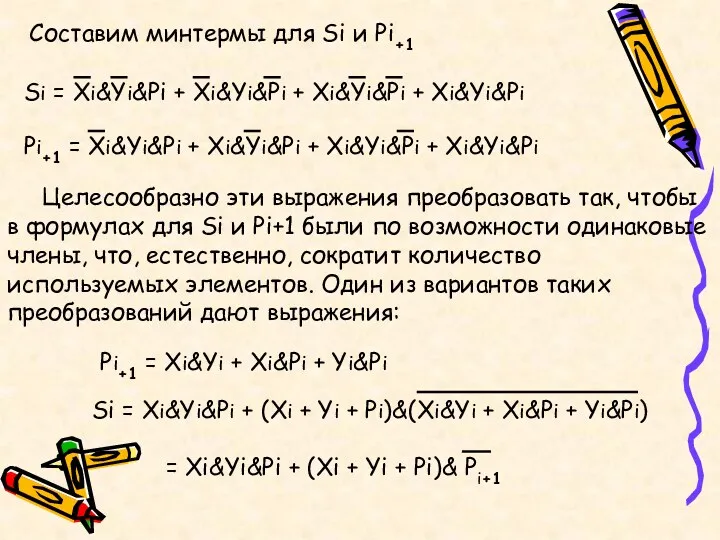

- 15. Составим минтермы для Si и Pi+1 Целесообразно эти выражения преобразовать так, чтобы в формулах для Si

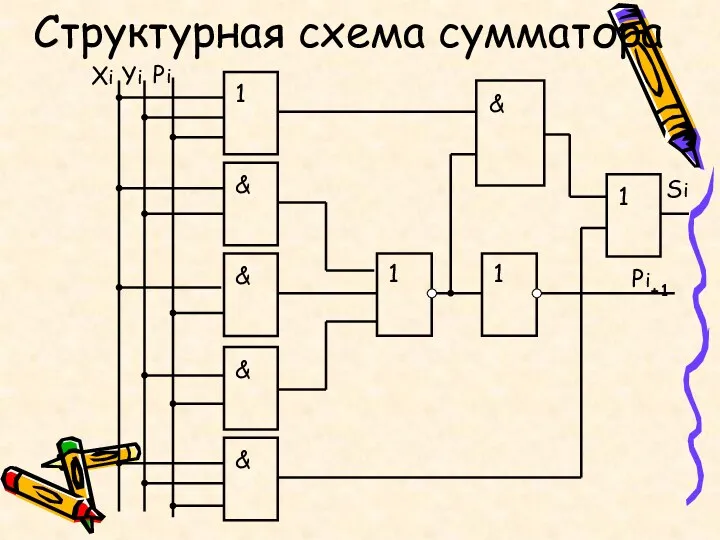

- 16. Структурная схема сумматора

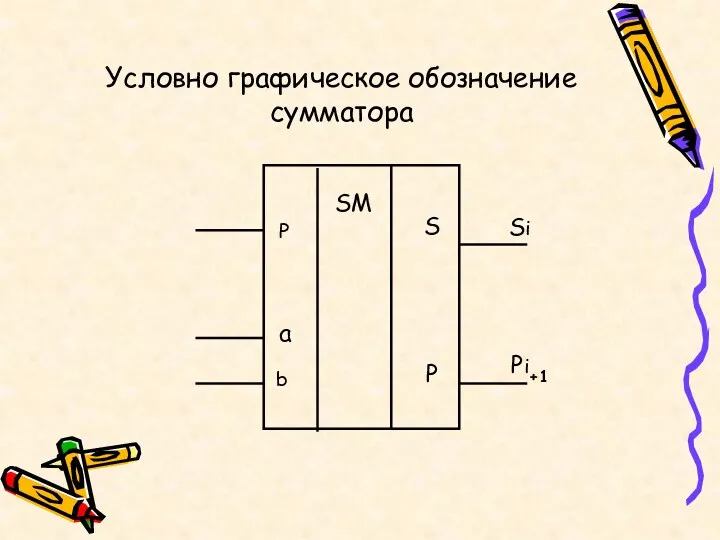

- 17. SM S P Si Pi+1 a b P Условно графическое обозначение сумматора

- 18. Для сложения двух N-разрядных двоичных кодов, используется схема многоразрядного сумматора.

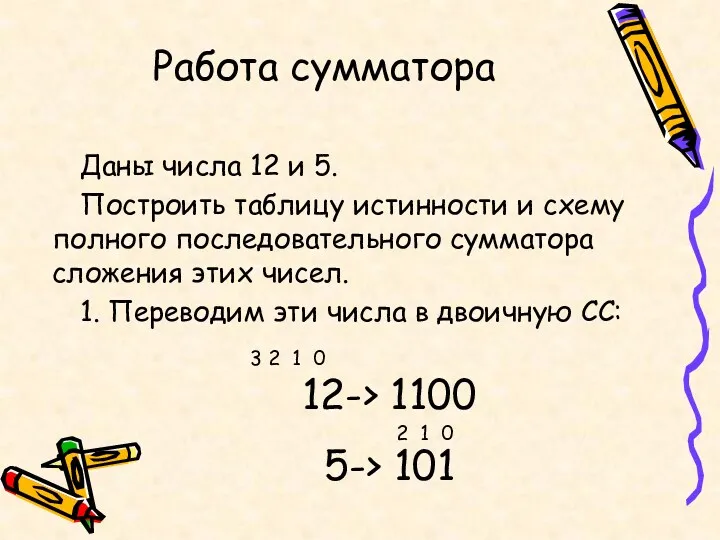

- 19. Работа сумматора Даны числа 12 и 5. Построить таблицу истинности и схему полного последовательного сумматора сложения

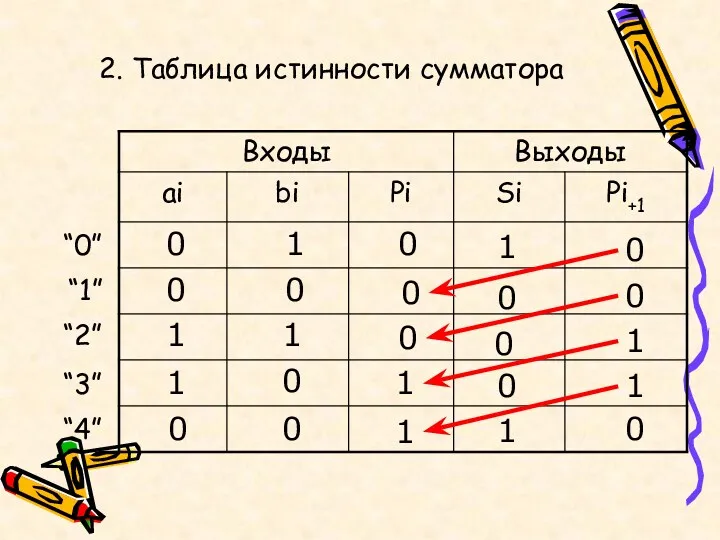

- 20. 2. Таблица истинности сумматора 0 1 1 0 0 0 0 0 0 0 1 1

- 21. Структурная схема сумматора 0

- 23. Скачать презентацию

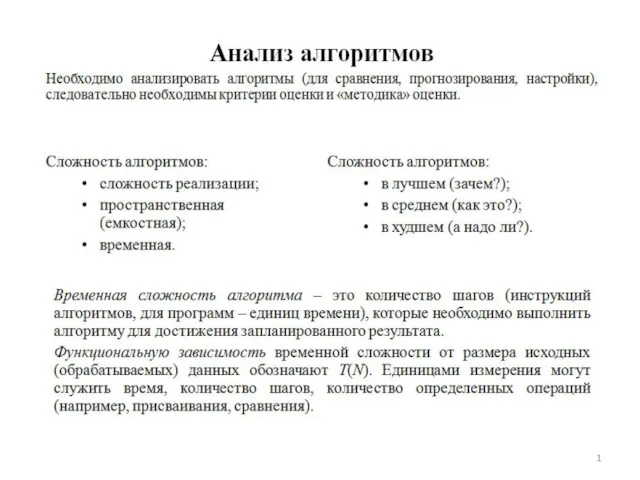

Анализ алгоритмов

Анализ алгоритмов Урок по созданию диаграмм в Excel для финансовых отчетов

Урок по созданию диаграмм в Excel для финансовых отчетов Интернет-этикет сетикет или по-другому нетикет

Интернет-этикет сетикет или по-другому нетикет Как вести себя в Интернете? Безопасность в сети Интернет

Как вести себя в Интернете? Безопасность в сети Интернет Алгоритм и исполнители

Алгоритм и исполнители Общие сведения о языке программирования Паскаль. Начала программирования. Информатика. 8 класс

Общие сведения о языке программирования Паскаль. Начала программирования. Информатика. 8 класс Электронные таблицы. MS Excel

Электронные таблицы. MS Excel Контент-анализ как количественный метод исследования текстов

Контент-анализ как количественный метод исследования текстов Лекция 2016.3. Построение конфигурации. Дерево конфигурации

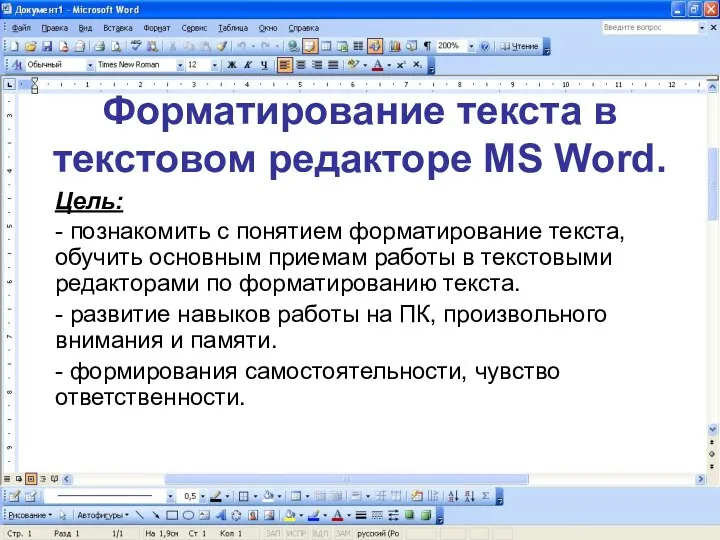

Лекция 2016.3. Построение конфигурации. Дерево конфигурации Форматирование текста в текстовом редакторе MS Word

Форматирование текста в текстовом редакторе MS Word Приложения по информатике

Приложения по информатике Обратное распространение ошибки. Практика

Обратное распространение ошибки. Практика Цикл с параметром

Цикл с параметром Назначение и возможности табличного процессора MS Excel

Назначение и возможности табличного процессора MS Excel Носії інформації

Носії інформації Виртуальные машины и их операционные системы

Виртуальные машины и их операционные системы Протоколы IPTV

Протоколы IPTV Создание веб-страниц в WORD. Проектирование веб-сайта

Создание веб-страниц в WORD. Проектирование веб-сайта История развития ООП. Базовые понятия ООП: объект, его свойства и методы, класс, интерфейс

История развития ООП. Базовые понятия ООП: объект, его свойства и методы, класс, интерфейс Запись чисел в различных системах счисления

Запись чисел в различных системах счисления Создание структуры базы данных. Семинар 3. Лекция 1. Первое знакомство с базами данных

Создание структуры базы данных. Семинар 3. Лекция 1. Первое знакомство с базами данных Организация ввода и вывода данных. Начала программирования

Организация ввода и вывода данных. Начала программирования Рецензия - отзыв, разбор и оценка

Рецензия - отзыв, разбор и оценка Суммирование элементов массива, вычисления следа матрицы, суммирование двух массивов

Суммирование элементов массива, вычисления следа матрицы, суммирование двух массивов Современные системы автоматизации

Современные системы автоматизации Проектирование информационной системы учета услуг по монтажу и ремонту электрооборудования

Проектирование информационной системы учета услуг по монтажу и ремонту электрооборудования SOFiSTiK: Расчет монолитных железобетонных плит с учетом физической нелинейности 21.05.2013

SOFiSTiK: Расчет монолитных железобетонных плит с учетом физической нелинейности 21.05.2013 Лекция 8. Форматы графических файлов. Формат JPEG

Лекция 8. Форматы графических файлов. Формат JPEG