Аппаратная поддержка порядка операций обращения в память в системе на кристалле Эльбрус-2S презентация

Содержание

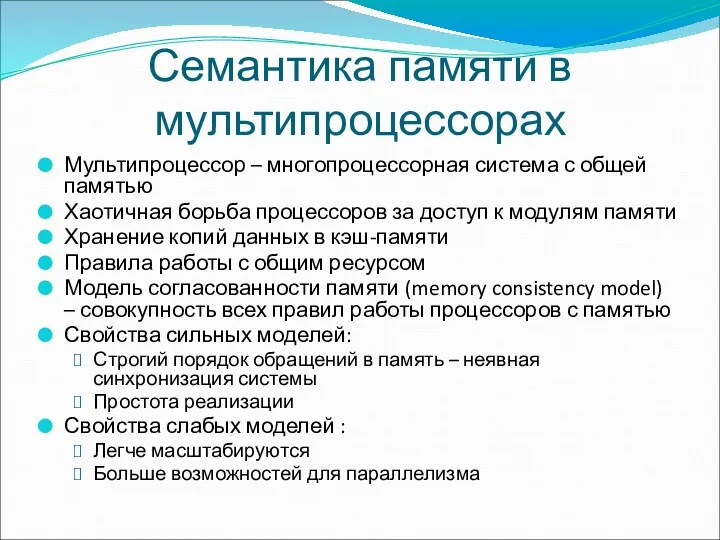

- 2. Семантика памяти в мультипроцессорах Мультипроцессор – многопроцессорная система с общей памятью Хаотичная борьба процессоров за доступ

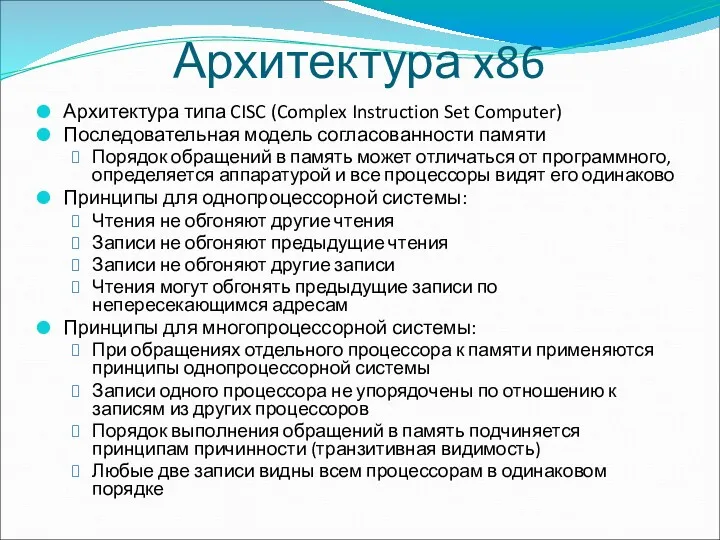

- 3. Архитектура x86 Архитектура типа CISC (Complex Instruction Set Computer) Последовательная модель согласованности памяти Порядок обращений в

- 4. Проблема совместимости с x86 Архитектура x86 – лидер на рынке продаж Написано огромное количество приложений под

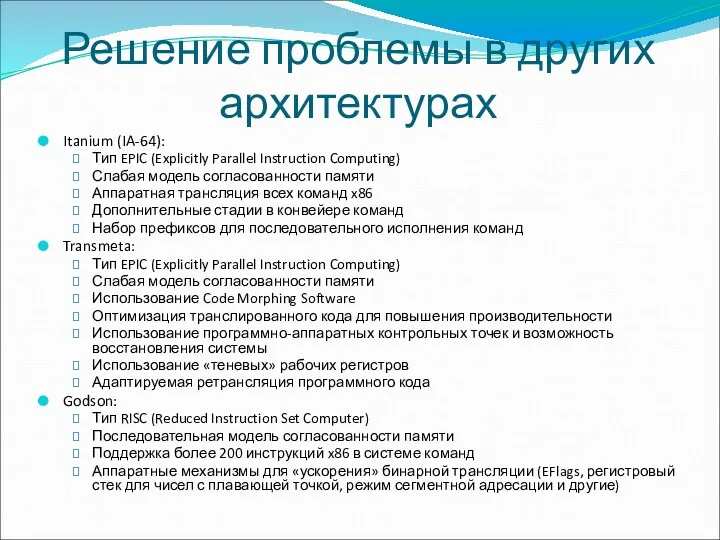

- 5. Решение проблемы в других архитектурах Itanium (IA-64): Тип EPIC (Explicitly Parallel Instruction Computing) Слабая модель согласованности

- 6. Место проблемы в архитектуре «Эльбрус» Тип VLIW (Very Long Instruction Word) Слабая модель согласованности памяти Статическое

- 7. Решение проблемы в проекте «Эльбрус-S» Реализация архитектуры «Эльбрус» в системе с четырьмя одноядерными процессорами Поддержка некоторых

- 8. Требования к проекту «Эльбрус-2S» Реализация архитектуры «Эльбрус» в системе с четырьмя процессорными узлами Каждый узел включает

- 9. Анализ задачи Основные аппаратные механизмы для совместимости с Intel x86 реализованы в проекте «Эльбрус-S» Для корректной

- 10. Принятое в проекте решение Поддержка порядка чтений Порядок чтений важен только тогда, когда считываемые переменные модифицируются

- 11. Принятое в проекте решение Положения неоптимизированного режима Упорядочивание записей относительно других записей и чтений: Присвоение уникального

- 12. Принятое в проекте решение Положения оптимизированного режима Используются все аппаратные механизмы неоптимизированного режима Механизм разбиения операций

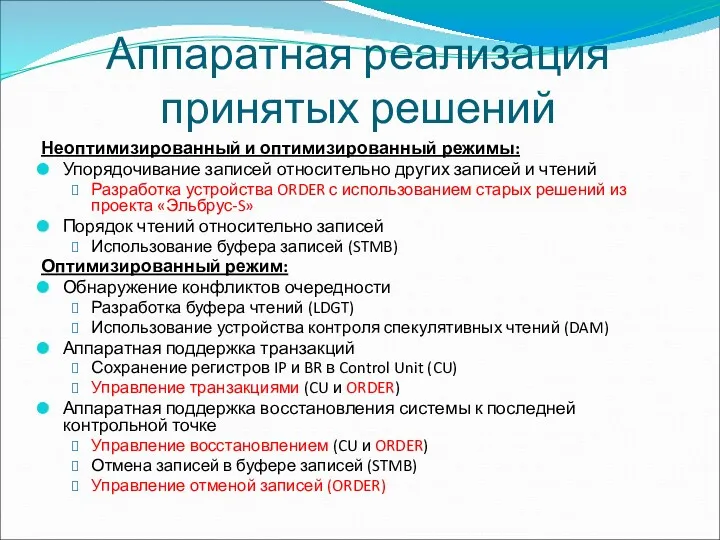

- 13. Аппаратная реализация принятых решений Неоптимизированный и оптимизированный режимы: Упорядочивание записей относительно других записей и чтений Разработка

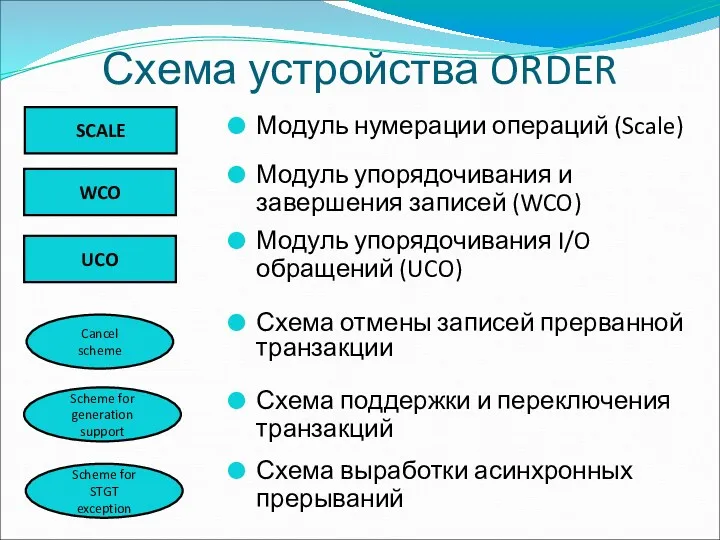

- 14. Схема устройства ORDER Модуль нумерации операций (Scale) Модуль упорядочивания и завершения записей (WCO) Модуль упорядочивания I/O

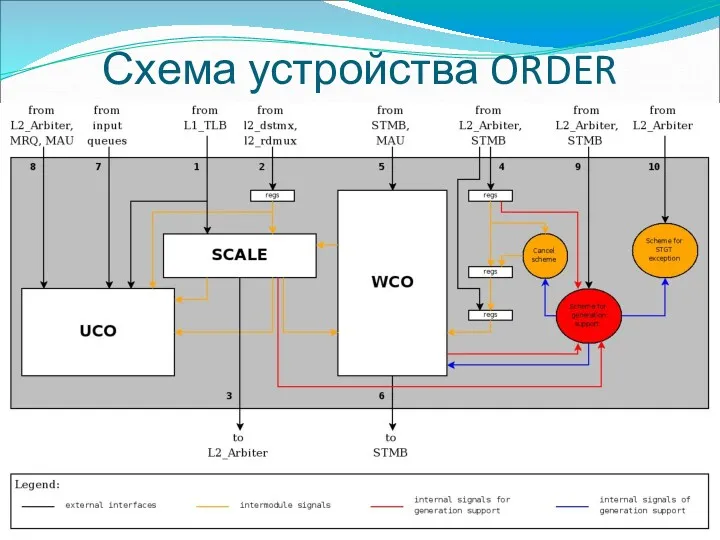

- 15. Схема устройства ORDER

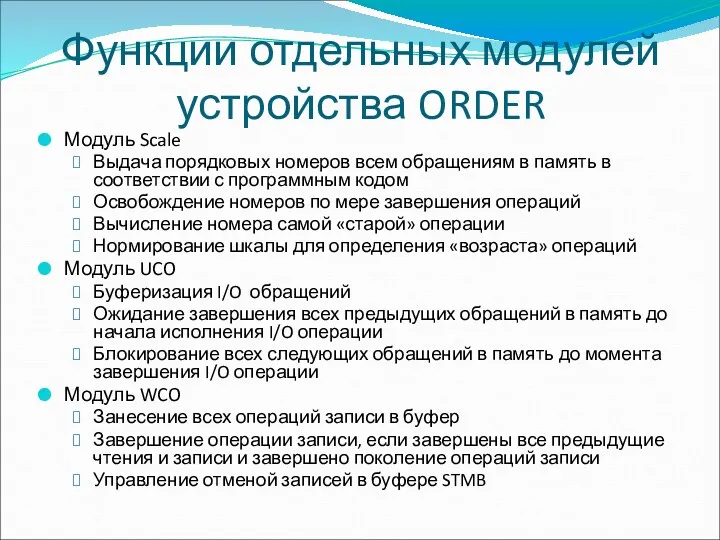

- 16. Функции отдельных модулей устройства ORDER Модуль Scale Выдача порядковых номеров всем обращениям в память в соответствии

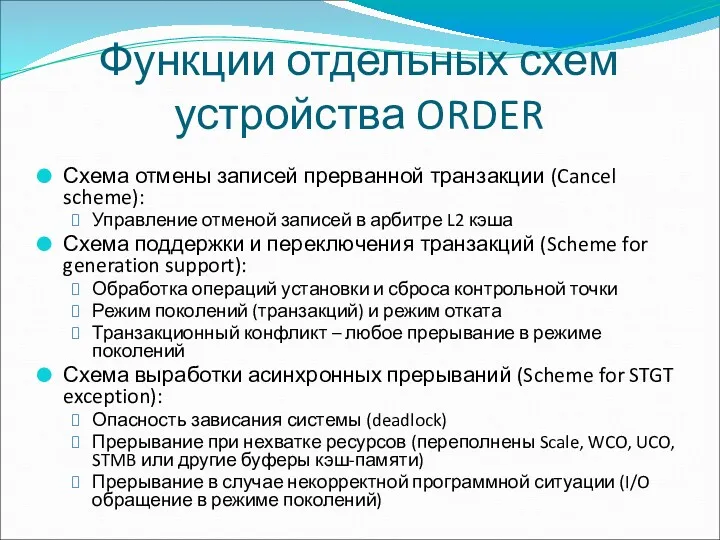

- 17. Функции отдельных схем устройства ORDER Схема отмены записей прерванной транзакции (Cancel scheme): Управление отменой записей в

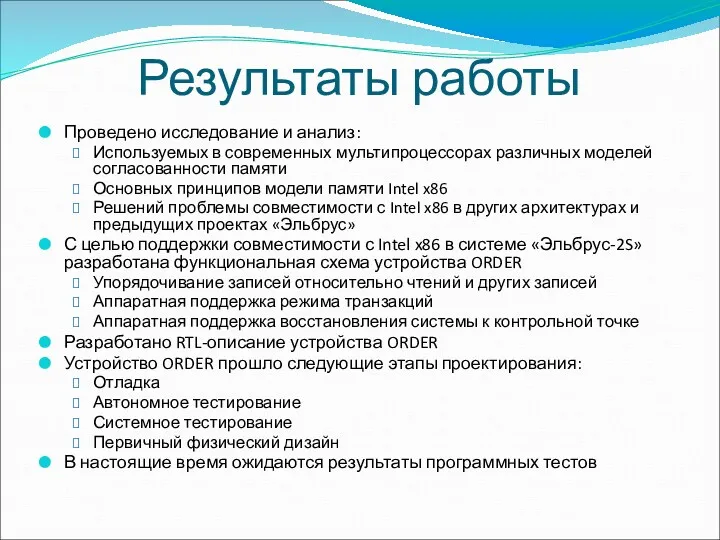

- 18. Результаты работы Проведено исследование и анализ: Используемых в современных мультипроцессорах различных моделей согласованности памяти Основных принципов

- 20. Скачать презентацию

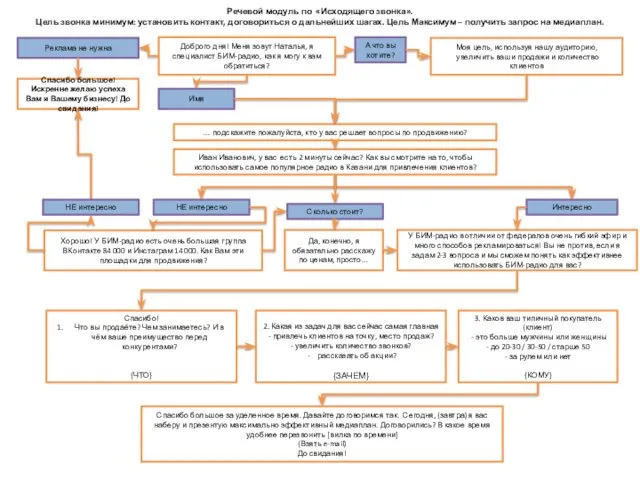

Речевые модули БИМ

Речевые модули БИМ Полуфабрикаты из мяса говядины

Полуфабрикаты из мяса говядины Презентация детского браузера Гогуль

Презентация детского браузера Гогуль Черты характера во фразеологизмах

Черты характера во фразеологизмах Моє рідне місто. Мальовниче місто Житомир

Моє рідне місто. Мальовниче місто Житомир Презентация_ООО_Первый_километр_2024

Презентация_ООО_Первый_километр_2024 Конструктивные особенности высокопроизводительных современных ЭВМ

Конструктивные особенности высокопроизводительных современных ЭВМ Организация технического обслуживания и ремонта машинно-тракторного парка по круглогодовому графику с разработкой технологии

Организация технического обслуживания и ремонта машинно-тракторного парка по круглогодовому графику с разработкой технологии Теоретические аспекты проектного обучения

Теоретические аспекты проектного обучения Построение урока на основе системно-деятельностного подхода

Построение урока на основе системно-деятельностного подхода Международный день прав животных

Международный день прав животных Регистры. Параллельные регистры

Регистры. Параллельные регистры Повторение изученного в 6 классе

Повторение изученного в 6 классе Cerberus Mouse FW update SOP

Cerberus Mouse FW update SOP Банковская система Китая

Банковская система Китая Классификация и химические свойства основных классов неорганических соединений

Классификация и химические свойства основных классов неорганических соединений Тауэрский мост

Тауэрский мост Ассортимент трикотажных товаров

Ассортимент трикотажных товаров Загородный поселок класса de luxe Гринфилд

Загородный поселок класса de luxe Гринфилд 1 сентября - День Знаний

1 сентября - День Знаний Географическое лото по теме Литосфера 6 класс

Географическое лото по теме Литосфера 6 класс Интерактивная презентация

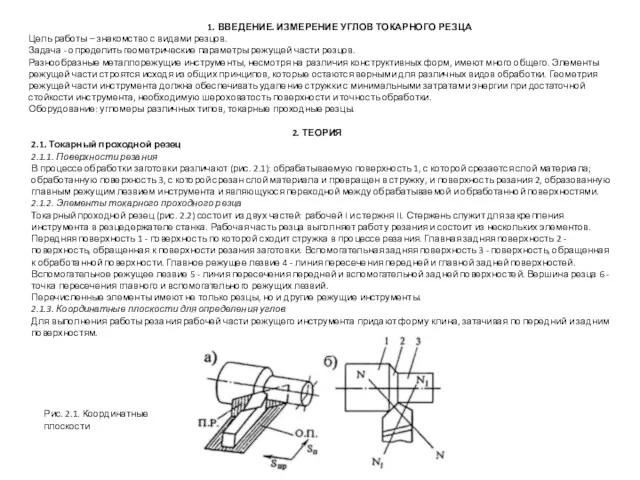

Интерактивная презентация Введение. Измерение углов токарного резца

Введение. Измерение углов токарного резца Теория эволюции. Откуда берутся новые формы живых систем?

Теория эволюции. Откуда берутся новые формы живых систем? Заканчивание скважин

Заканчивание скважин Повторение: квадратные уравнения. Решение упражнений с использованием сведений о космонавтике. 9 класс

Повторение: квадратные уравнения. Решение упражнений с использованием сведений о космонавтике. 9 класс Социальные, психологические и речевые нормы общения

Социальные, психологические и речевые нормы общения Вест Гарант

Вест Гарант