Слайд 2

Регистром называется узел ЭВМ, предназначенный для приема, хранения и передачи информации

в другие узлы в процессе выполнения операций в вычислительных устройствах.

Слайд 3

Регистр представляет собой совокупность триггеров, число которых соответствует количеству разрядов размещаемой

в нем информации.

Наличие прямых и инверсных выходов позволяет использовать устройство для получения кодов чисел хранимой информации.

Слайд 4

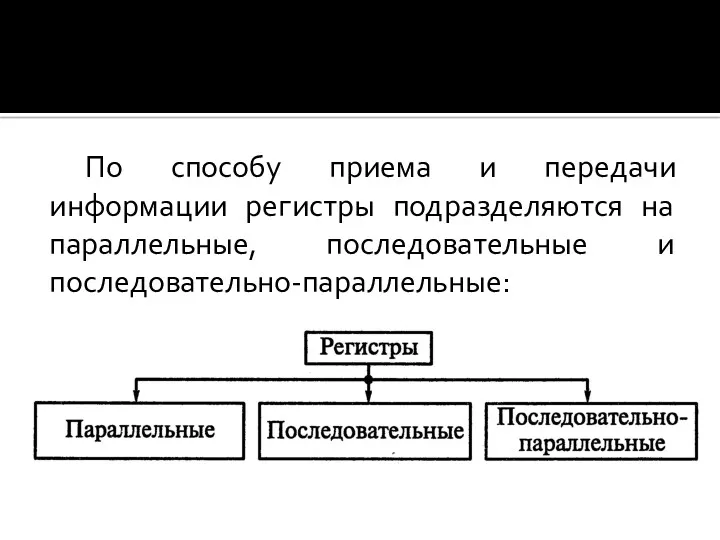

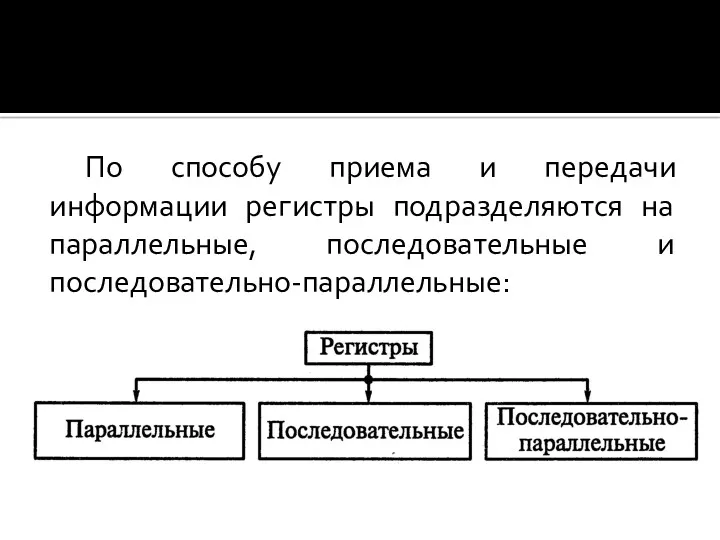

По способу приема и передачи информации регистры подразделяются на параллельные, последовательные

и последовательно-параллельные:

Слайд 5

1. Параллельные регистры

Прием и передача n-разрядного кода производится параллельно под воздействием

управляющего синхросигнала

Слайд 6

2. Последовательные регистры

Прием и передача n-разрядного кода информации могут производится последовательно

разряд за разрядом, при этом внутри регистра возможны однонаправленный сдвиг информации из разряда в разряд влево или вправо и двунаправленный (реверсивный) сдвиг в зависимости от условий как вправо, так и влево

Слайд 7

3. Последовательно-параллельные регистры

Прием и передача n-разрядного кода информации производится в последовательном,

параллельном и смешанном режимах. В смешанном режиме регистр выполняет функции преобразователя последовательного входного кода в параллельный выходной код и, наоборот, параллельного входного кода в последовательный выходной код.

Слайд 8

Схемы простейших регистров

Слайд 9

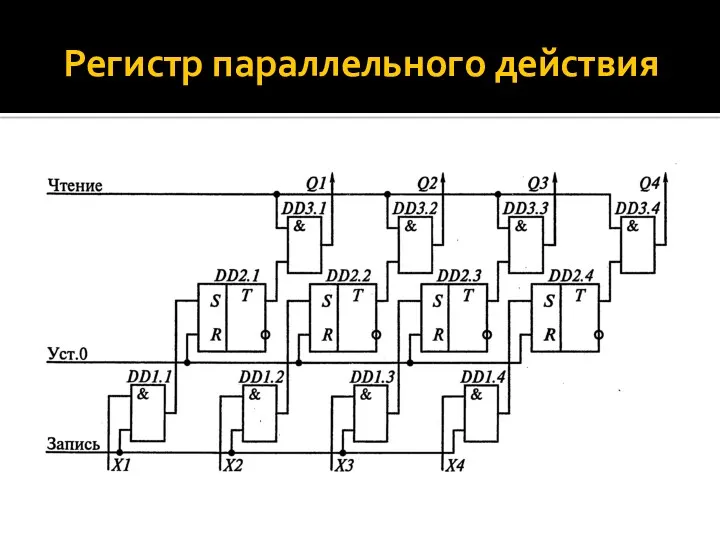

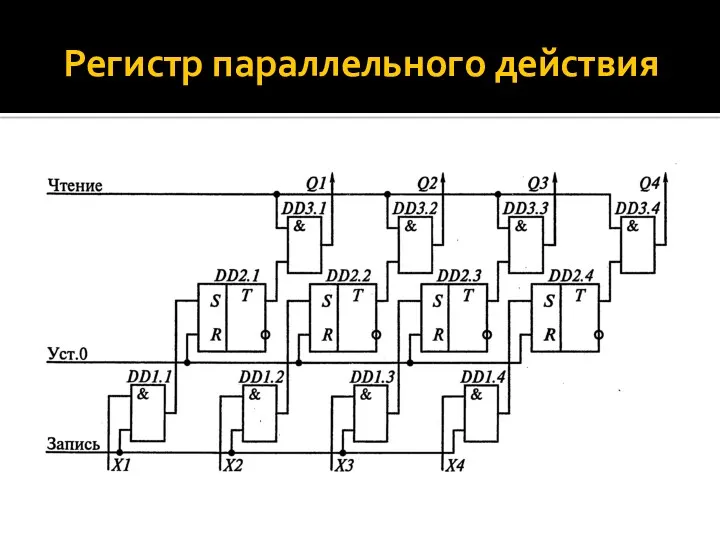

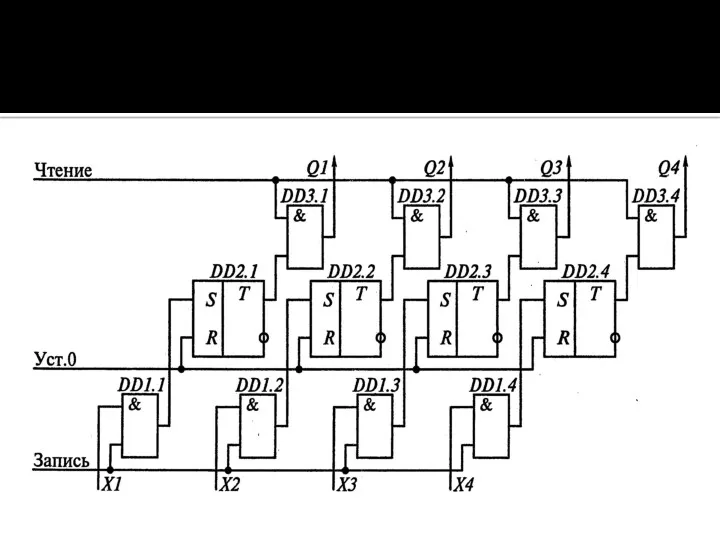

Регистр параллельного действия

Слайд 10

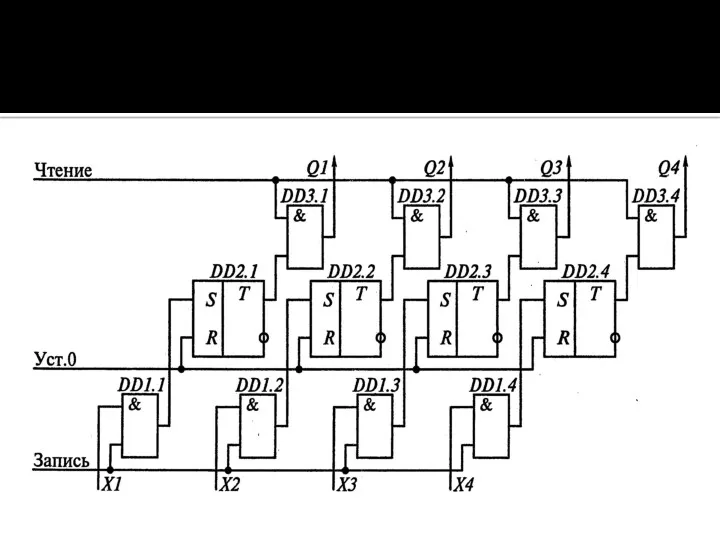

входные ключи DD1, используемые для ввода в регистр четырехразрядной информации;

элементы памяти

DD2, асинхронные RS-триггеры;

выходные ключи DD3, используемые для вывода из регистра хранимой информации

Слайд 11

Регистр может работать в следующих режимах:

предварительная установка (подготовка триггеров регистра к

записи информации);

запись информации в триггеры регистра;

хранение ранее записанной информации;

чтение информации из регистра.

Слайд 12

Записываемая информация поступает на информационные входы X1-X4. Вход «Уст.0» используется для

предварительной установки триггеров в нулевое состояние подачей него лог. 1. Управление режимами работы осуществляется по управляющим входам: «Запись», «Чтение». При отсутствии управляющих сигналов, равных лог. 1, на этих входах находятся лог. 0.

Слайд 13

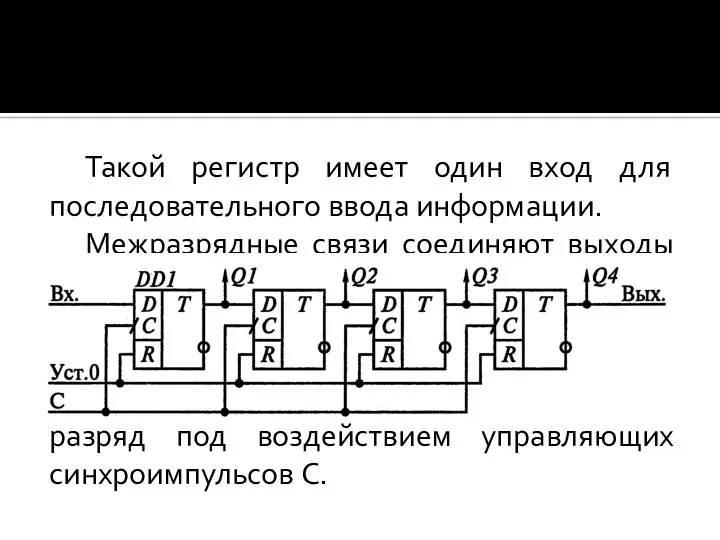

Регистр последовательного действия

Слайд 14

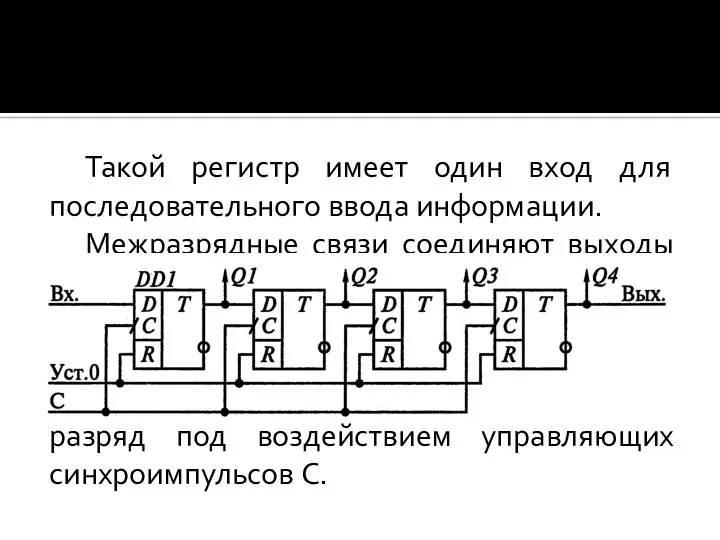

Такой регистр имеет один вход для последовательного ввода информации.

Межразрядные связи соединяют

выходы триггеров младших разрядов с входами триггеров старших разрядов, что позволяет осуществить последовательное продвижение информации из разряда в разряд под воздействием управляющих синхроимпульсов C.

Слайд 15

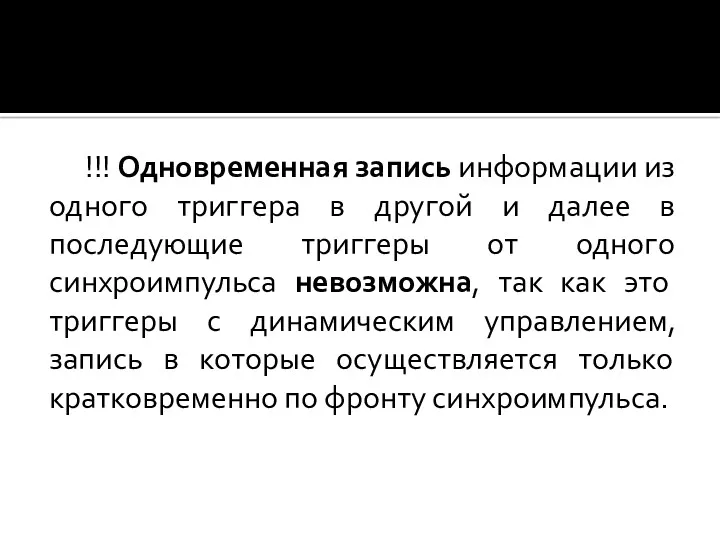

!!! Одновременная запись информации из одного триггера в другой и далее

в последующие триггеры от одного синхроимпульса невозможна, так как это триггеры с динамическим управлением, запись в которые осуществляется только кратковременно по фронту синхроимпульса.

Слайд 16

При объединении выводов входа и выхода образуется схема кольцевого регистра, в

котором происходит циркуляция ранее записанной информации.

Регистр последовательного действия уступает регистру параллельного действия в быстродействии и используется только в случаях, когда количество входных и выходных линий связи ограничено.

Слайд 17

Реверсивные регистры

Логическая схема И-ИЛИ

Слайд 18

Как правило, схемы регистров выполняют сложные функции. Часто предусматривается возможность их

работы как в параллельном, так и в последовательном режимах, а также возможность сдвига информации как влево, так и вправо.

Когда в схеме совмещены такие функции, то говорят, что она работает в реверсивном режиме. Для организации работы в реверсивном режиме используют логические схемы И-ИЛИ.

Слайд 19

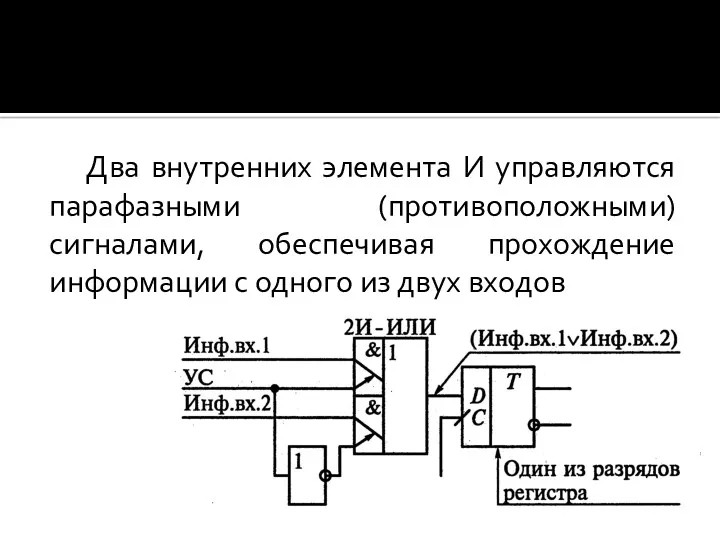

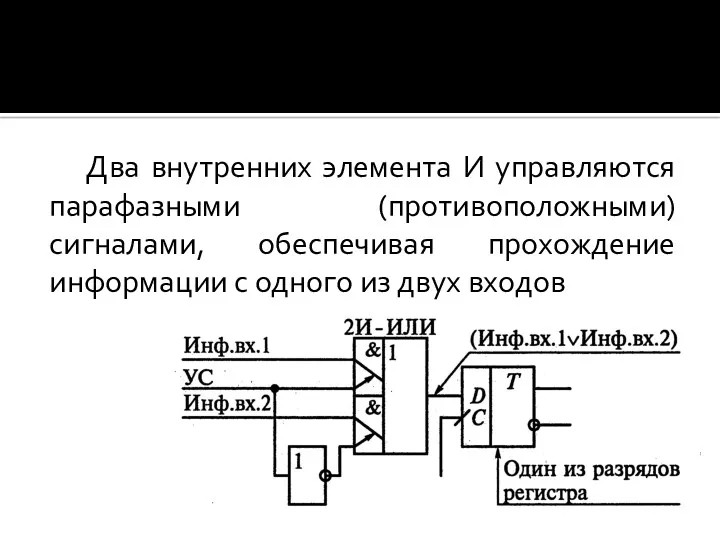

Два внутренних элемента И управляются парафазными (противоположными) сигналами, обеспечивая прохождение информации

с одного из двух входов

Слайд 20

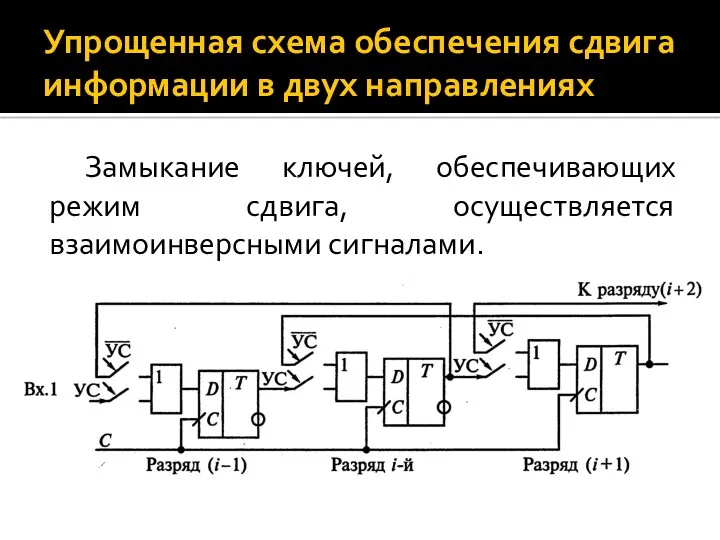

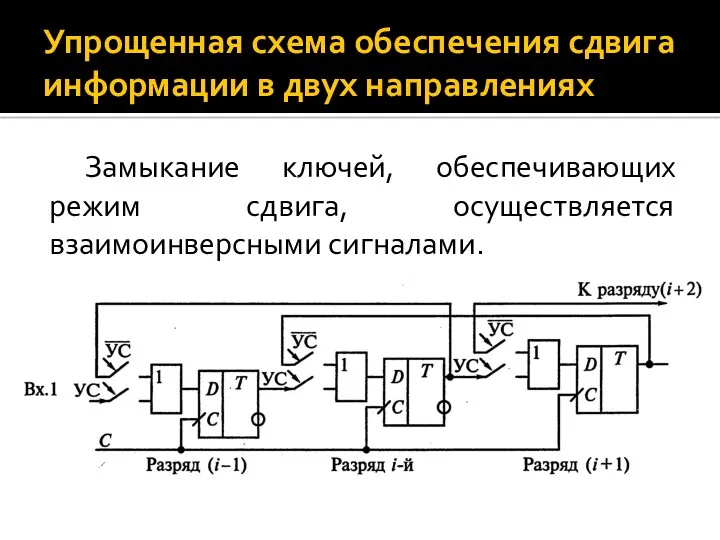

Упрощенная схема обеспечения сдвига информации в двух направлениях

Замыкание ключей, обеспечивающих режим

сдвига, осуществляется взаимоинверсными сигналами.

Слайд 21

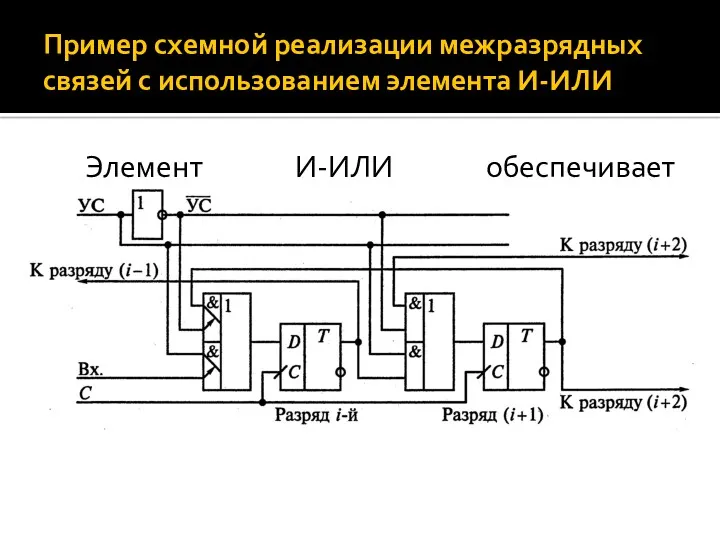

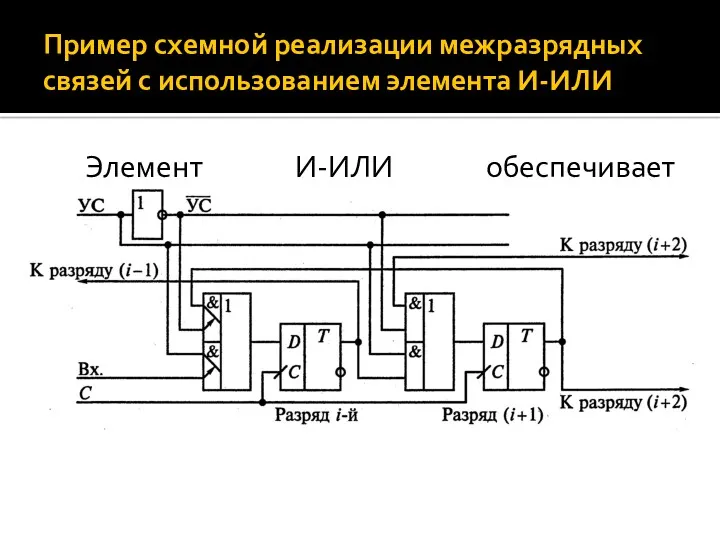

Пример схемной реализации межразрядных связей с использованием элемента И-ИЛИ

Элемент И-ИЛИ обеспечивает

поступление сигналов с прямых выходов старших разрядов на выходы D младших или наоборот. Фиксация поступающей информации происходит в момент прихода синхроимпульса.

Слайд 22

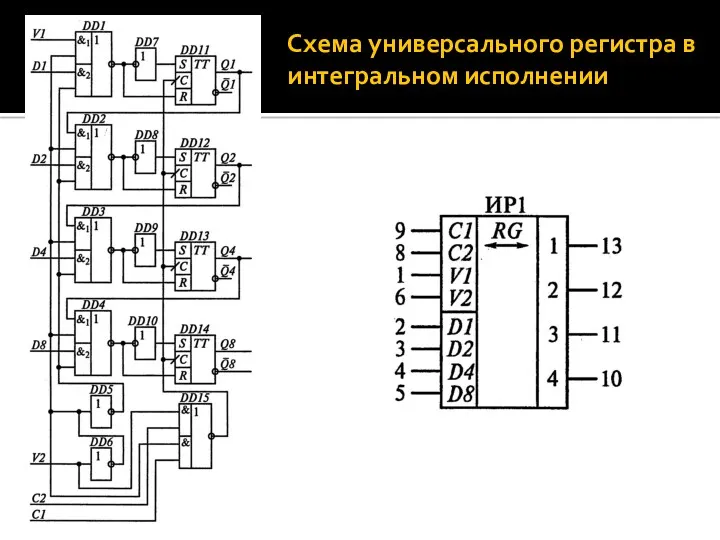

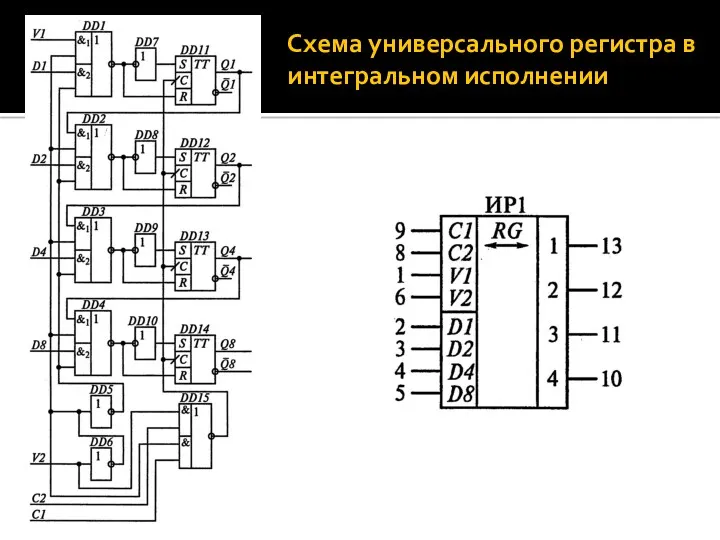

Схема универсального регистра в интегральном исполнении

Слайд 23

Схема может работать в следующих режимах:

Параллельная запись;

Последовательная запись и сдвиг информации

из младших разрядов в старшие;

Последовательная запись и сдвиг информации из старших разрядов в младшие;

Совмещение двух режимов – параллельной записи и сдвига информации с последующей записью в освобождающиеся разряды новых данных.

Слайд 24

Режим работы задается сигналом, поданным на вход V2.

При параллельной записи и

последовательном сдвиге информации от старших разрядов к младшим на вход V2 подается лог. 1, при последовательном вводе и сдвиге информации от младших разрядов к старшим – лог.0

Слайд 25

Параллельная запись информации осуществляется по информационным входам D1, D2, D4, D8;

Последовательный

ввод информации производится по входу V1, начиная со старшего разряда.

При параллельной записи синхроимпульс подается на вход c2, при последовательном сдвиге – на вход C1.

Слайд 26

Схемы DD1…DD4 выполняют роль ключей-инверторов, которые пропускают информацию или с параллельных

входов D1,D2,D4,D8, или с выходов триггеров младших разрядов на входы старших разрядов при последовательном вводе и сдвиге информации.

Слайд 27

Управление замыканием ключей осуществляется через схемы DD5, DD6.

Вводимая в триггеры информация

проходит через дополнительные инверторы DD7…DD10, поступая парафазным кодом на входы S и R синхронных триггеров, и фиксируется в них с приходом синхроимпульса.

Слайд 28

Управление работой регистра можно осуществлять от одного синхроимпульса, для чего необходимо

объединить входы C1 и C2.

Слайд 29

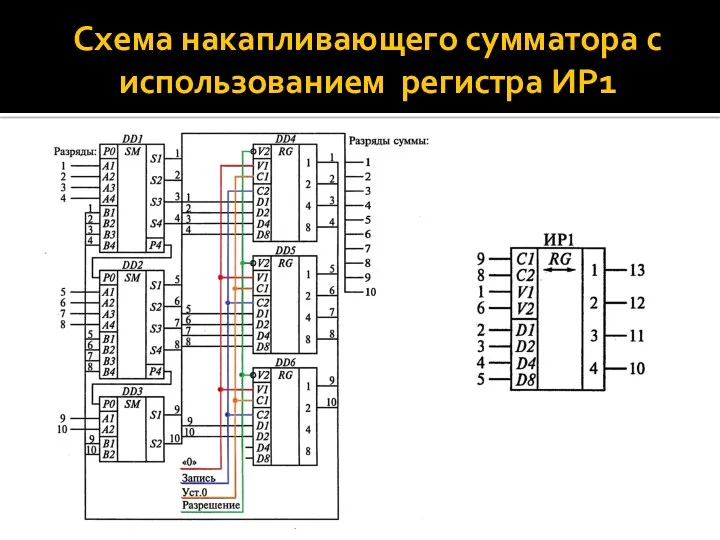

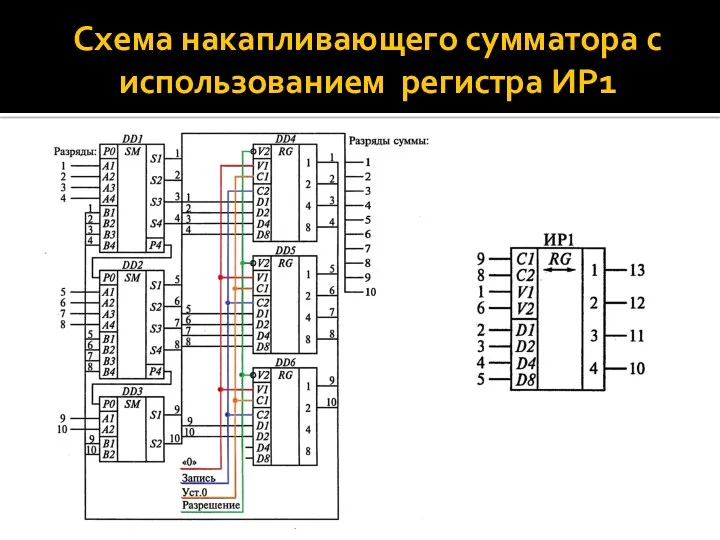

Схема накапливающего сумматора с использованием регистра ИР1

Международная торговля и услуги

Международная торговля и услуги Биосфера, как система, обеспечивающая существование человека

Биосфера, как система, обеспечивающая существование человека Универсальный дизайн в основной возрастной и профессиональной деятельности

Универсальный дизайн в основной возрастной и профессиональной деятельности Простейшие переборные задачи. Генерация подмножеств и перестановок

Простейшие переборные задачи. Генерация подмножеств и перестановок Синтетические противомикробные средства

Синтетические противомикробные средства Выжигание

Выжигание Презентация к уроку технологии Аппликация Осень в лесу

Презентация к уроку технологии Аппликация Осень в лесу Информационная безопасность и защита информации в медицинском учреждении

Информационная безопасность и защита информации в медицинском учреждении О профессиях для дошкольников

О профессиях для дошкольников класс. ЛР №5

класс. ЛР №5 Правовой режим информации, распространение которой ограничивается или запрещается

Правовой режим информации, распространение которой ограничивается или запрещается Черновая отделка. Группа компаний Удача

Черновая отделка. Группа компаний Удача Кавказ.

Кавказ. 7kl_ur1_piton

7kl_ur1_piton Мозаика народов. Россия – многонациональная страна

Мозаика народов. Россия – многонациональная страна Плата за негативное воздействие на окружающую среду

Плата за негативное воздействие на окружающую среду Портфолио учителя

Портфолио учителя Источники ошибок ГНСС-измерений. Режимы ГНСС-измерений

Источники ошибок ГНСС-измерений. Режимы ГНСС-измерений Расчёт теплового баланса реакционного узла. Лекция 4

Расчёт теплового баланса реакционного узла. Лекция 4 Оригами-танграм

Оригами-танграм Значение подвижных игр

Значение подвижных игр Умная телефония для оптимальной работы с клиентами

Умная телефония для оптимальной работы с клиентами Термообработка стали

Термообработка стали Der beruf – die berufe

Der beruf – die berufe Презентация к статье Формы взаимодействия педагога с детьми в условиях реализации образовательной программы Югорский трамплин

Презентация к статье Формы взаимодействия педагога с детьми в условиях реализации образовательной программы Югорский трамплин Концевые эффекты и их значение при измерениях фильтрационных характеристик

Концевые эффекты и их значение при измерениях фильтрационных характеристик Ранний возраст

Ранний возраст Атмосферное давление

Атмосферное давление