Содержание

- 2. Структура микропроцессора Intel 80386 Циклический сдвигатель, сумматор Умножитель/ делитель Набор регистров Декодирование и упорядочение Управляющее ПЗУ

- 3. Регистры ЦП 80386 Программно доступные регистры: 8 регистров общего назначения (32-разрядные). Регистр флагов (EFLAGS – 32-разрядный).

- 4. Режимы работы ЦП 80386 Реальный режим или режим реальных адресов. В реальном режиме МП работает как

- 5. ЦП 80386 (переключение режимов)

- 6. Формирование линейного адреса без участия селекторов В режиме реального адреса и в режиме системного управления используется

- 7. Формирование линейного адреса в защищенном режиме Если в регистре управления CR0 бит PG- разбиение на страницы

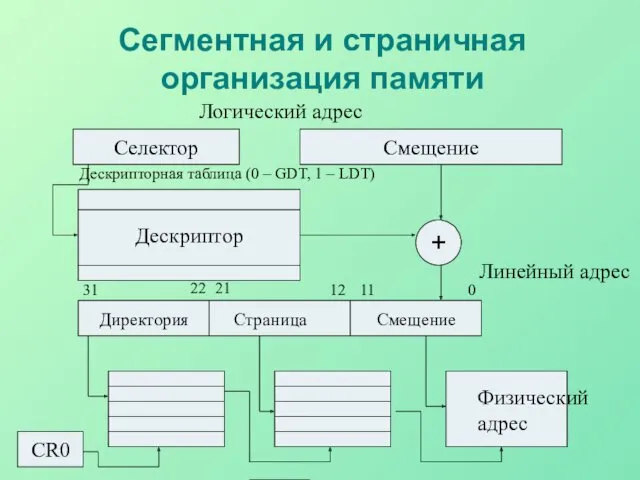

- 8. Сегментная и страничная организация памяти Селектор Смещение Дескриптор CR0 Линейный адрес Логический адрес Физический адрес Дескрипторная

- 9. Многозадачность в ЦП 80386 Многозадачность - это метод управления компьютерной системой, когда отдельные задачи выполняются так,

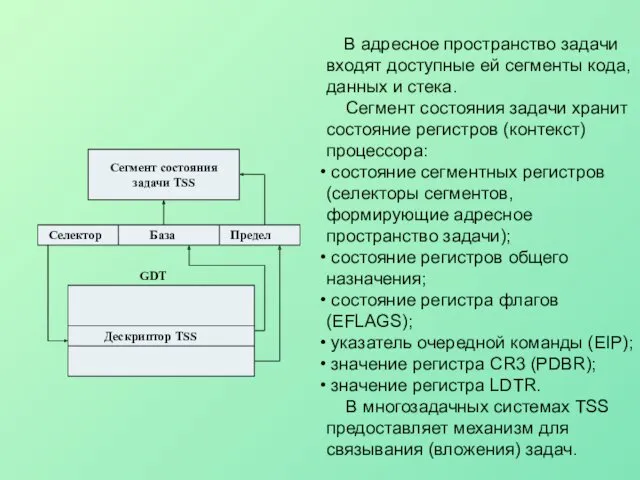

- 10. В адресное пространство задачи входят доступные ей сегменты кода, данных и стека. Сегмент состояния задачи хранит

- 11. Сравнительные характеристики режимов работы процессора

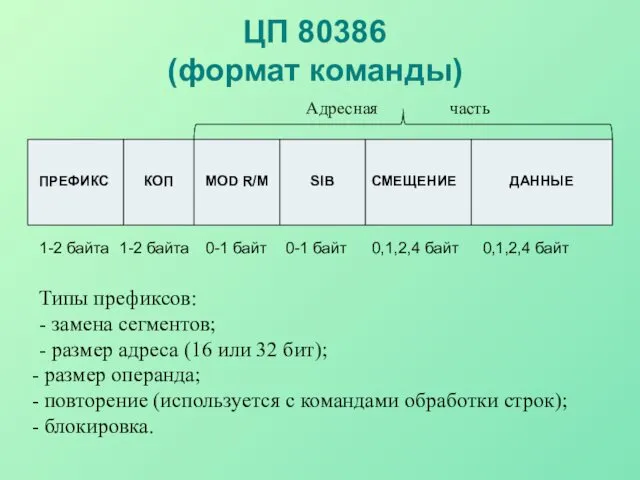

- 12. ЦП 80386 (формат команды) ПРЕФИКС КОП MOD R/M SIB СМЕЩЕНИЕ ДАННЫЕ 1-2 байта 1-2 байта 0-1

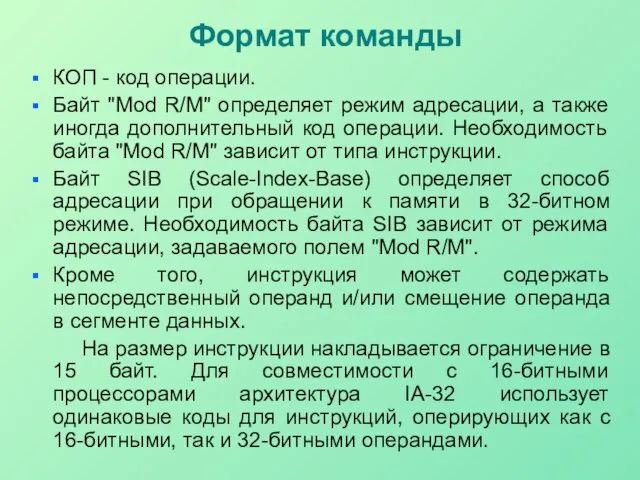

- 13. Формат команды КОП - код операции. Байт "Mod R/M" определяет режим адресации, а также иногда дополнительный

- 14. Структура микропроцессора Intel 80486 Шинный интерфейс Драйверы адреса Буферы записи Приемо- передатчики данных Управление шиной Управление

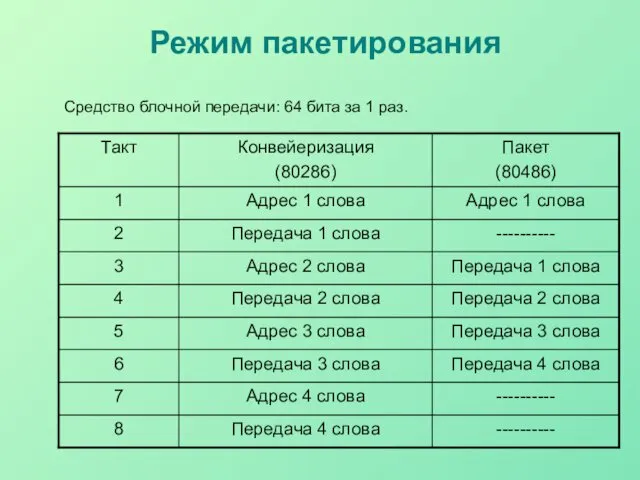

- 15. Режим пакетирования Средство блочной передачи: 64 бита за 1 раз.

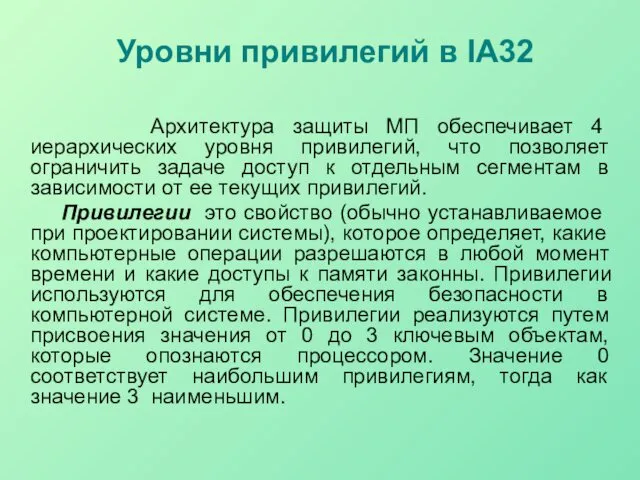

- 16. Уровни привилегий в IA32 Архитектура защиты МП обеспечивает 4 иерархических уровня привилегий, что позволяет ограничить задаче

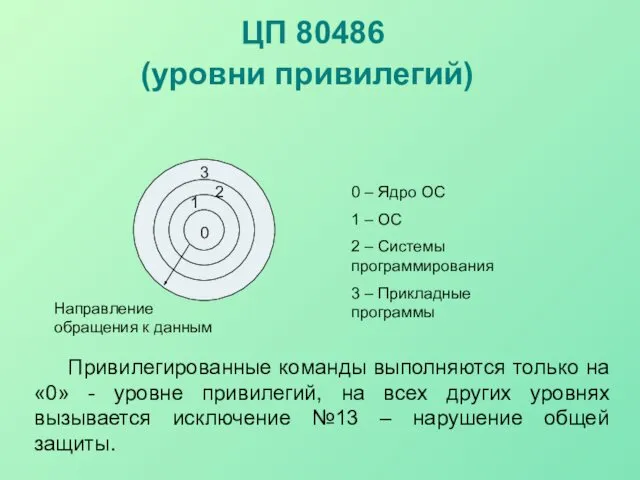

- 17. ЦП 80486 (уровни привилегий) 0 1 2 3 0 – Ядро ОС 1 – ОС 2

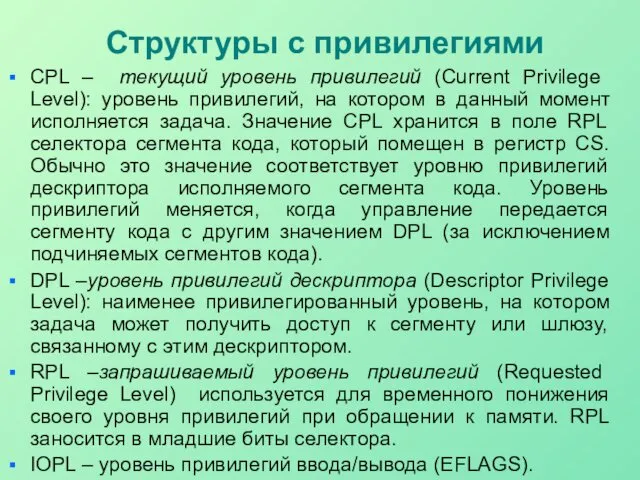

- 18. Структуры с привилегиями CPL – текущий уровень привилегий (Current Privilege Level): уровень привилегий, на котором

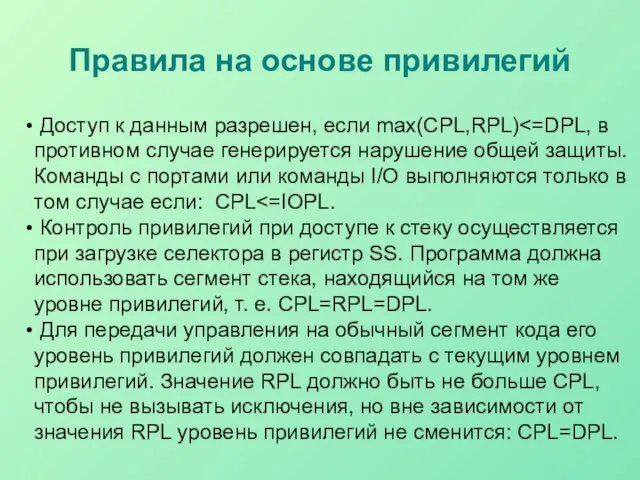

- 19. Доступ к данным разрешен, если max(CPL,RPL) Контроль привилегий при доступе к стеку осуществляется при загрузке селектора

- 20. Вопросы для самоконтроля Какие регистры составляют программная модель ЦП 80386? В каких режимах может работать ЦП

- 22. Скачать презентацию

Школьные службы примирения

Школьные службы примирения Wooden structures of wooden structures by the method of limit states

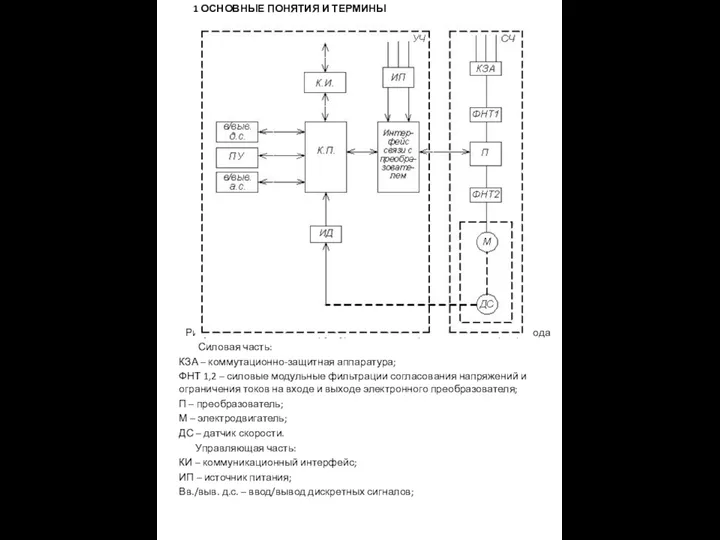

Wooden structures of wooden structures by the method of limit states Обобщенная структурная схема современного электропривода

Обобщенная структурная схема современного электропривода Роль компьютера в жизни человека

Роль компьютера в жизни человека Swot-анализ компании Renault Nissan

Swot-анализ компании Renault Nissan Культурне життя України в умовах незалежності

Культурне життя України в умовах незалежності Презентация Нестандартный урок

Презентация Нестандартный урок Методика расследования преступлений против семьи и несовершеннолетних

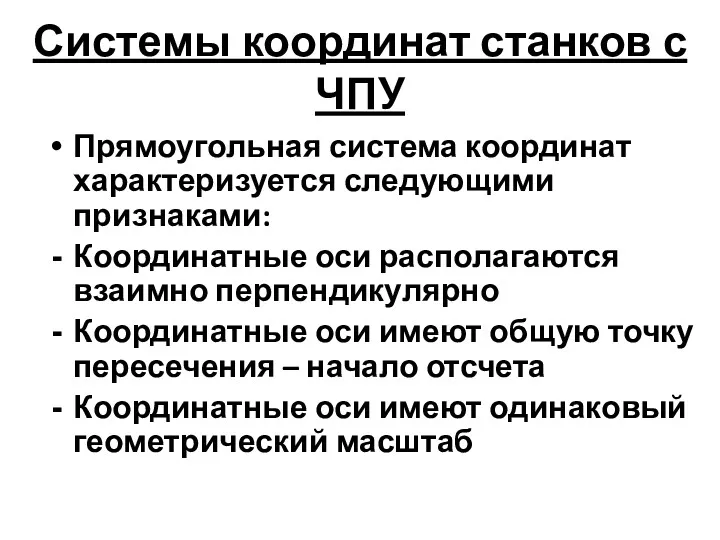

Методика расследования преступлений против семьи и несовершеннолетних Системы координат станков с ЧПУ

Системы координат станков с ЧПУ High Sensitivity Camera. NEC Corporation

High Sensitivity Camera. NEC Corporation Футбол - мой любимый вид спорта

Футбол - мой любимый вид спорта Информационная работа первичной профсоюзной организации

Информационная работа первичной профсоюзной организации Podorozhny

Podorozhny Stereotypes_that_help_me_learn_the_world (1)

Stereotypes_that_help_me_learn_the_world (1) История города Павлово

История города Павлово Устный журнал России верные сыны

Устный журнал России верные сыны Shinto

Shinto Великая русская революция

Великая русская революция Өзараауысымдылық және тегіс цилиндрлік біріктірулерді бақылау

Өзараауысымдылық және тегіс цилиндрлік біріктірулерді бақылау Здравствуйте, это мы!

Здравствуйте, это мы! 20230925_kartochki

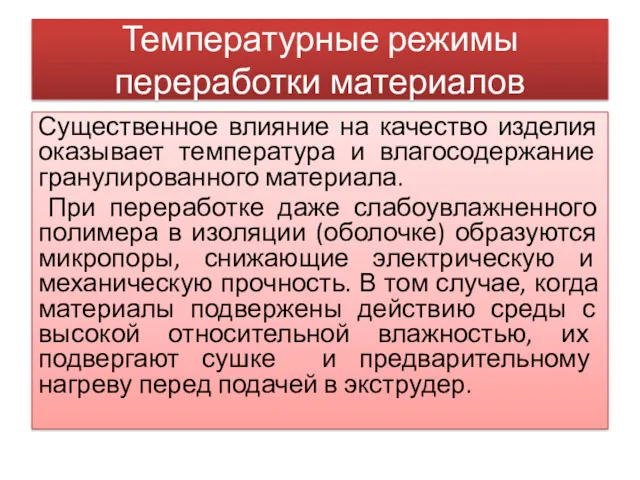

20230925_kartochki Экструдер. Температурные режимы переработки материалов

Экструдер. Температурные режимы переработки материалов Учимся готовить: десерт Клубничка

Учимся готовить: десерт Клубничка Калининградская область. Агрохолдинг ДолговГрупп

Калининградская область. Агрохолдинг ДолговГрупп Волонтерский проект Твори Добро

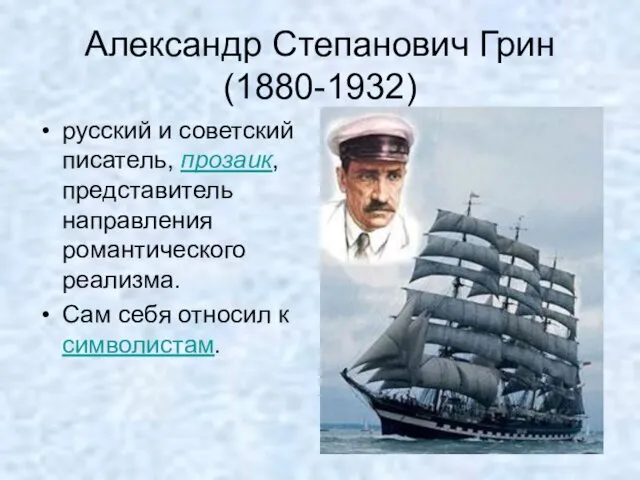

Волонтерский проект Твори Добро Александр Степанович Грин (1880-1932)

Александр Степанович Грин (1880-1932) Характеристика бизнес-плана. (Лекция 2)

Характеристика бизнес-плана. (Лекция 2) Эстетикалық стоматология үшін оптикалық жүйенің маңызы

Эстетикалық стоматология үшін оптикалық жүйенің маңызы