Содержание

- 2. Логические основы ЭВМ Базовые функциональные элементы ЭВМ (вентили) Основные логические схемы

- 3. Вентили Логический элемент - электронное устройство, на входах и выходах которого сигнал может иметь только один

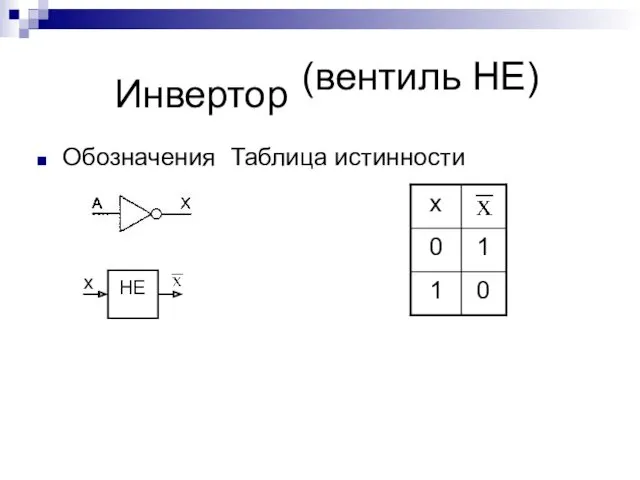

- 4. Инвертор Обозначения Таблица истинности (вентиль НЕ)

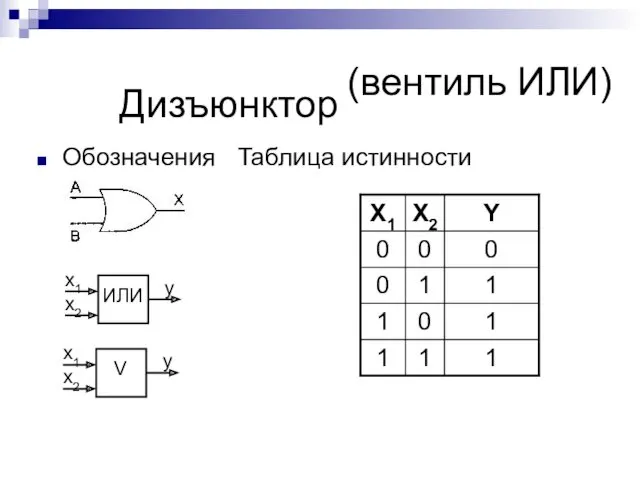

- 5. Дизъюнктор Обозначения Таблица истинности (вентиль ИЛИ)

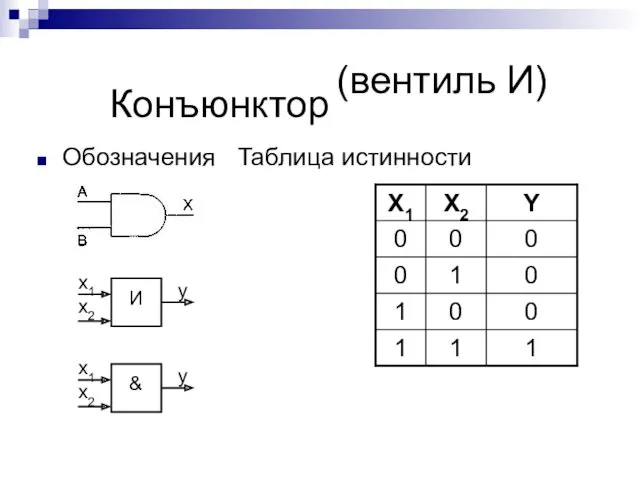

- 6. Конъюнктор Обозначения Таблица истинности (вентиль И)

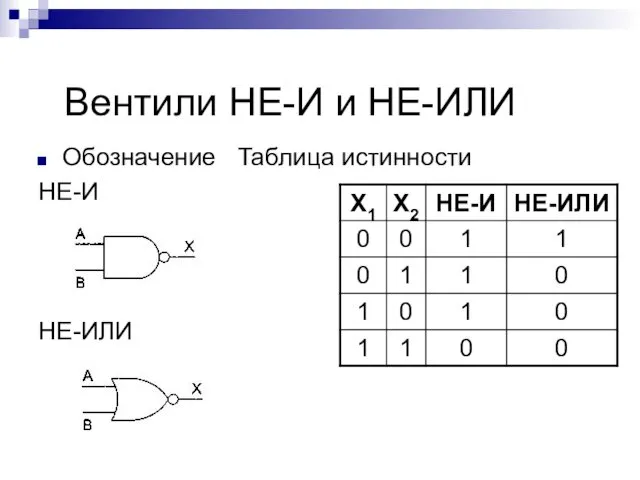

- 7. Вентили НЕ-И и НЕ-ИЛИ Обозначение Таблица истинности НЕ-И НЕ-ИЛИ

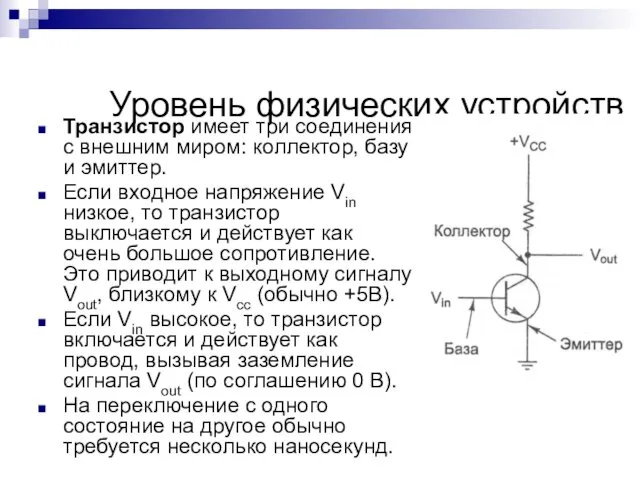

- 8. Уровень физических устройств Транзистор имеет три соединения с внешним миром: коллектор, базу и эмиттер. Если входное

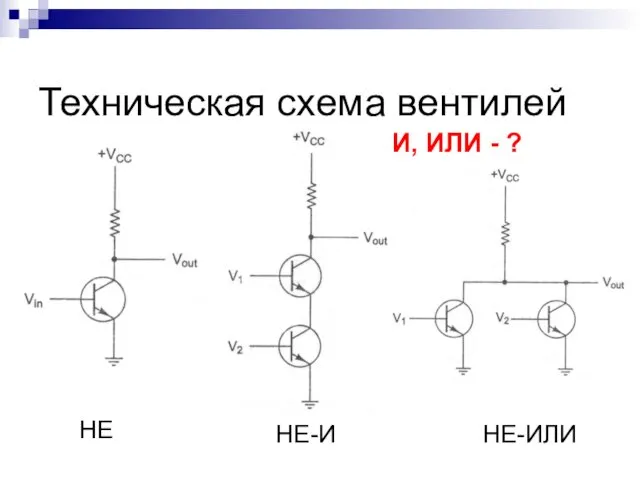

- 9. Техническая схема вентилей НЕ И, ИЛИ - ? НЕ-И НЕ-ИЛИ

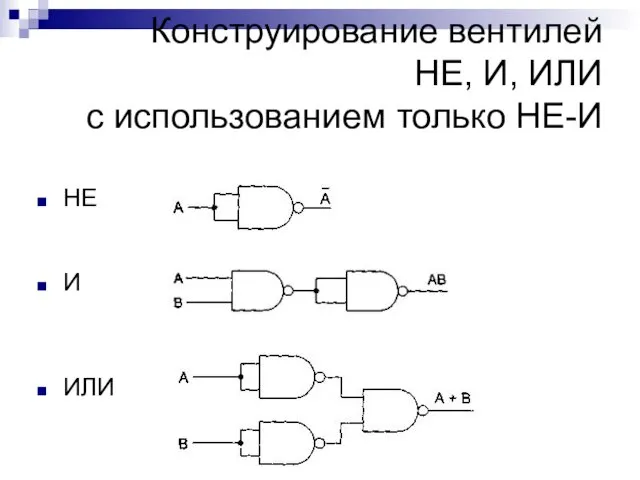

- 10. Конструирование вентилей НЕ, И, ИЛИ с использованием только НЕ-И НЕ И ИЛИ

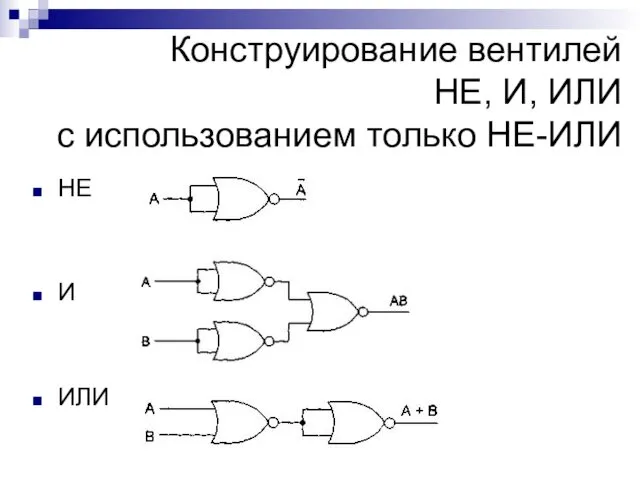

- 11. Конструирование вентилей НЕ, И, ИЛИ с использованием только НЕ-ИЛИ НЕ И ИЛИ

- 12. Логический синтез схем Одноразрядный двоичный полусумматор Полный одноразрядный сумматор Полный многоразрядный сумматор Дешифратор Триггер

- 13. Как реализовать схему Составить таблицу истинности для данной функции Обеспечить инверторы, чтобы порождать инверсии для каждого

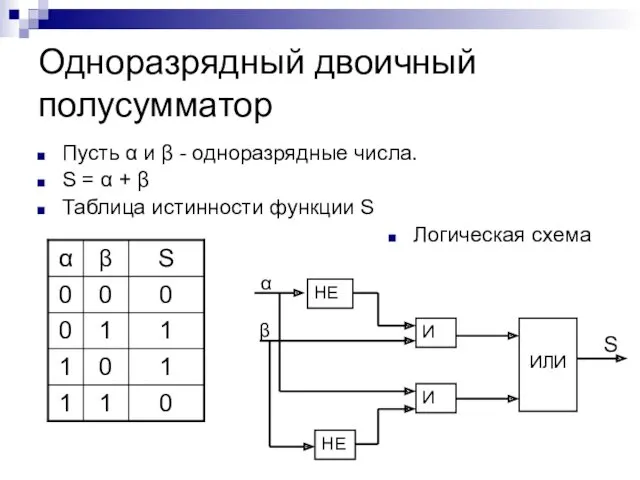

- 14. Одноразрядный двоичный полусумматор Пусть α и β - одноразрядные числа. S = α + β Таблица

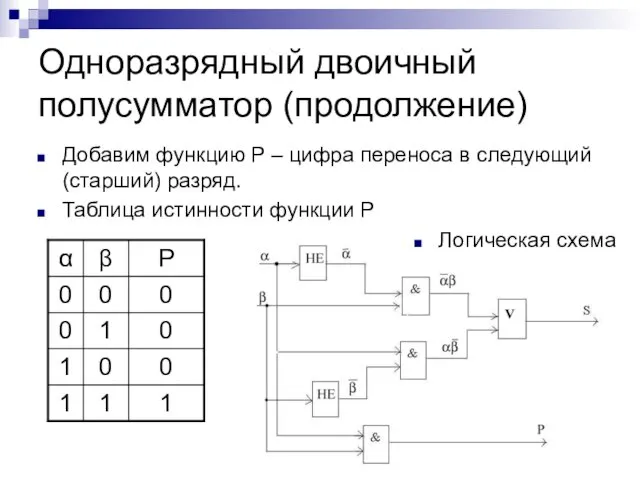

- 15. Одноразрядный двоичный полусумматор (продолжение) Добавим функцию P – цифра переноса в следующий (старший) разряд. Таблица истинности

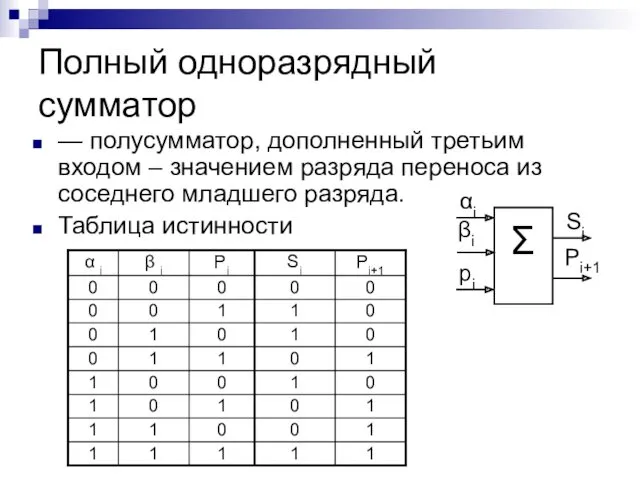

- 16. Полный одноразрядный сумматор — полусумматор, дополненный третьим входом – значением разряда переноса из соседнего младшего разряда.

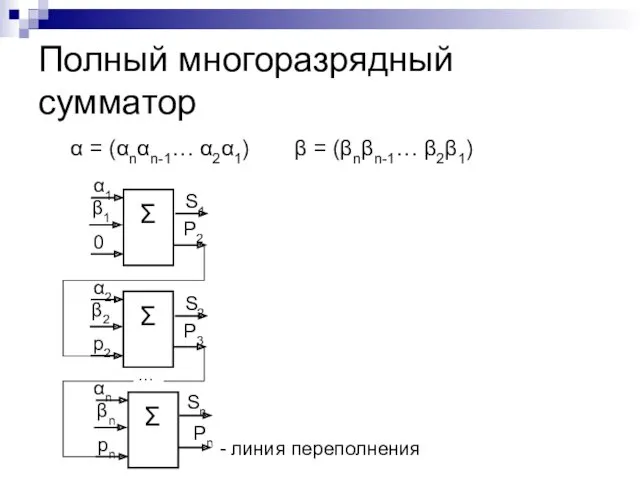

- 17. Полный многоразрядный сумматор β1 0 P2 S1 Σ α1 β2 p2 P3 S2 Σ α2 βn

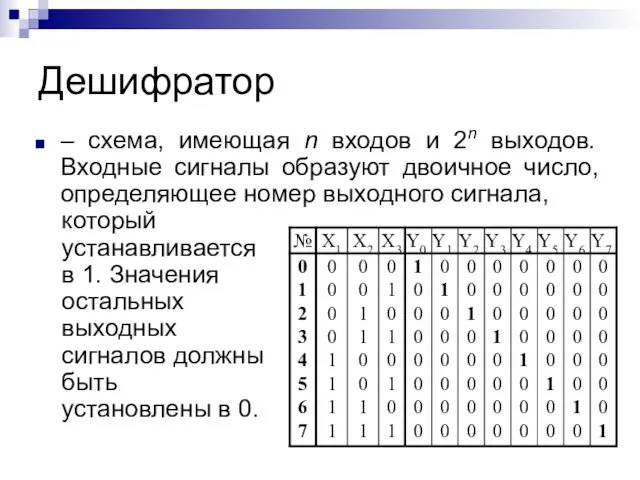

- 18. Дешифратор – схема, имеющая n входов и 2n выходов. Входные сигналы образуют двоичное число, определяющее номер

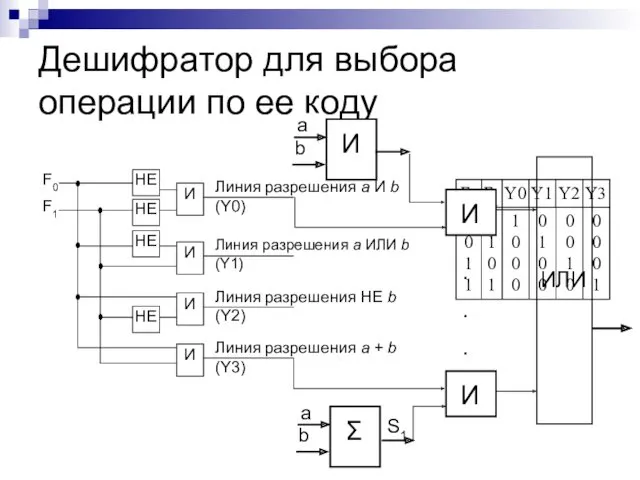

- 19. Дешифратор для выбора операции по ее коду b S1 Σ a И b И a И

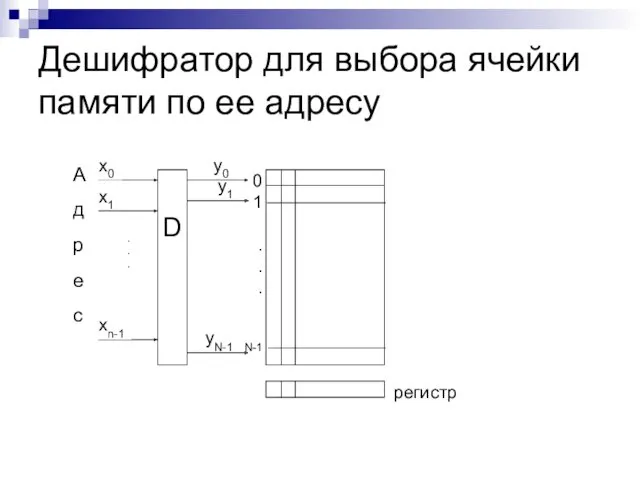

- 20. Дешифратор для выбора ячейки памяти по ее адресу

- 21. Определения Схема называется комбинационной (схема без памяти), если значения переменных на выходе схемы однозначно зависят только

- 23. Скачать презентацию

Lec_10

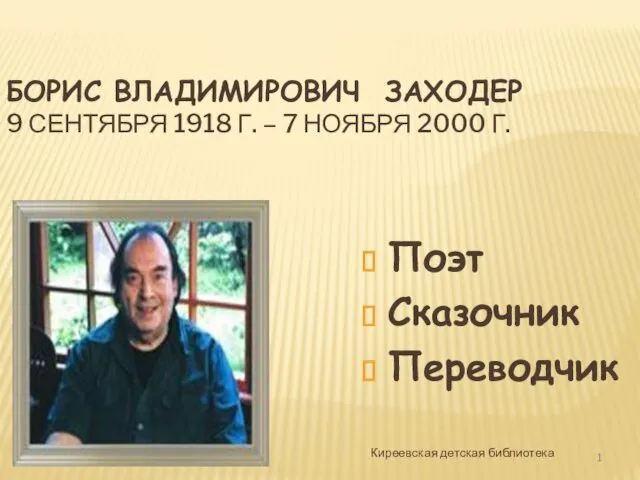

Lec_10 Борис Владимирович Заходер. Викторина

Борис Владимирович Заходер. Викторина Report on investments

Report on investments Творчество Жана Батиста Мольера. Жанр Высокой комедии

Творчество Жана Батиста Мольера. Жанр Высокой комедии Многоэтажные жилые дома

Многоэтажные жилые дома Массажный салон

Массажный салон Игровые технологии в начальной школе

Игровые технологии в начальной школе Стиль семейного воспитания как фактор формирования личности

Стиль семейного воспитания как фактор формирования личности Кольская сверхглубокая скважина

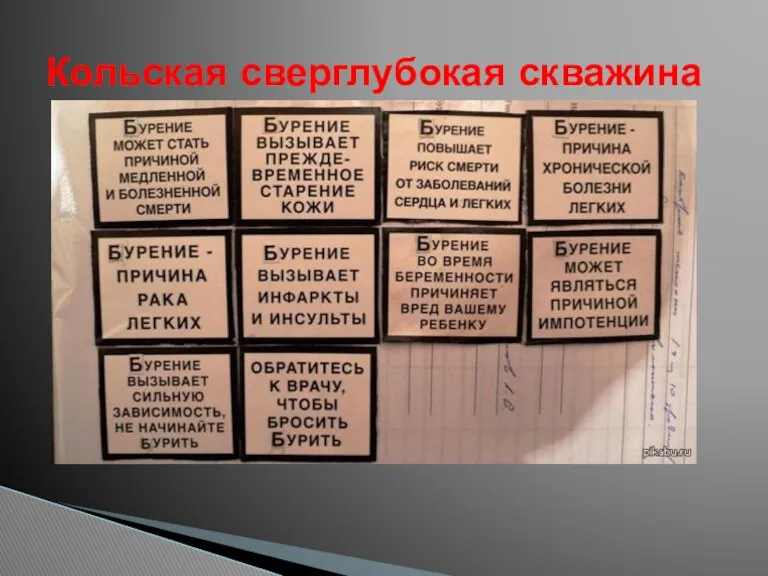

Кольская сверхглубокая скважина Физкультминутки (1)

Физкультминутки (1) Основные понятия в области качества. Потребительские свойства

Основные понятия в области качества. Потребительские свойства Интерактивная игра по ОПК Православие и живопись

Интерактивная игра по ОПК Православие и живопись Практическое занятие по русскому языку для педагогов, родителей, обучающихся.

Практическое занятие по русскому языку для педагогов, родителей, обучающихся. Електронний блок керування ДВЗ

Електронний блок керування ДВЗ Агробизнес-2020. 2020 жылға дейін мал азығы өндірісін дамыту бойынша кәсіби-жоспар

Агробизнес-2020. 2020 жылға дейін мал азығы өндірісін дамыту бойынша кәсіби-жоспар Цемент. История создания

Цемент. История создания Подготовка к ГИА. А15. Вычисление массовой доли химического элемента в веществе

Подготовка к ГИА. А15. Вычисление массовой доли химического элемента в веществе Тамақтану денсаулық факторы. Алиментарлық аурулар

Тамақтану денсаулық факторы. Алиментарлық аурулар How to Write a CV

How to Write a CV Пропедевтика. Эхокардиография (ЭХОКГ С ДКГ)

Пропедевтика. Эхокардиография (ЭХОКГ С ДКГ) Теоретико-графовые модели данных. Реляционная, многомерная, гибридная, виртуальная

Теоретико-графовые модели данных. Реляционная, многомерная, гибридная, виртуальная Презентация родительского собрания по теме Самооценка младшего школьника

Презентация родительского собрания по теме Самооценка младшего школьника Обеспечение надежности систем трубопроводного транспорта

Обеспечение надежности систем трубопроводного транспорта Современные здоровьесберегающие технологии используемые в работе с детьми.

Современные здоровьесберегающие технологии используемые в работе с детьми. Конный туризм и полевые выезды в России

Конный туризм и полевые выезды в России Жанна д’Арк

Жанна д’Арк Организация питания

Организация питания Сущность воспитания и его место в целостной структуре образовательного процесса

Сущность воспитания и его место в целостной структуре образовательного процесса