Слайд 2

Слайд 3

Слайд 4

Слайд 5

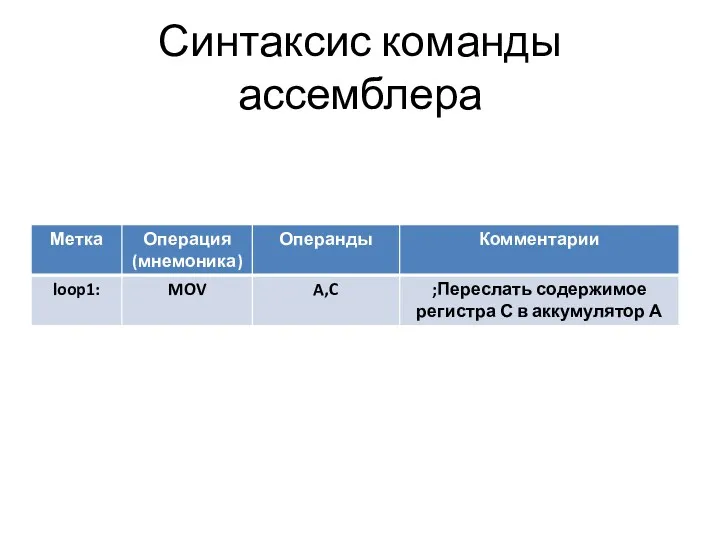

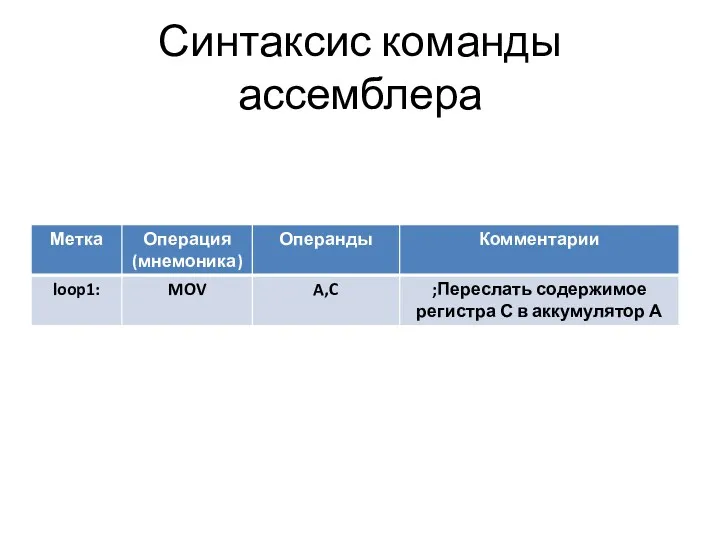

Синтаксис команды ассемблера

Слайд 6

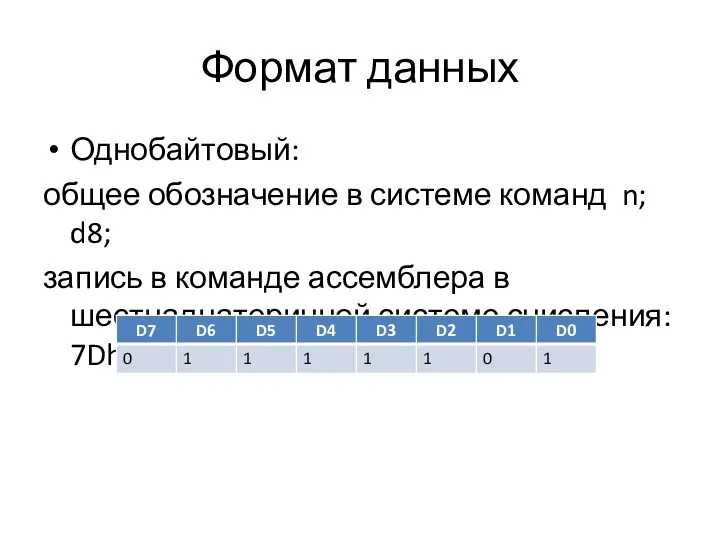

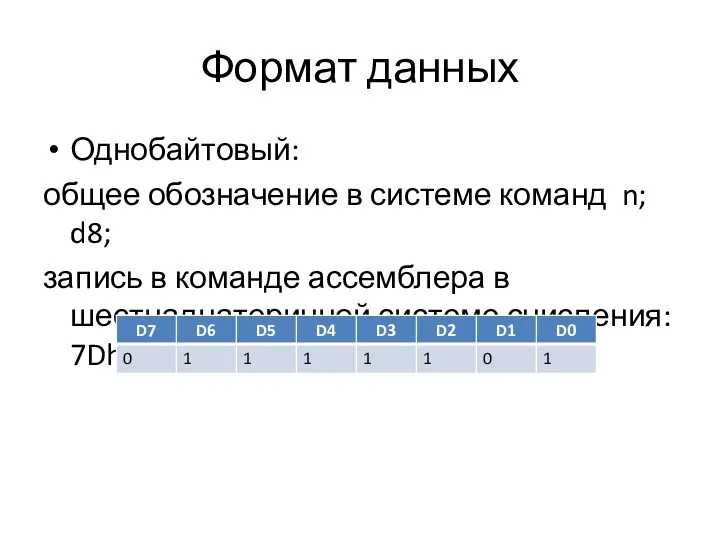

Формат данных

Однобайтовый:

общее обозначение в системе команд n; d8;

запись в команде

ассемблера в шестнадцатеричной системе счисления: 7Dh.

Слайд 7

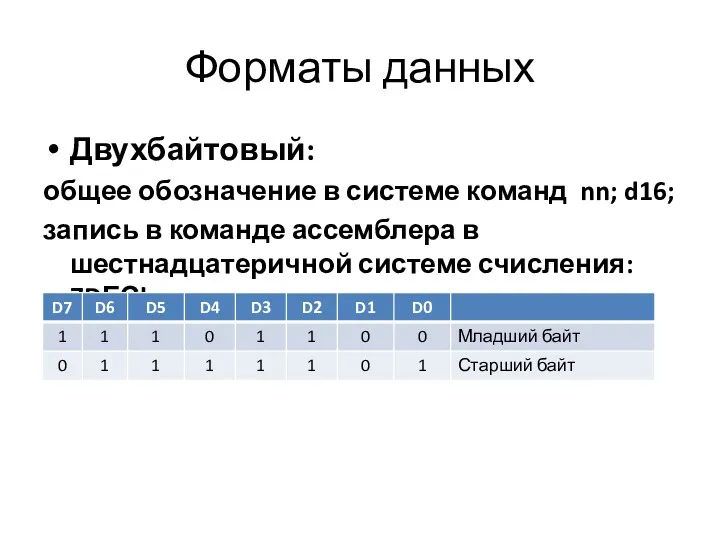

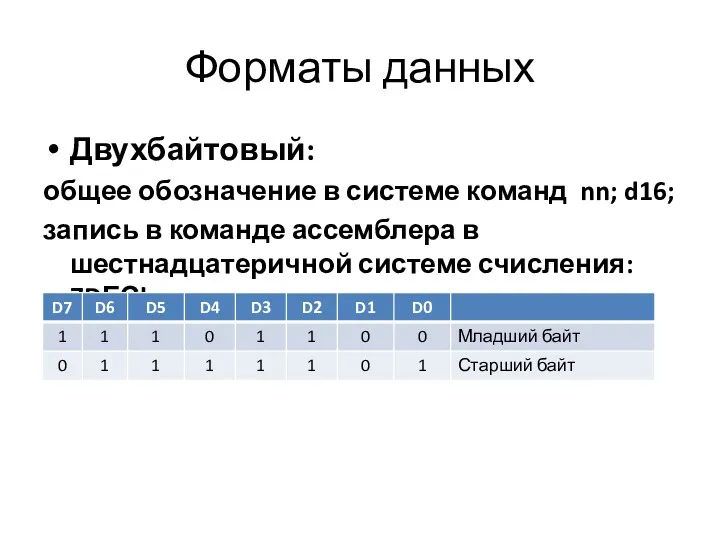

Форматы данных

Двухбайтовый:

общее обозначение в системе команд nn; d16;

запись в команде ассемблера

в шестнадцатеричной системе счисления: 7DЕСh.

Слайд 8

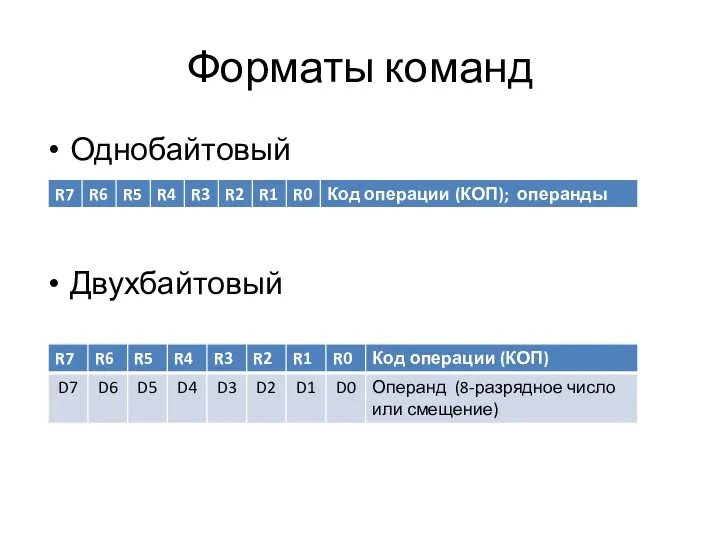

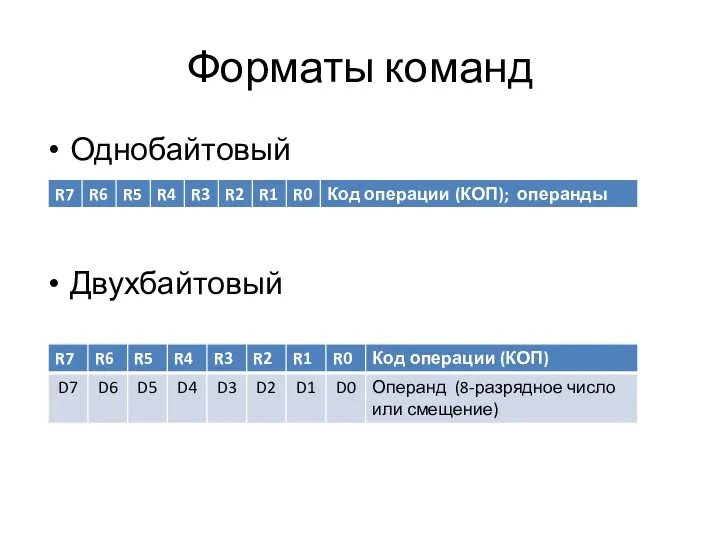

Форматы команд

Однобайтовый

Двухбайтовый

Слайд 9

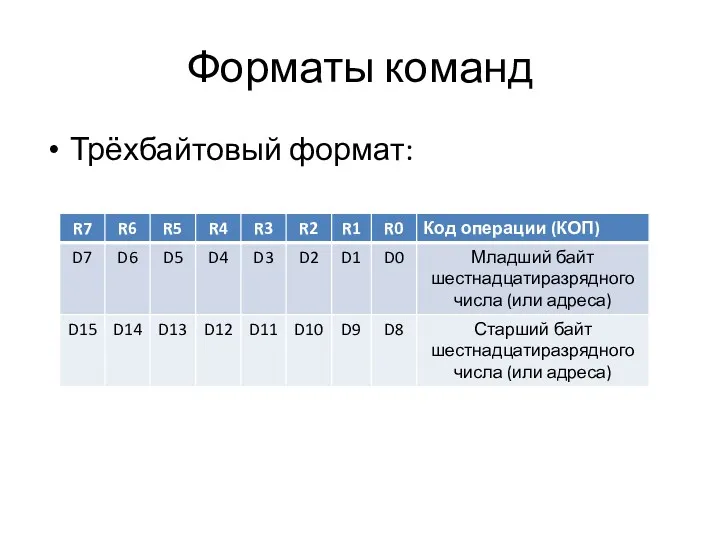

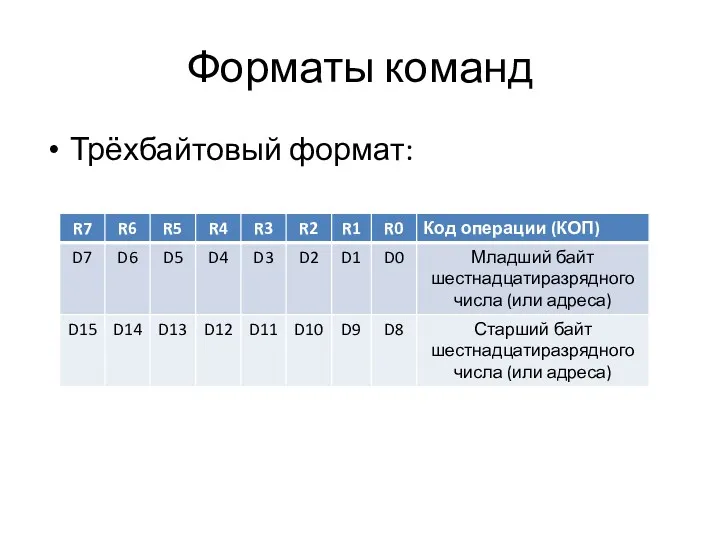

Форматы команд

Трёхбайтовый формат:

Слайд 10

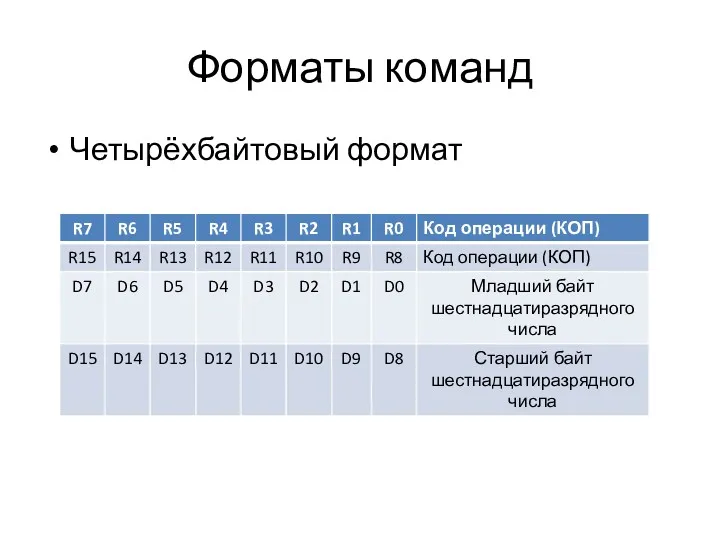

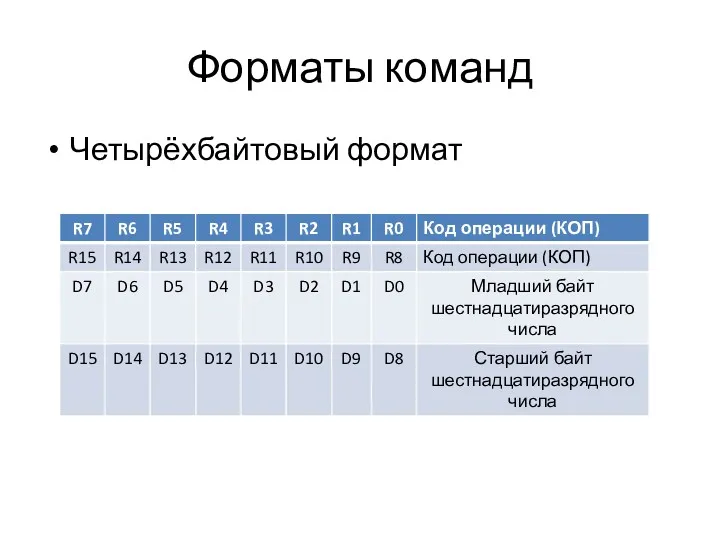

Форматы команд

Четырёхбайтовый формат

Слайд 11

Адресация операндов

Непосредственная;

Регистровая;

Косвенная;

Относительная;

Индексная;

Битовая;

Встроенная;

Смешанная.

Слайд 12

Система команд

Команды пересылки;

Арифметические и логические операции;

Команды условных и безусловных переходов;

Команды вызова

подпрограмм и возврата из подпрограмм;

Команды ввода-вывода;

Команды циклических сдвигов;

Команды операций с битами;

Прочие.

Слайд 13

Команды пересылки

LD a,b

LD - переслать

a – приемник

b – источник

Слайд 14

Арифметические команды

АDD (ADC) – арифметические сложение;

SUB (SBC) – арифметическое вычитание;

INC –

увеличение на единицу;

DEC – уменьшение на единицу;

СР – сравнение.

Слайд 15

Логические команды

АND – «И»

OR – «ИЛИ»

XOR – «исключающее ИЛИ»

CPL – инверсия

каждого из разрядов А

NEG – изменение знака содержимого А

Слайд 16

Команды переходов

JP – переход по адресу ячейки памяти

JR – переход с

учетом 8-разрядного смещения

JP Z – проверяется значение флага Z, если оно равно нулю, осуществляется переход

JP NZ - проверяется значение флага Z, если оно не равно нулю, осуществляется переход

Слайд 17

Команды вызова и возврата

CALL – вызов подпрограммы

RET – возврат из подпрограммы

PUSH

– загрузка данных в стек

POP – считывание данных из стека

Слайд 18

Команды ввода-вывода

IN – содержимое порта ввода загружается в регистр А

OUT –

содержимое регистра А пересылается в порт вывода

Слайд 19

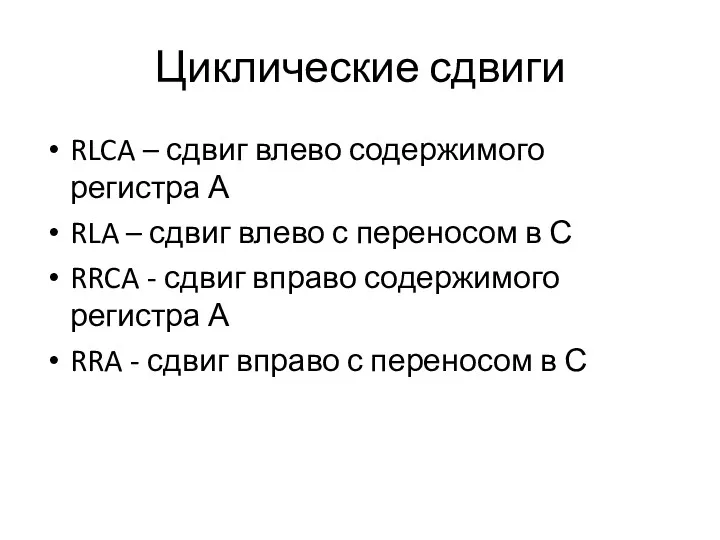

Циклические сдвиги

RLCA – сдвиг влево содержимого регистра А

RLA – сдвиг влево

с переносом в С

RRCA - сдвиг вправо содержимого регистра А

RRA - сдвиг вправо с переносом в С

Слайд 20

Операции с битами

BIT – инверсия бита

SET – запись единицы в

бит

Семиотика поражения дыхательной системы у детей. Пропедевтика детских болезней

Семиотика поражения дыхательной системы у детей. Пропедевтика детских болезней Балалық шақтағы қан жасау органдарының анатомофизиологиялық ерекшелігі визуальды диагностикасы

Балалық шақтағы қан жасау органдарының анатомофизиологиялық ерекшелігі визуальды диагностикасы Как подготовиться к поступлению в 5 класс лицея. Математика

Как подготовиться к поступлению в 5 класс лицея. Математика Мышцы спины

Мышцы спины Размещение газодобывающей и газоперербатывающей промышленности

Размещение газодобывающей и газоперербатывающей промышленности Психологические особенности детей группы риска

Психологические особенности детей группы риска Болота

Болота Электрлік кабельдер

Электрлік кабельдер Маркетинг и общество

Маркетинг и общество Дикие животные Якутии

Дикие животные Якутии Причастные/деепричастные обороты (Задание 8)

Причастные/деепричастные обороты (Задание 8) Любимому мужу на день рождения. Фото

Любимому мужу на день рождения. Фото Теория фирмы

Теория фирмы Гадание на рунах

Гадание на рунах PR в интернете

PR в интернете Устройство судна

Устройство судна Просто о главном. ФГОС

Просто о главном. ФГОС Неврология. Анатомия и физиология нервной системы

Неврология. Анатомия и физиология нервной системы Компоненты интенсивной терапии

Компоненты интенсивной терапии мультик

мультик Карл Линней (1707-1778)

Карл Линней (1707-1778) III муниципальный фотокросс Золотой объектив! сентябрь 2019 г

III муниципальный фотокросс Золотой объектив! сентябрь 2019 г Сборник стихов Н.А. Некрасова

Сборник стихов Н.А. Некрасова Сущность и особенности административного надзора. Прокурорский надзор

Сущность и особенности административного надзора. Прокурорский надзор Administratīvais process

Administratīvais process История СНК кафедры

История СНК кафедры Тигровая акула

Тигровая акула План мероприятий Молодежного добровольческого центра

План мероприятий Молодежного добровольческого центра