Содержание

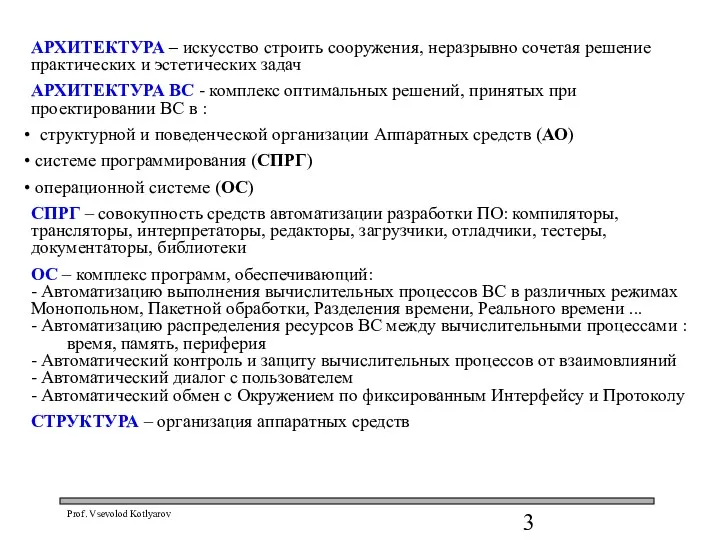

- 3. АРХИТЕКТУРА – искусство строить сооружения, неразрывно сочетая решение практических и эстетических задач АРХИТЕКТУРА ВС - комплекс

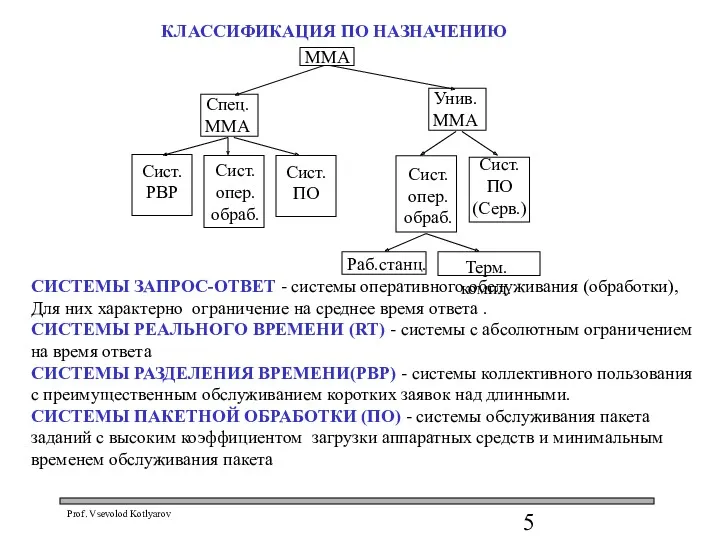

- 5. КЛАССИФИКАЦИЯ ПО НАЗНАЧЕНИЮ СИСТЕМЫ ЗАПРОС-ОТВЕТ - системы оперативного обслуживания (обработки), Для них характерно ограничение на среднее

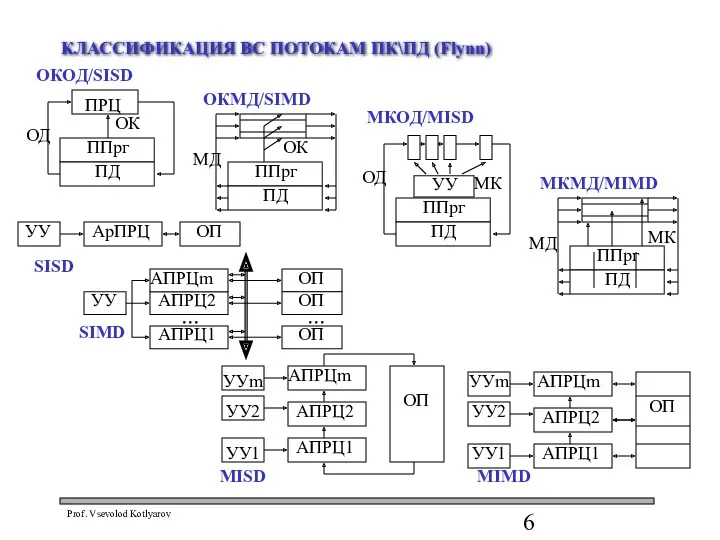

- 6. КЛАССИФИКАЦИЯ ВС ПОТОКАМ ПК\ПД (Flynn)

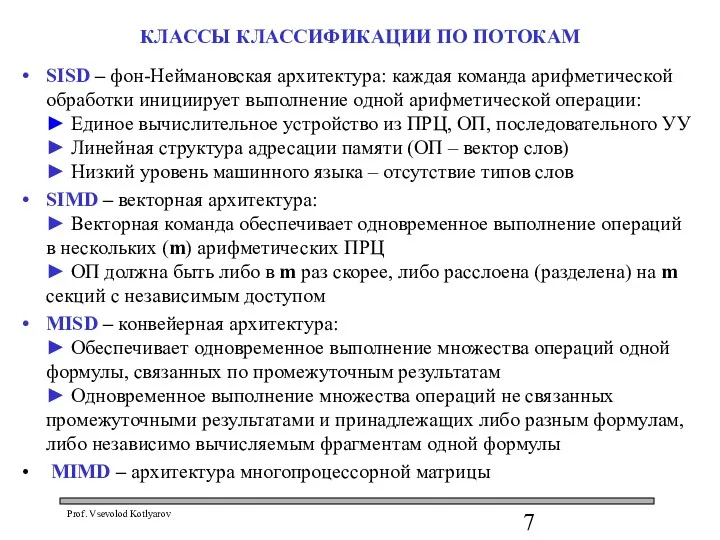

- 7. КЛАССЫ КЛАССИФИКАЦИИ ПО ПОТОКАМ SISD – фон-Неймановская архитектура: каждая команда арифметической обработки инициирует выполнение одной арифметической

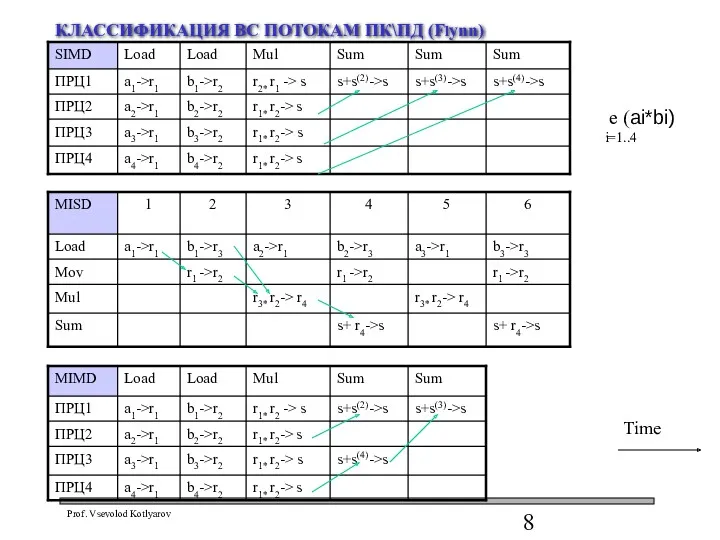

- 8. КЛАССИФИКАЦИЯ ВС ПОТОКАМ ПК\ПД (Flynn) Time е (ai*bi) i=1..4

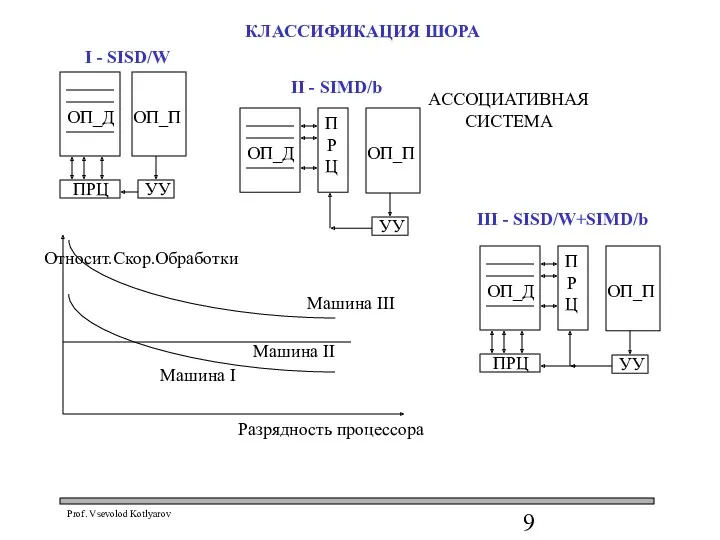

- 9. КЛАССИФИКАЦИЯ ШОРА

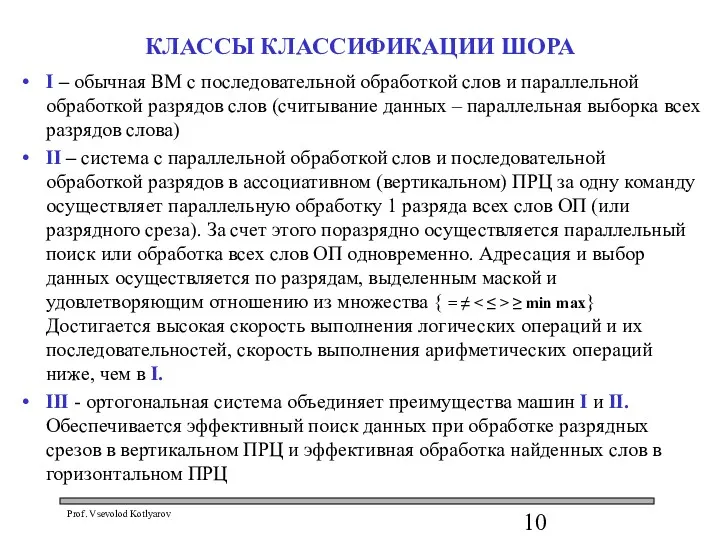

- 10. КЛАССЫ КЛАССИФИКАЦИИ ШОРА I – обычная ВМ с последовательной обработкой слов и параллельной обработкой разрядов слов

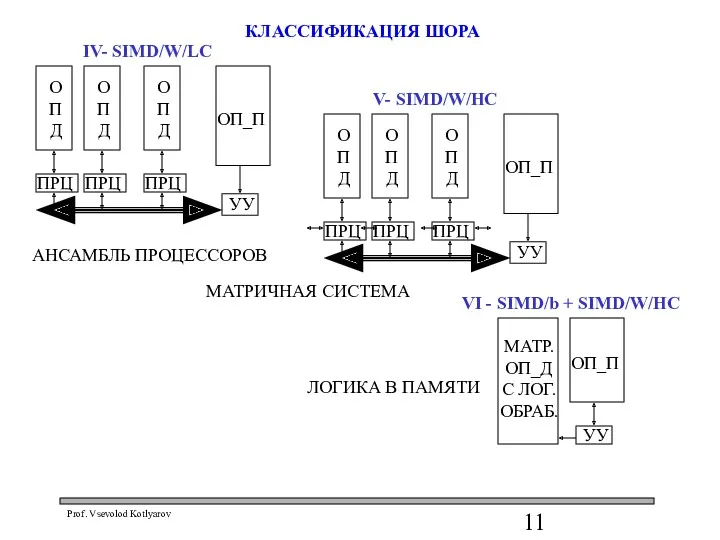

- 11. КЛАССИФИКАЦИЯ ШОРА

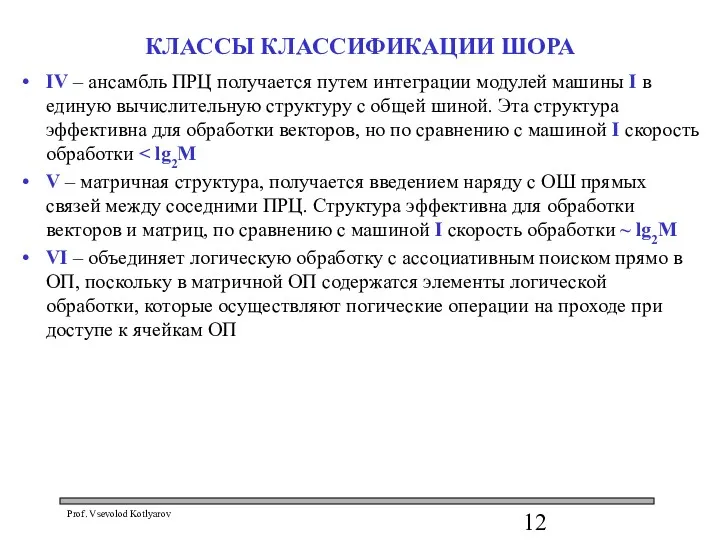

- 12. КЛАССЫ КЛАССИФИКАЦИИ ШОРА IV – ансамбль ПРЦ получается путем интеграции модулей машины I в единую вычислительную

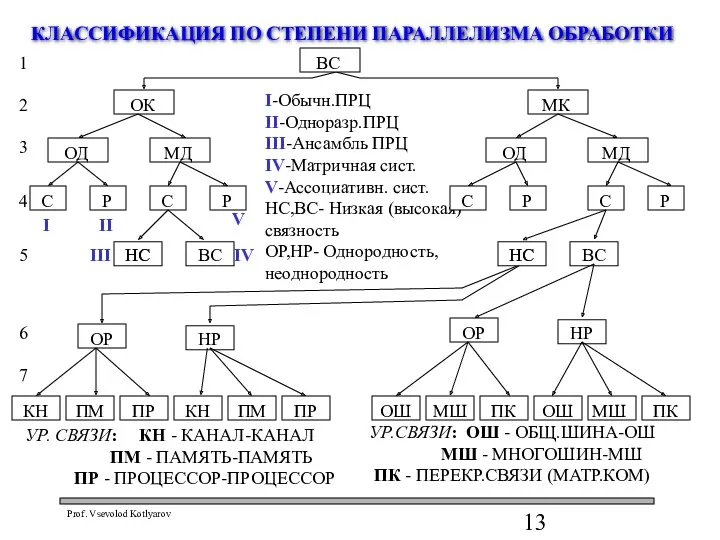

- 13. КЛАССИФИКАЦИЯ ПО СТЕПЕНИ ПАРАЛЛЕЛИЗМА ОБРАБОТКИ 1 2 3 4 5 6 7 I-Обычн.ПРЦ II-Одноразр.ПРЦ III-Ансамбль ПРЦ

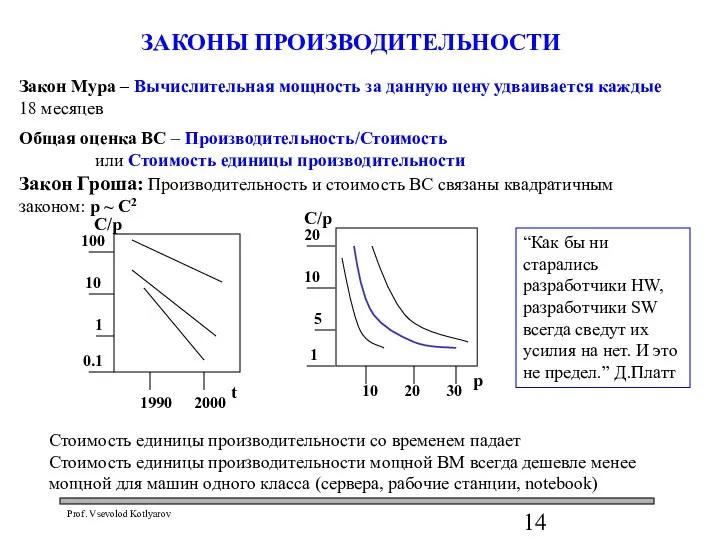

- 14. Закон Гроша: Производительность и стоимость ВС связаны квадратичным законом: p ~ C2 C/p Закон Мура –

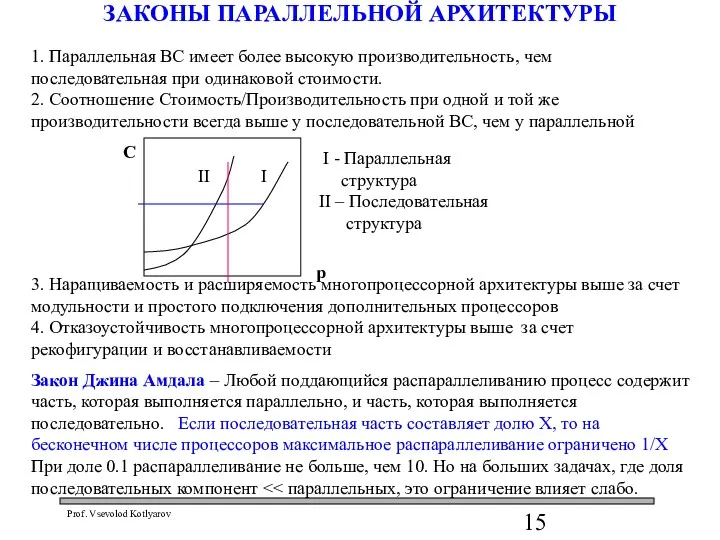

- 15. ЗАКОНЫ ПАРАЛЛЕЛЬНОЙ АРХИТЕКТУРЫ 1. Параллельная ВС имеет более высокую производительность, чем последовательная при одинаковой стоимости. 2.

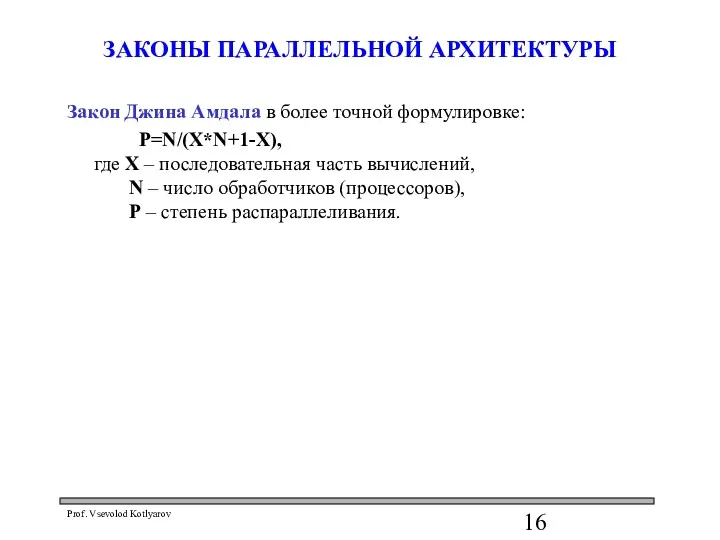

- 16. ЗАКОНЫ ПАРАЛЛЕЛЬНОЙ АРХИТЕКТУРЫ Закон Джина Амдала в более точной формулировке: P=N/(X*N+1-X), где X – последовательная часть

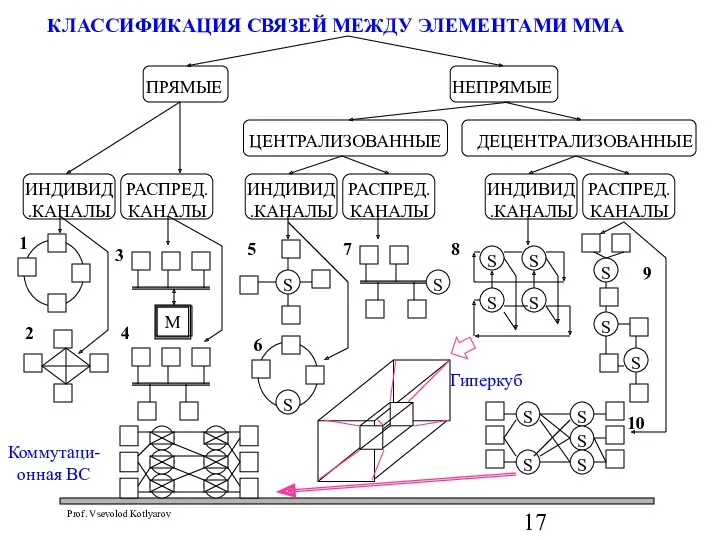

- 17. КЛАССИФИКАЦИЯ СВЯЗЕЙ МЕЖДУ ЭЛЕМЕНТАМИ ММА

- 18. КЛАССИФИКАЦИЯ СВЯЗЕЙ МЕЖДУ ЭЛЕМЕНТАМИ ММА

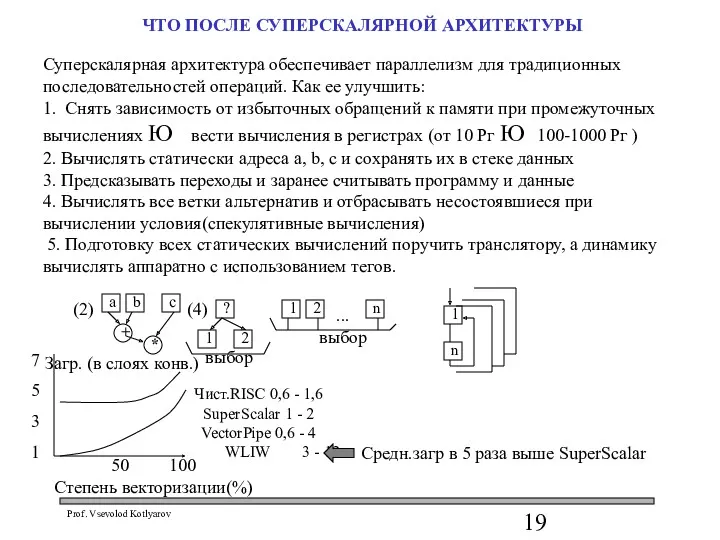

- 19. ЧТО ПОСЛЕ СУПЕРСКАЛЯРНОЙ АРХИТЕКТУРЫ Суперскалярная архитектура обеспечивает параллелизм для традиционных последовательностей операций. Как ее улучшить: 1.

- 20. ЧТО ПОСЛЕ СУПЕРСКАЛЯРНОЙ АРХИТЕКТУРЫ СУПЕРСКАЛЯРНУЮ АРХИТЕКТУРУ сменит Мультимашинная (MultyСore)

- 25. Тест 1 Найти в интернете и распечатать описания архитектур современных ВС известных фирм: Intel Sun IBM

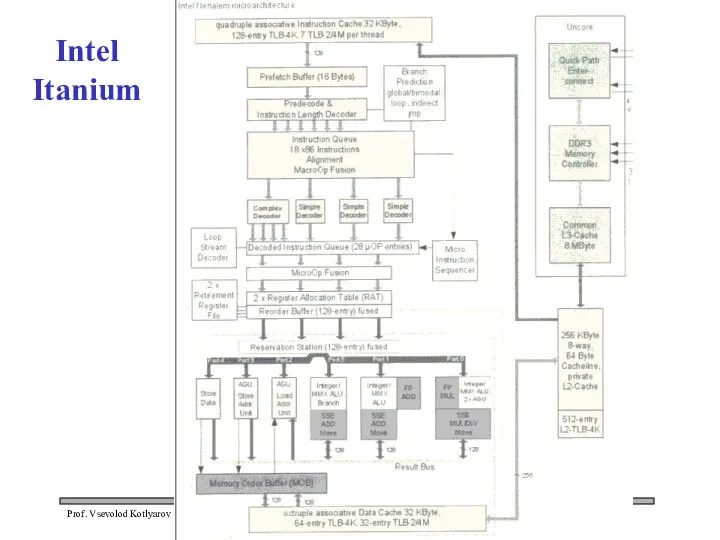

- 26. Intel Itanium

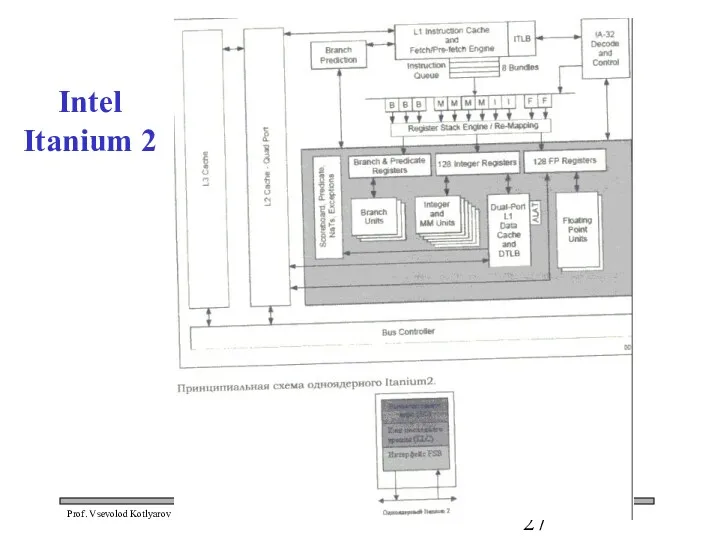

- 27. Intel Itanium 2

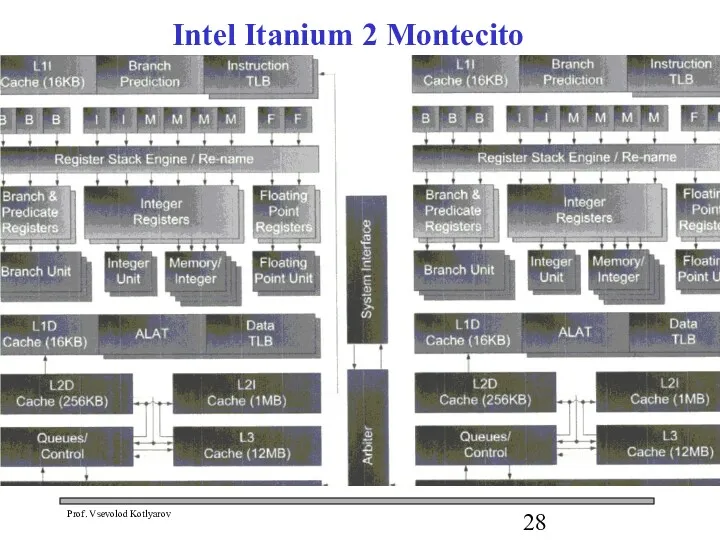

- 28. Intel Itanium 2 Montecito

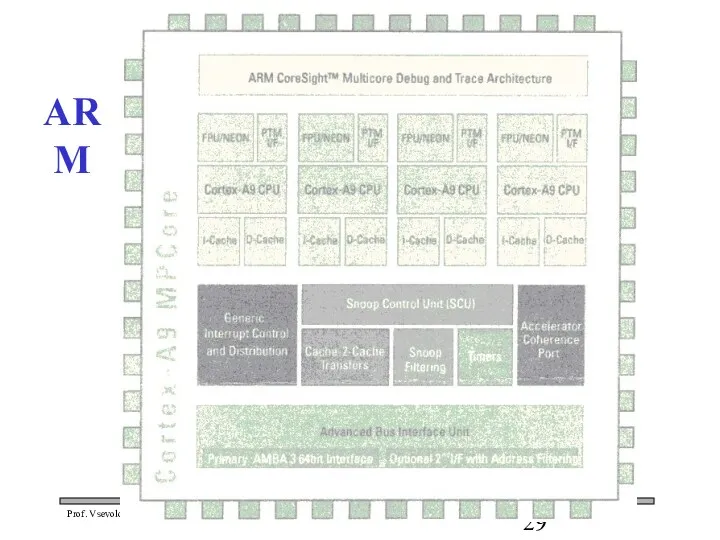

- 29. ARM

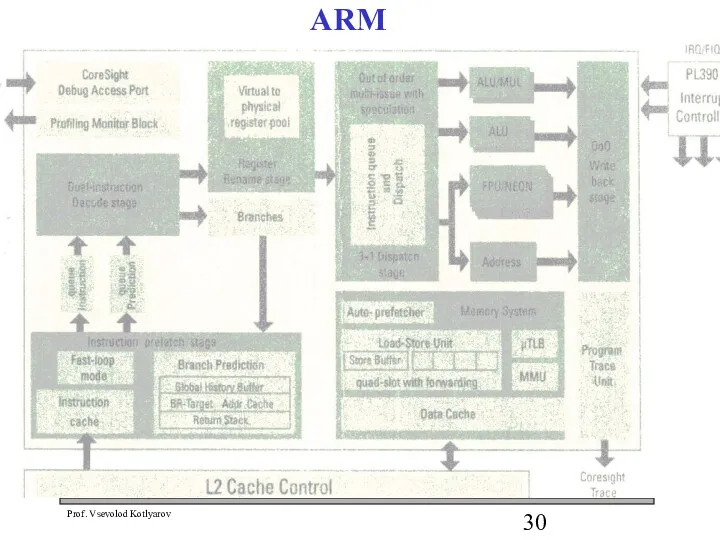

- 30. ARM

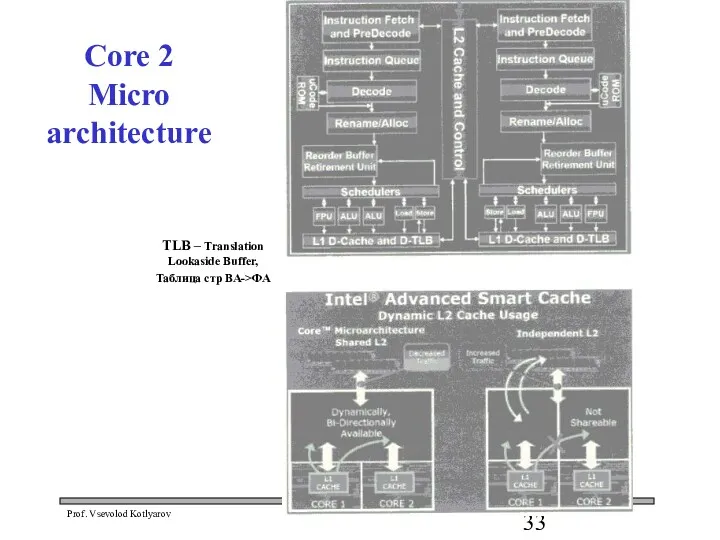

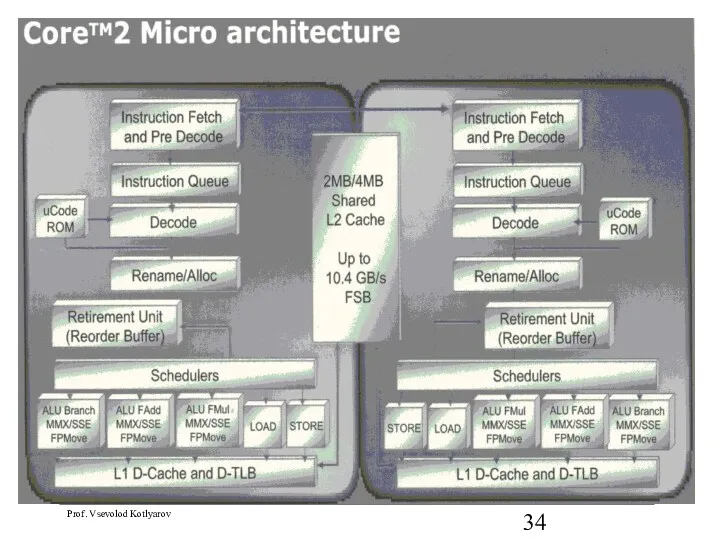

- 33. Core 2 Micro architecture TLB – Translation Lookaside Buffer, Таблица стр ВА->ФА

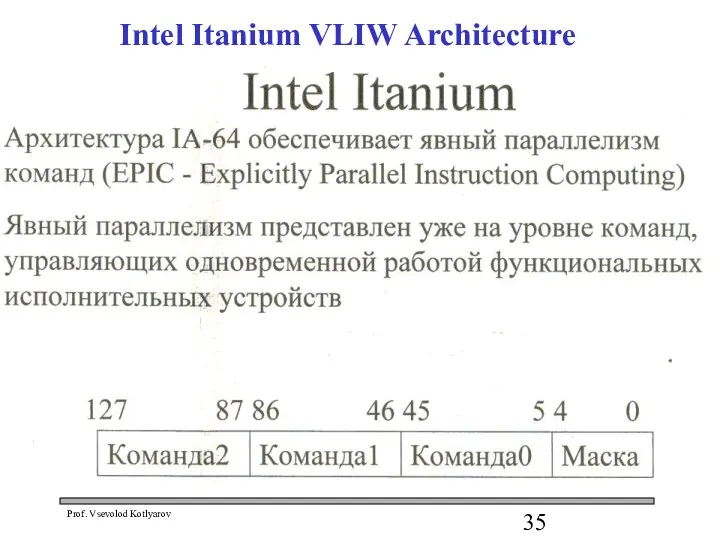

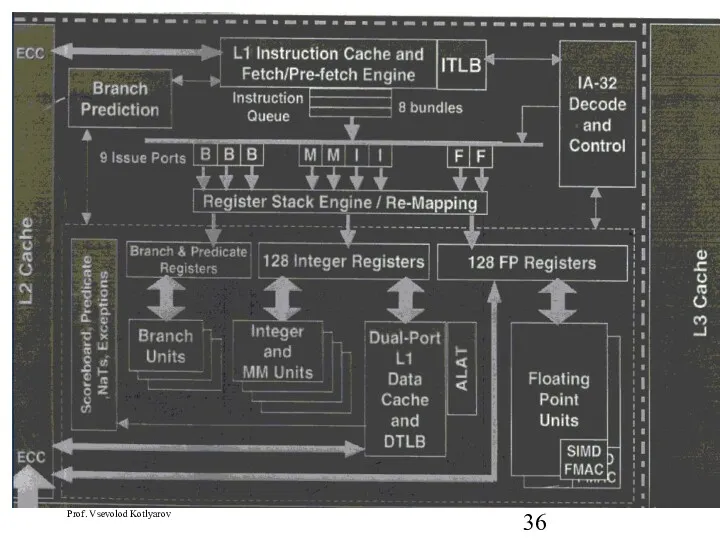

- 35. Intel Itanium VLIW Architecture

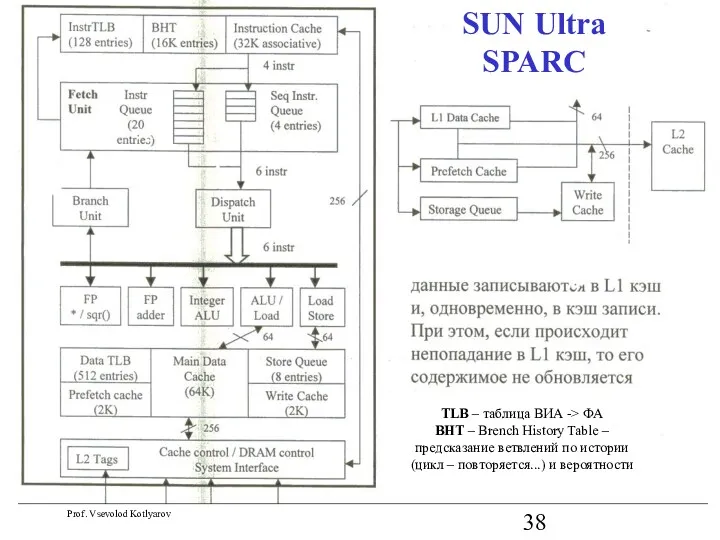

- 38. SUN Ultra SPARC SUN Ultra SPARC TLB – таблица ВИА -> ФА BHT – Brench History

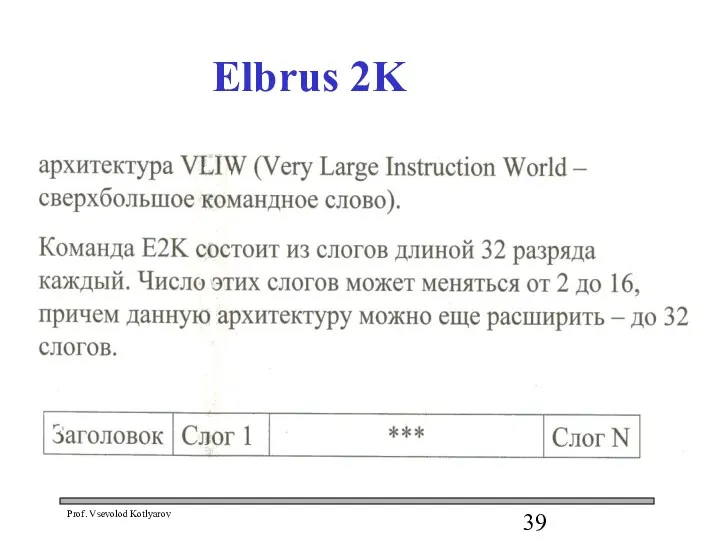

- 39. Elbrus 2K

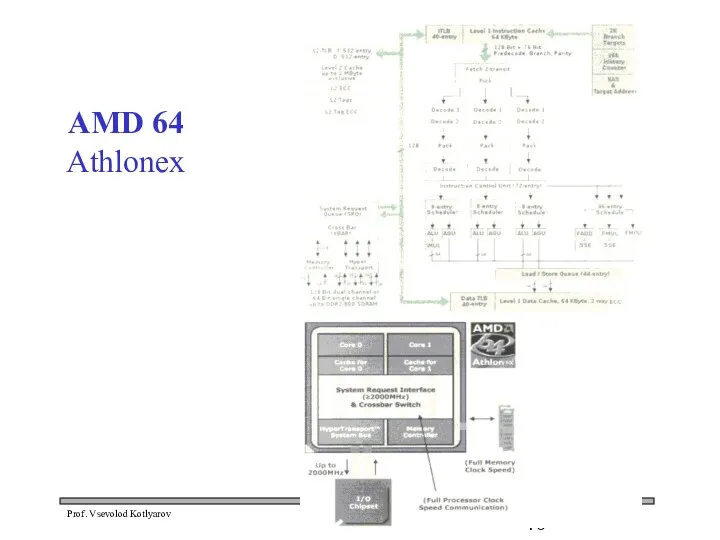

- 40. AMD 64 Athlonex

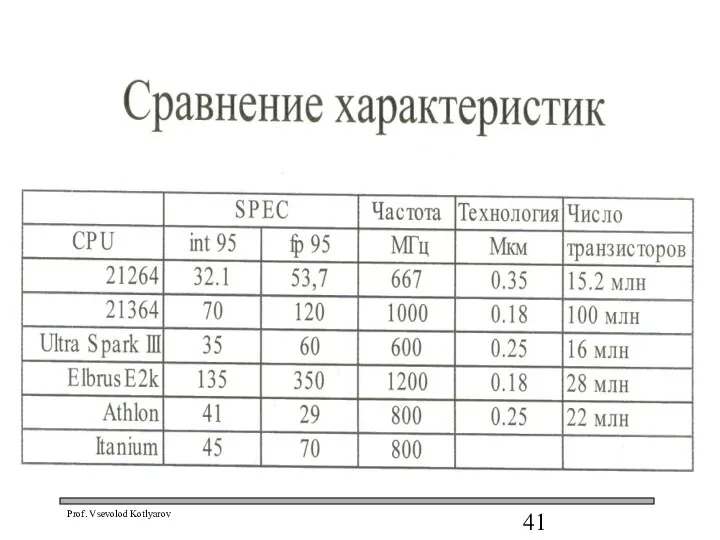

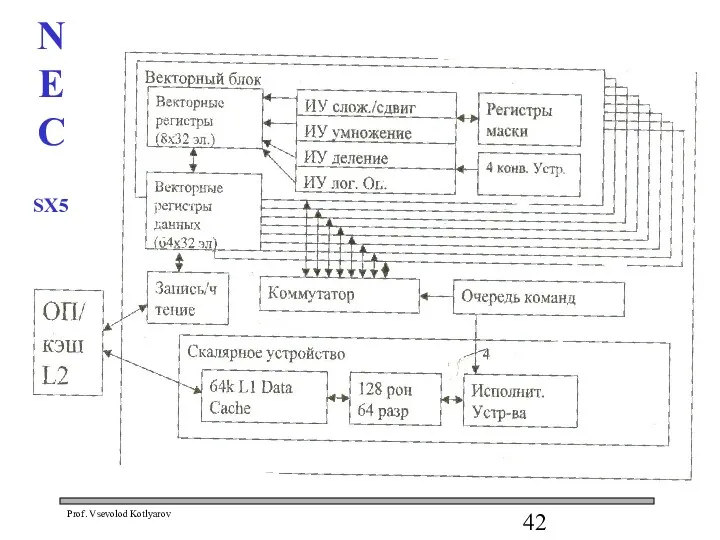

- 42. NEC SX5

- 44. Скачать презентацию

Возникновение социологии как науки

Возникновение социологии как науки С днём рождения

С днём рождения Особенности УМК ОС Школа 2100 или как помочь ребенку, который будет учиться по стандартам нового поколения

Особенности УМК ОС Школа 2100 или как помочь ребенку, который будет учиться по стандартам нового поколения Презентация Самые интересные факты о птицах.

Презентация Самые интересные факты о птицах. ПРЕЗЕНТАЦИЯ НА ТЕМУ: ЕВРОПА - ОБЩАЯ ХАРАКТЕРИСТИКА

ПРЕЗЕНТАЦИЯ НА ТЕМУ: ЕВРОПА - ОБЩАЯ ХАРАКТЕРИСТИКА Презентация слайдов к уроку географии в 11 классе Хозяйство Японии

Презентация слайдов к уроку географии в 11 классе Хозяйство Японии Водоснабжение и водоотведение

Водоснабжение и водоотведение Звонкие и глухие звуки в словах

Звонкие и глухие звуки в словах Оптоэлектронные приборы

Оптоэлектронные приборы Музыка утра

Музыка утра секты и социальная безопасность

секты и социальная безопасность Бедность и богатство

Бедность и богатство Рельеф и полезные ископаемые Южной Америки

Рельеф и полезные ископаемые Южной Америки Социальные нормы

Социальные нормы Противоэпидемические мероприятия в очагах с фекальнооральным механизмом передачи

Противоэпидемические мероприятия в очагах с фекальнооральным механизмом передачи Татар теленнән дәрес эшкәртмәсе (4 сыйныф). Сыйфат сүз төркеме.

Татар теленнән дәрес эшкәртмәсе (4 сыйныф). Сыйфат сүз төркеме. 13 примеров губительного влияния человека на природу

13 примеров губительного влияния человека на природу Объяснение электрических явлений

Объяснение электрических явлений Расследование грабежей, совершенных в условиях города (161 УК РФ)

Расследование грабежей, совершенных в условиях города (161 УК РФ) Организационная структура ВС РФ. Виды и рода ВС РФ

Организационная структура ВС РФ. Виды и рода ВС РФ ООО Типографский комплекс Девиз

ООО Типографский комплекс Девиз Презентация Мой крайдля учащихся начальной школы.

Презентация Мой крайдля учащихся начальной школы. Анализ состояния системы образования и пути ее совершенствования

Анализ состояния системы образования и пути ее совершенствования Электрические аппараты электровозов. Классификация

Электрические аппараты электровозов. Классификация презентация к уроку по теме Азотная кислота

презентация к уроку по теме Азотная кислота Технический анализ финансовых рынков

Технический анализ финансовых рынков Русь сказочная

Русь сказочная Презентация Дидактические приемы

Презентация Дидактические приемы