Содержание

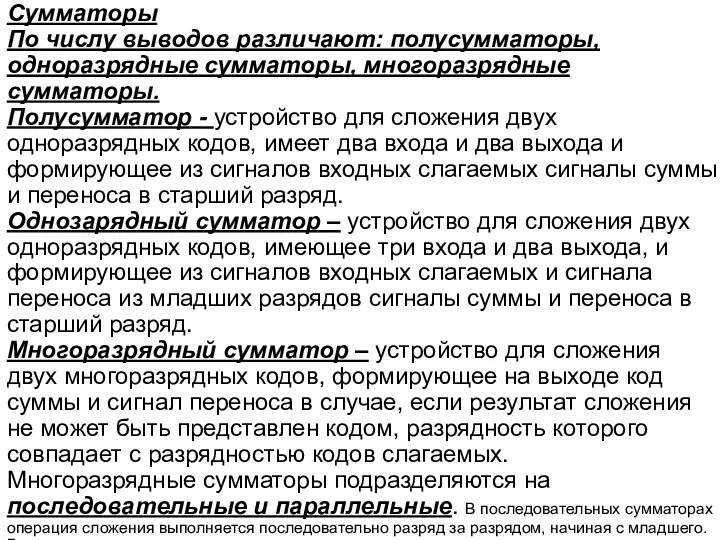

- 2. Сумматоры По числу выводов различают: полусумматоры, одноразрядные сумматоры, многоразрядные сумматоры. Полусумматор - устройство для сложения двух

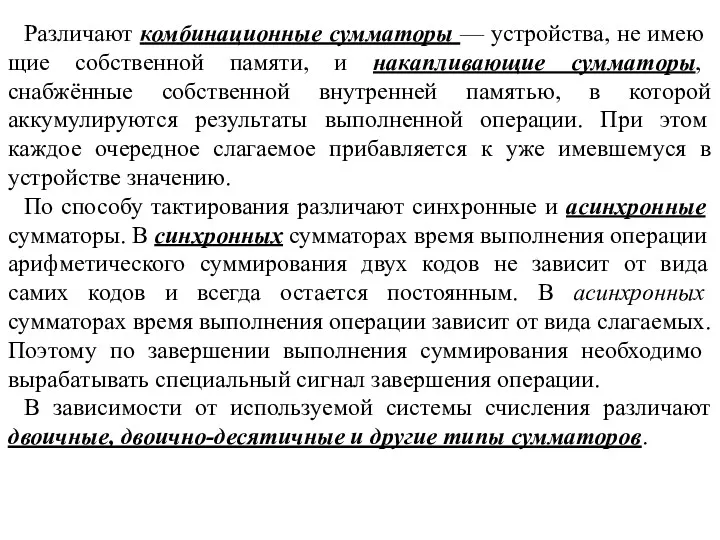

- 3. Различают комбинационные сумматоры — устройства, не имеющие собственной памяти, и накапливающие сумматоры, снабжённые собственной внутренней памятью,

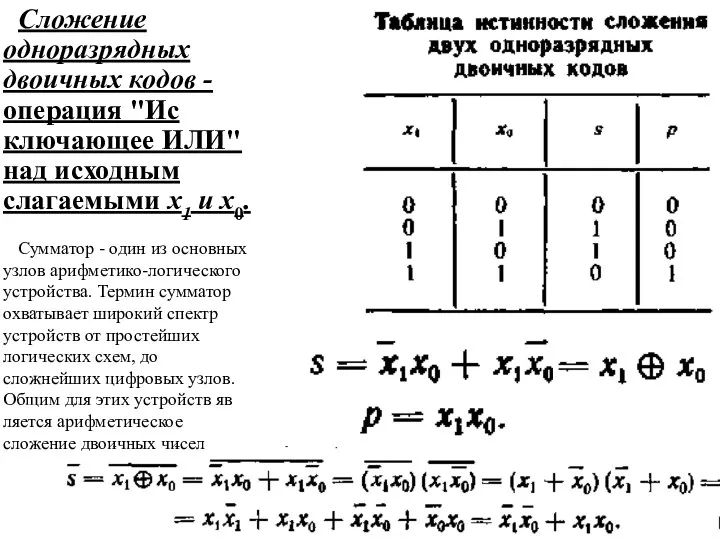

- 4. Сложение одноразрядных двоичных кодов - операция "Исключающее ИЛИ" над исходным слагаемыми х1 и x0. Сумматор -

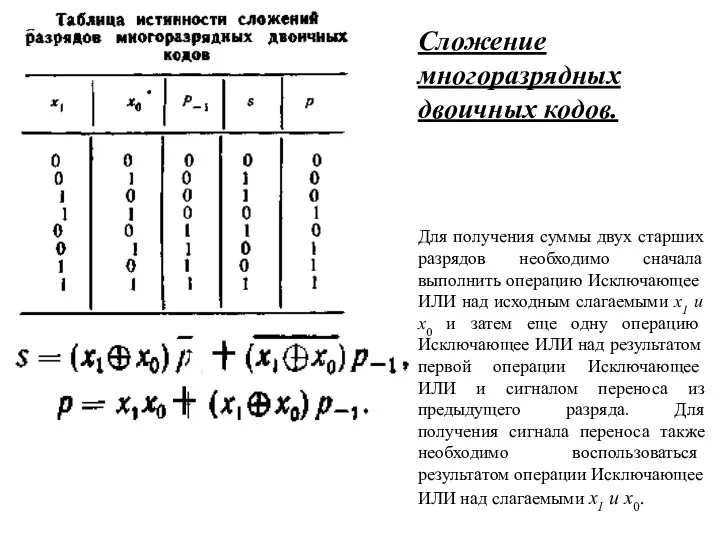

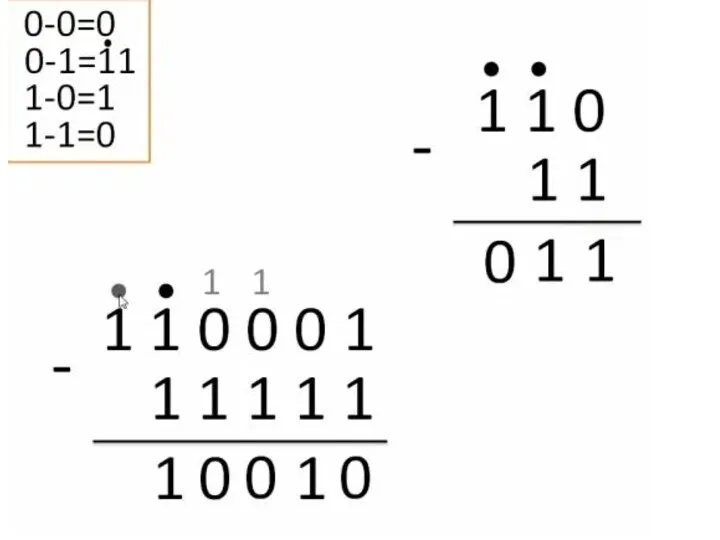

- 5. Сложение многоразрядных двоичных кодов. Для получения суммы двух старших разрядов необходимо сначала выполнить операцию Исключающее ИЛИ

- 6. Структурная схема реализации двоичного полусумматора х0 ДВОИЧНЫИ ПОЛУСУММАТОР - устройство сложения двух одноразрядных кодов, имеет два

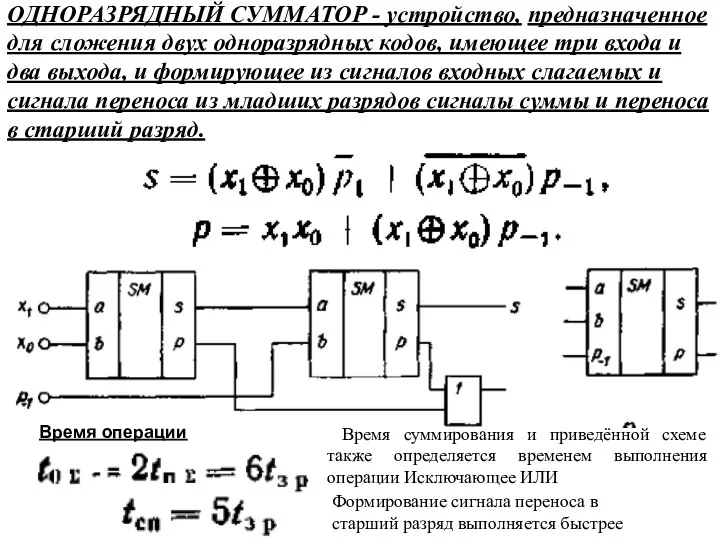

- 7. ОДНОРАЗРЯДНЫЙ СУММАТОР - устройство, предназначенное для сложения двух одноразрядных кодов, имеющее три входа и два выхода,

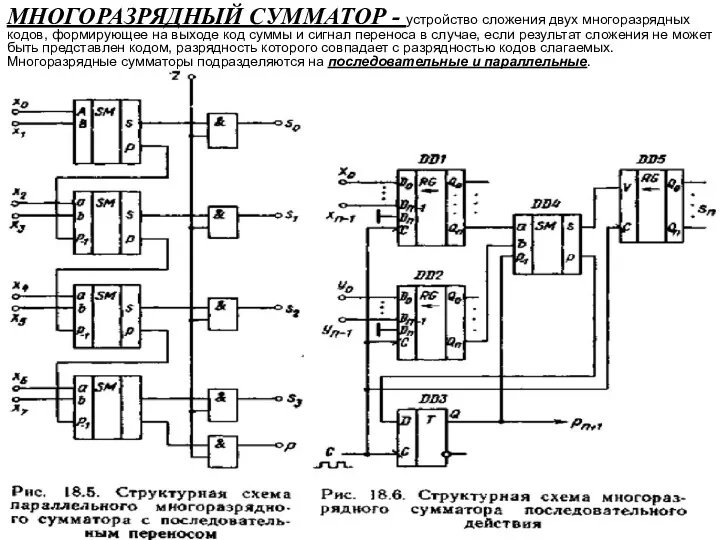

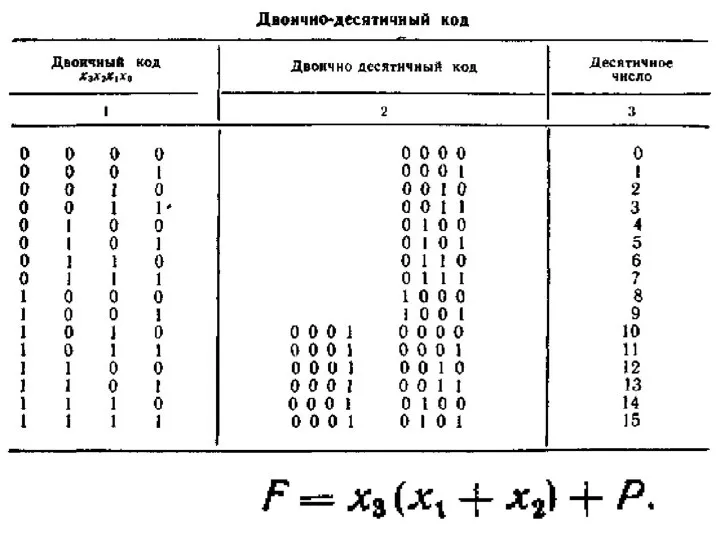

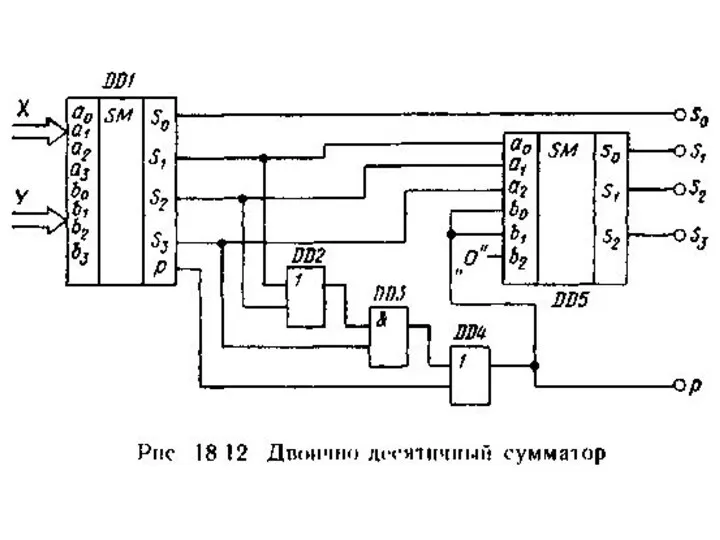

- 8. МНОГОРАЗРЯДНЫЙ СУММАТОР - устройство сложения двух многоразрядных кодов, формирующее на выходе код суммы и сигнал переноса

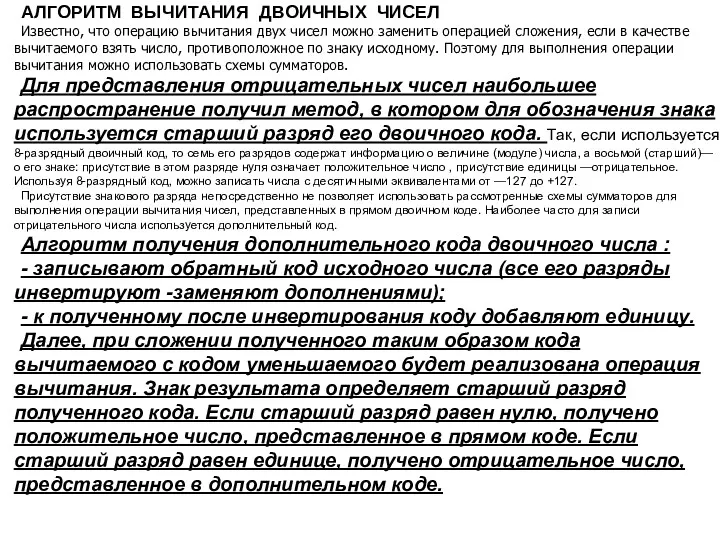

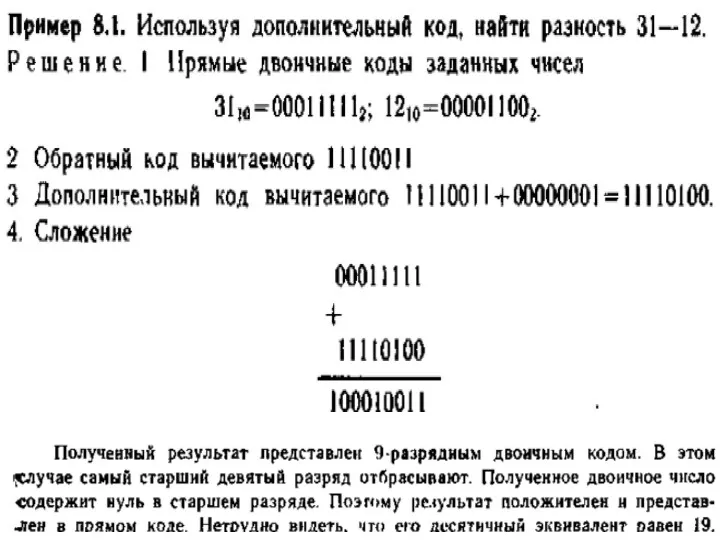

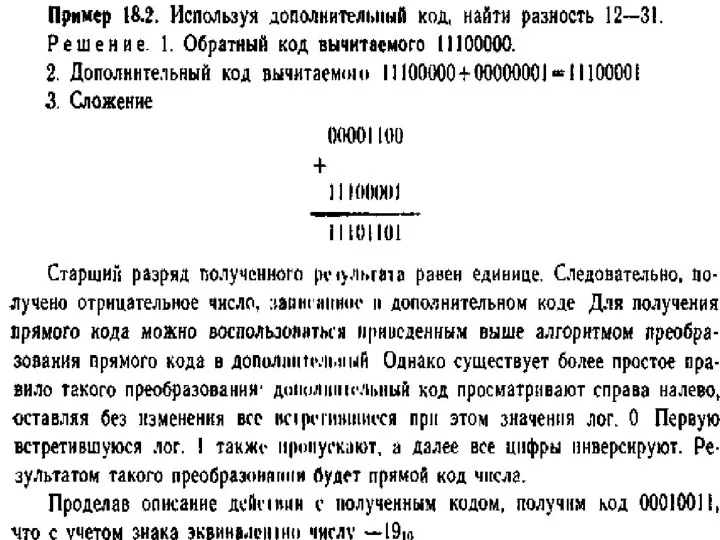

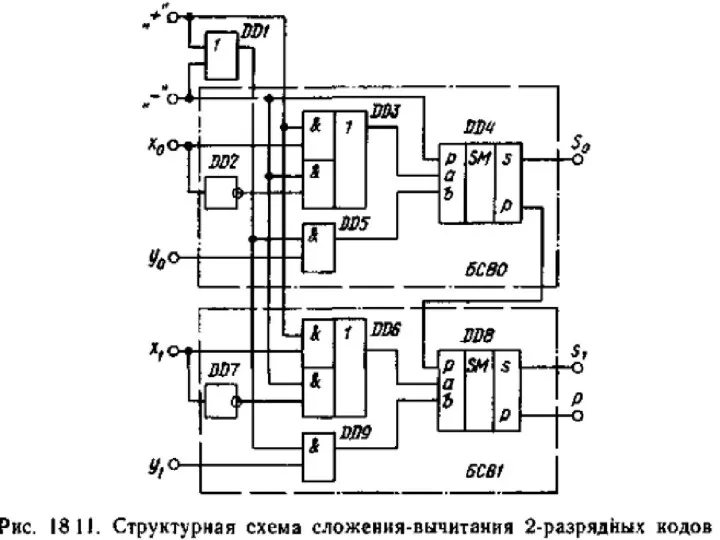

- 12. АЛГОРИТМ ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ Известно, что операцию вычитания двух чисел можно заменить операцией сложения, если в

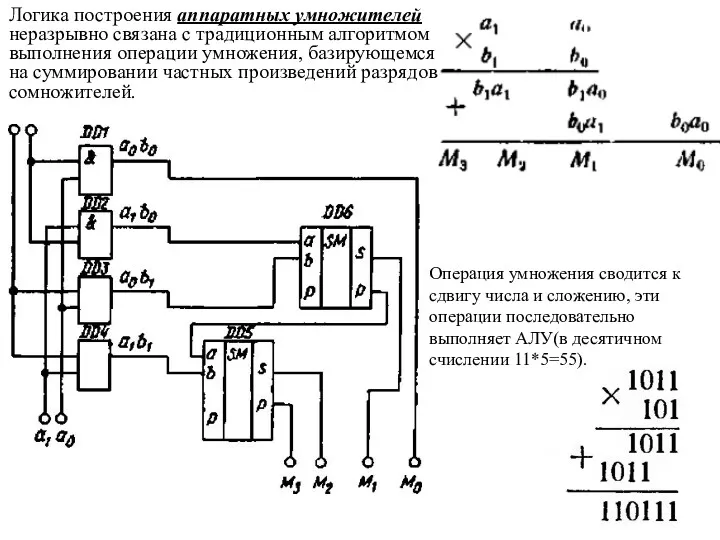

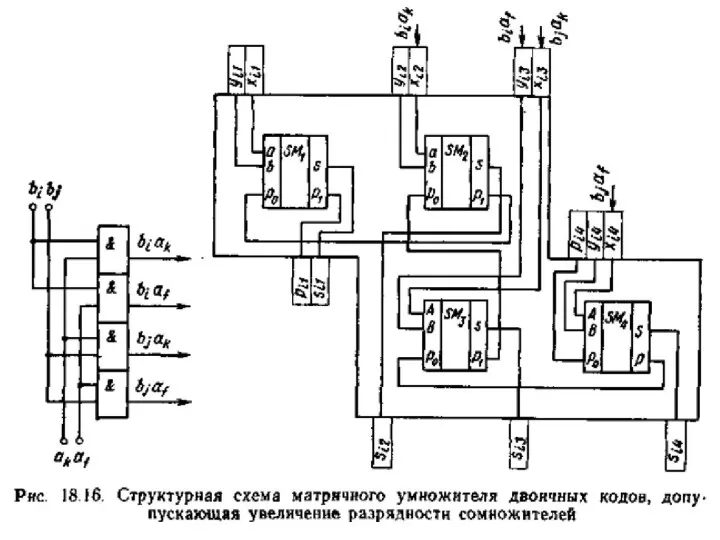

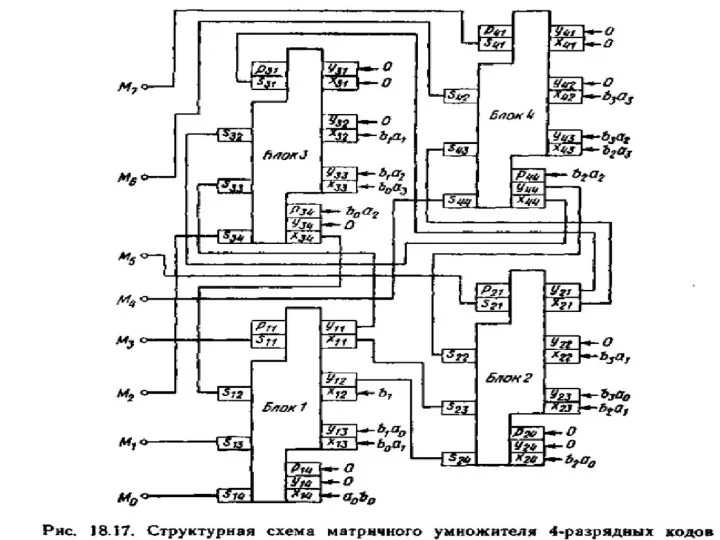

- 17. Логика построения аппаратных умножителей неразрывно связана с традиционным алгоритмом выполнения операции умножения, базирующемся на суммировании частных

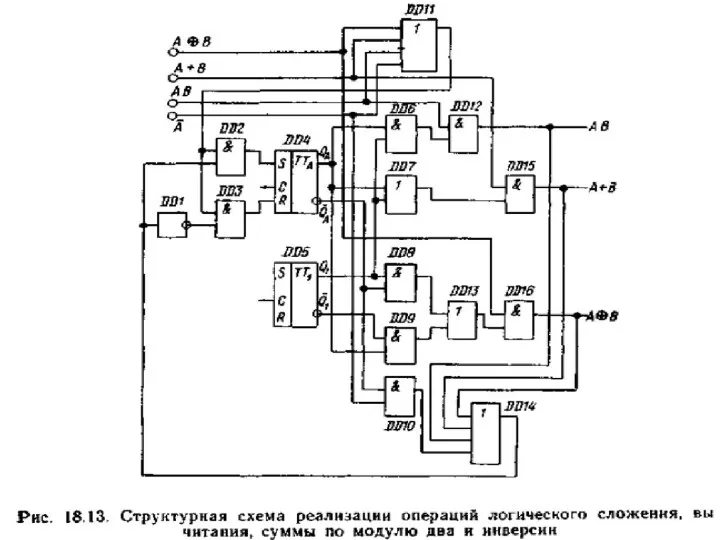

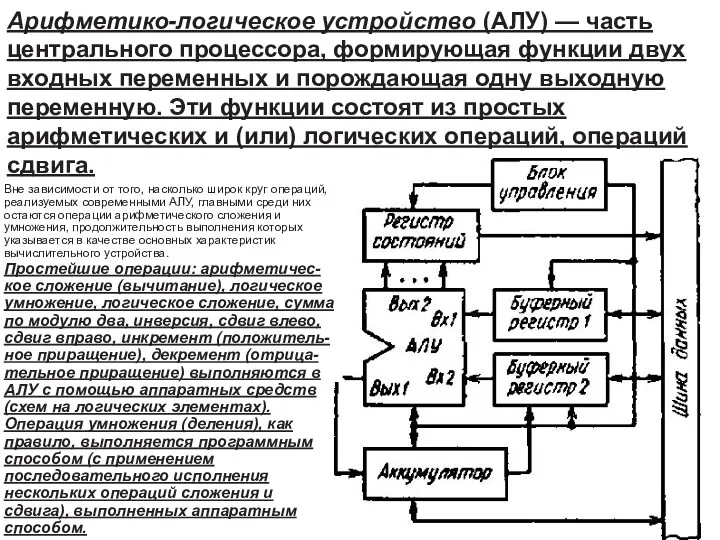

- 21. Арифметико-логическое устройство (АЛУ) — часть центрального процессора, формирующая функции двух входных переменных и порождающая одну выходную

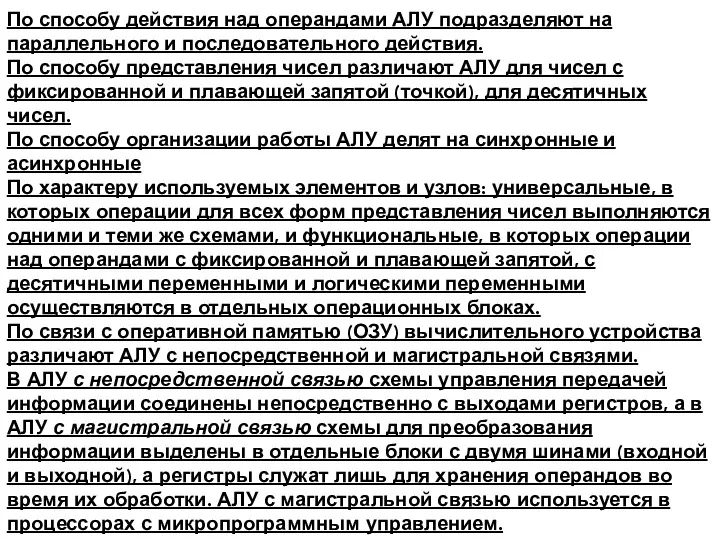

- 22. По способу действия над операндами АЛУ подразделяют на параллельного и последовательного действия. По способу представления чисел

- 23. Современная технология изготовления ИМС позволяет выполнить весьма сложные электронные устройства в виде одной или нескольких ИМС.

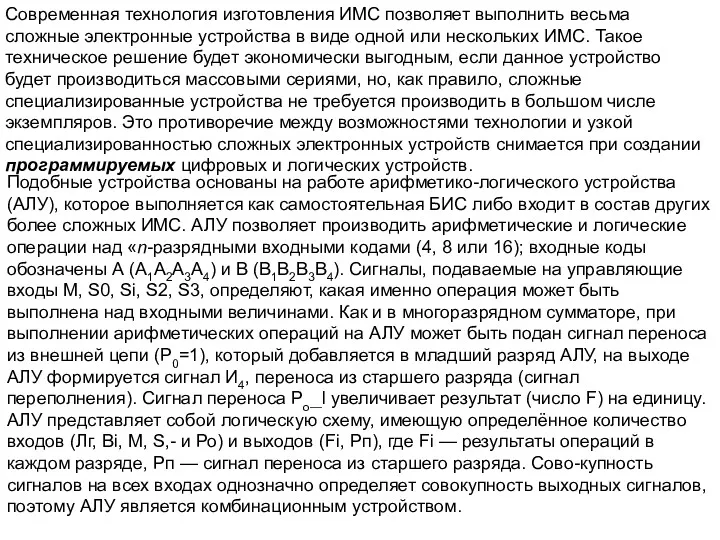

- 24. При управляющем сигнале М=0 АЛУ выполняет арифметические операции над входными n-разрядными двоичными числами А к В:

- 26. Схемы наращивания АЛУ при последовательном (в) и параллельном (б) переносах и реализация функций компаратора для группы

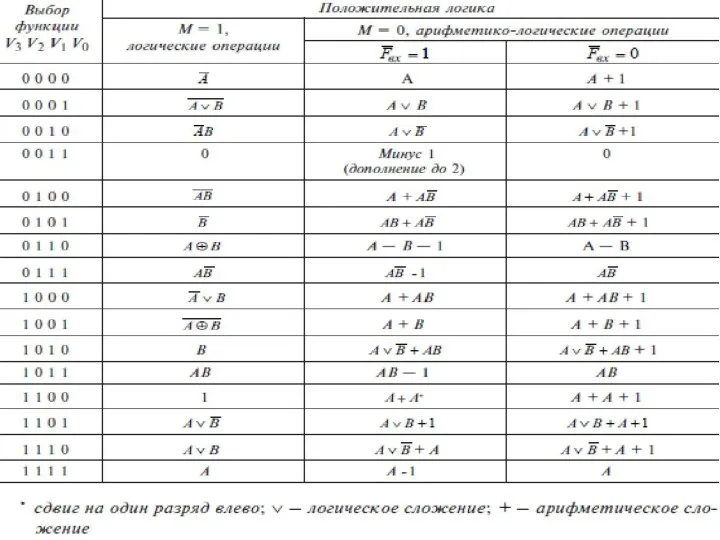

- 27. Несмотря на разнообразие операций, выполняемых АЛУ, его функциональность ограниченна: устройство выполняет только операции над двумя переменными,

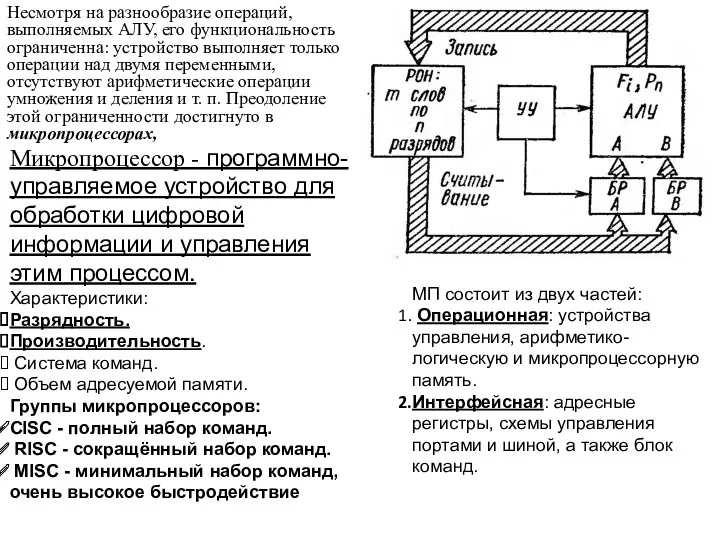

- 28. Читают и дешифруют команды, поступающие из основной памяти. Принимают и обрабатывают запросы от адаптеров про обслуживание

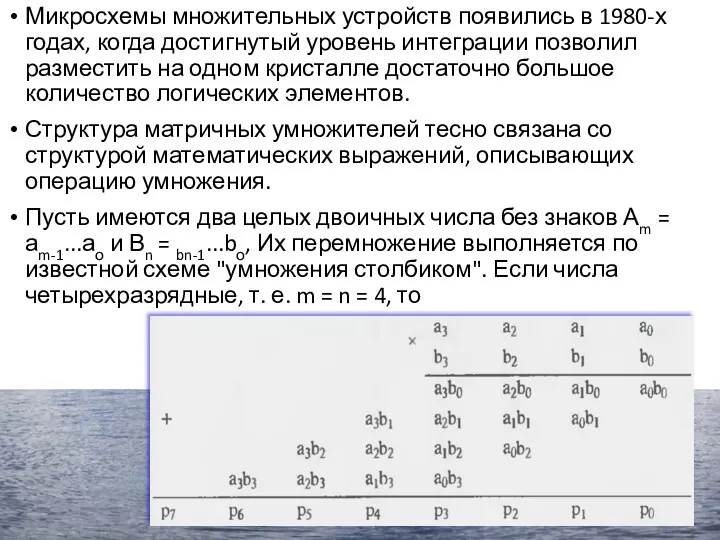

- 30. Матричные умножители

- 31. Микросхемы множительных устройств появились в 1980-х годах, когда достигнутый уровень интеграции позволил разместить на одном кристалле

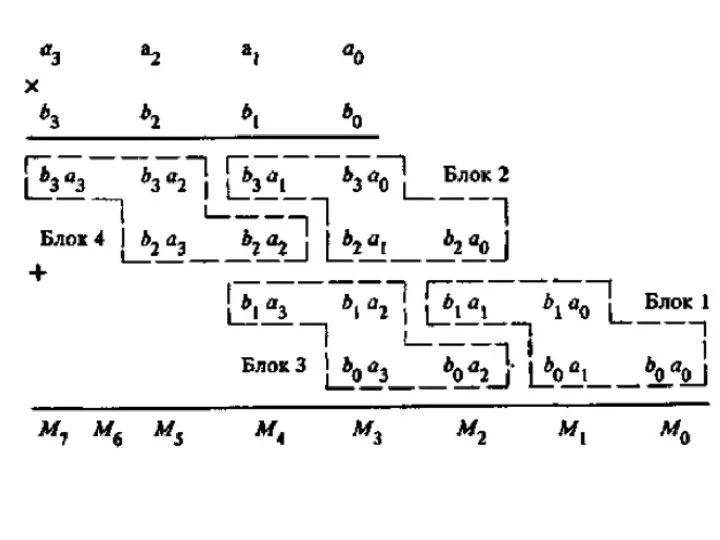

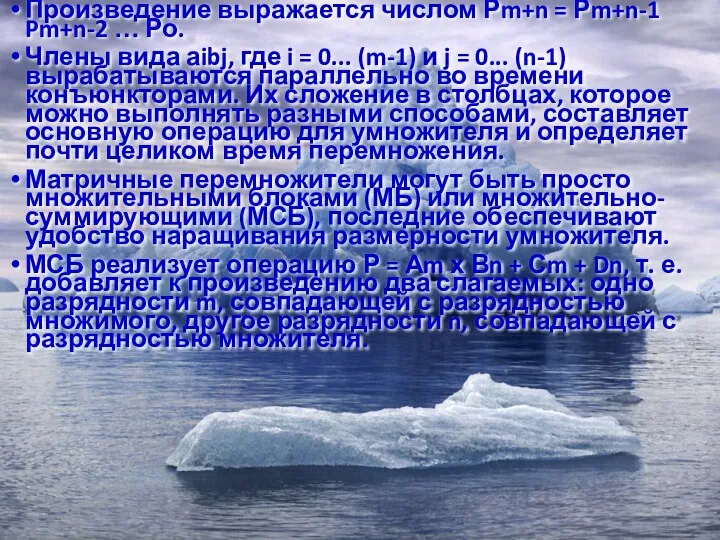

- 32. Произведение выражается числом Рm+n = Рm+n-1 Pm+n-2 … Ро. Члены вида аibj, где i = 0...

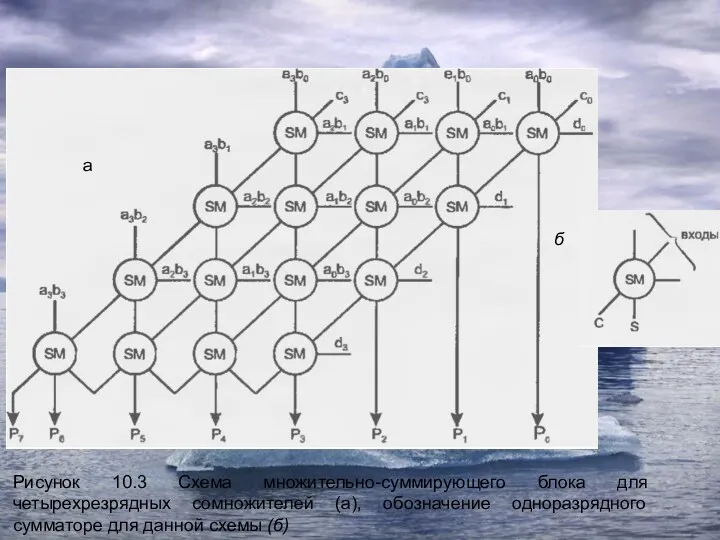

- 33. Множительно-суммирующие блоки Множительно-суммирующий блок для четырехразрядных операндов без набора конъюнкторов, вырабатывающих члены вида аibj, показан на

- 34. Рисунок 10.3 Схема множительно-суммирующего блока для четырехрезрядных сомножителей (а), обозначение одноразрядного сумматоре для данной схемы (б)

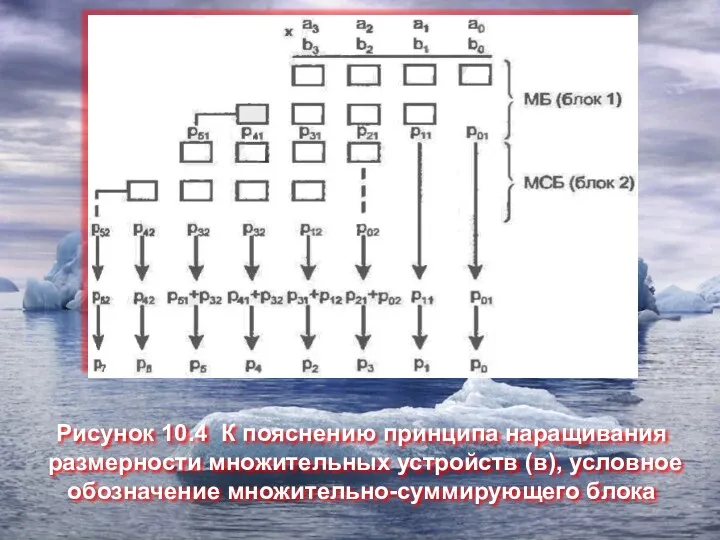

- 35. Рисунок 10.4 К пояснению принципа наращивания размерности множительных устройств (в), условное обозначение множительно-суммирующего блока

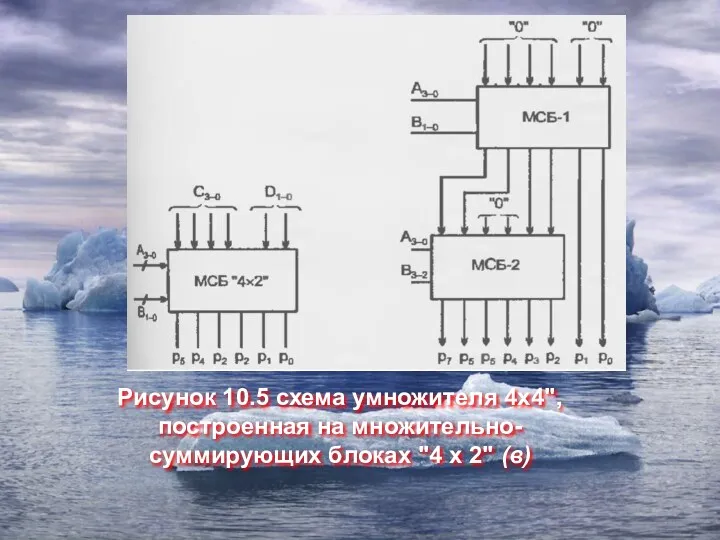

- 36. Рисунок 10.5 схема умножителя 4x4", построенная на множительно-суммирующих блоках "4 х 2" (в)

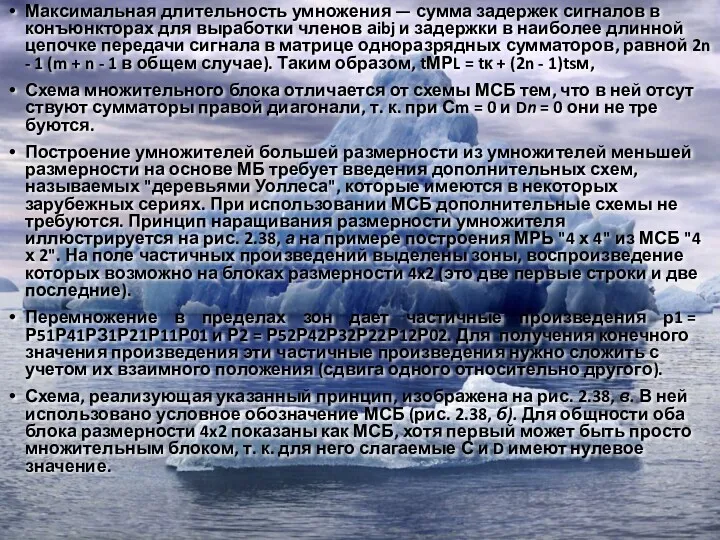

- 37. Максимальная длительность умножения — сумма задержек сигналов в конъюнкторах для выработки членов аibj и задержки в

- 38. Схемы ускоренного умножения Для ускорения умножения разработан ряд алгоритмов, большой вклад в эти разработки внес Э.

- 39. Непосредственное воспроизведение соотношения (а) связано с выработкой частичных произведений вида Abj2i (i = 0...n - 1).

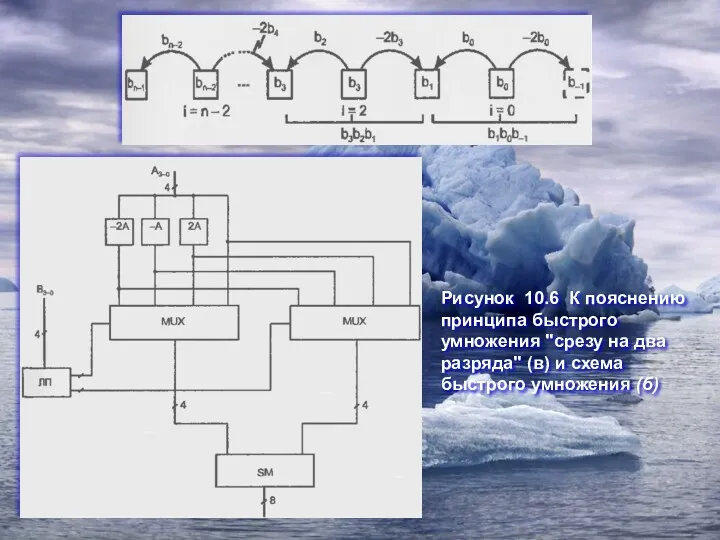

- 40. Рисунок 10.6 К пояснению принципа быстрого умножения "срезу на два разряда" (в) и схема быстрого умножения

- 41. Для всех возможных сочетаний bi+1, bi, bi-1 можно составить таблицу (табл. 2.14) частичных произведений.

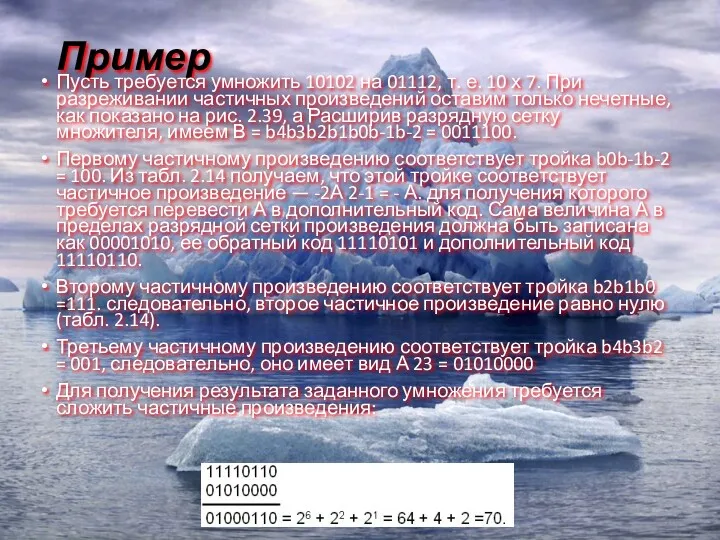

- 42. Пример Пусть требуется умножить 10102 на 01112, т. е. 10 х 7. При разреживании частичных произведений

- 43. Схема, реализующая алгоритм быстрого умножения сразу на два разряда, показана на рис. 2.39, б. Множимое А

- 44. Блок СКГ вырабатывает также функции генерации и прозрачности для всей группы обслуживаемых им АЛУ, что при

- 45. блок регистров БРег, предназначенный для приёма и размещения операндов и результата операции; блок арифметико-логических операций БАЛО,

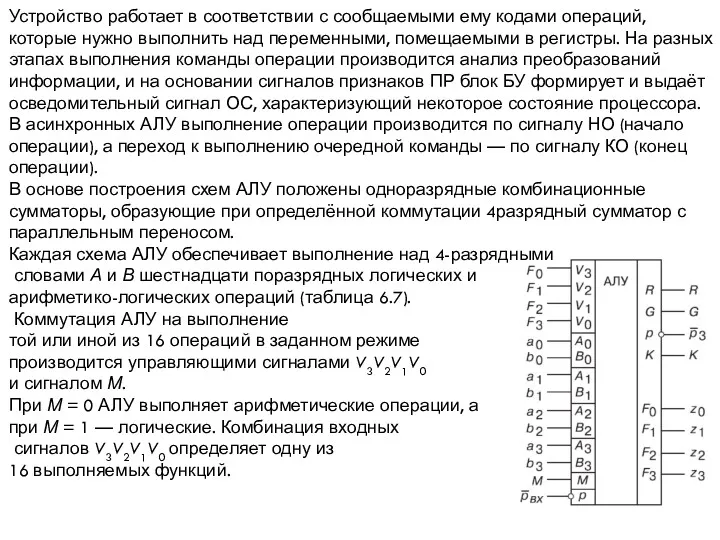

- 46. Устройство работает в соответствии с сообщаемыми ему кодами операций, которые нужно выполнить над переменными, помещаемыми в

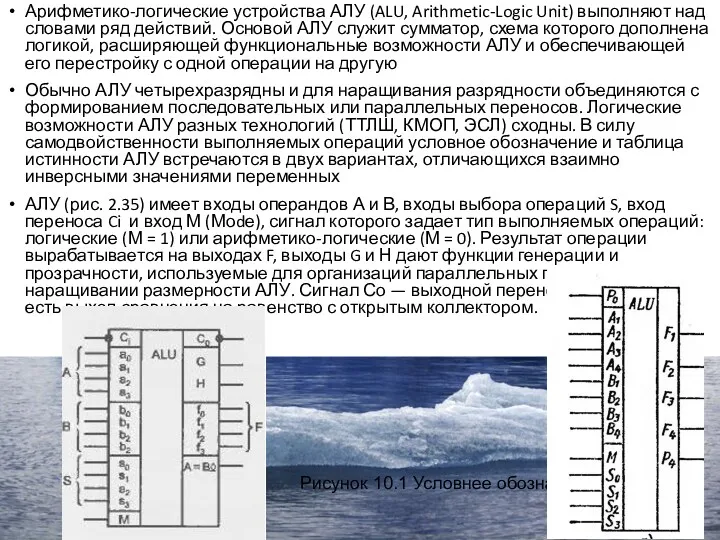

- 49. Арифметико-логические устройства АЛУ (ALU, Arithmetic-Logic Unit) выполняют над словами ряд действий. Основой АЛУ служит сумматор, схема

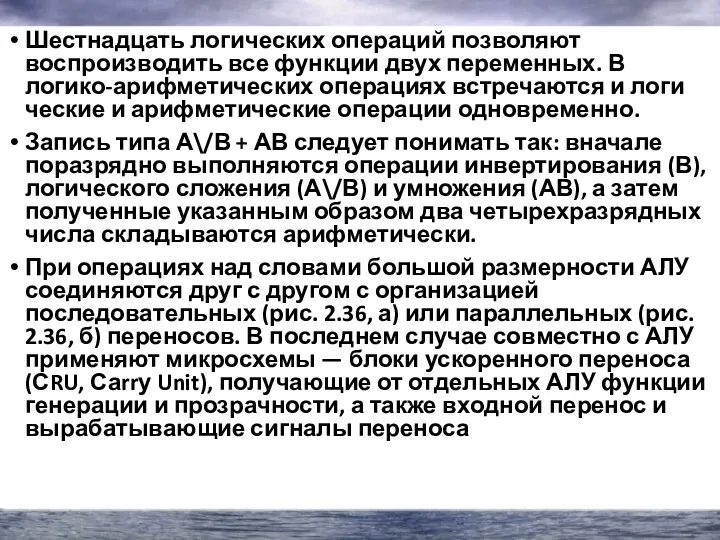

- 50. Шестнадцать логических операций позволяют воспроизводить все функции двух переменных. В логико-арифметических операциях встречаются и логические и

- 51. запрет по А импликация по А

- 53. Скачать презентацию

Презентация к уроку Резьба по дереву (вводное занятие)

Презентация к уроку Резьба по дереву (вводное занятие) Презентация. Фелтинг. Брошь Мак

Презентация. Фелтинг. Брошь Мак Религия как социокультурный феномен

Религия как социокультурный феномен Електронні та друковані портфоліо

Електронні та друковані портфоліо Александр Трифонович Твардовский 1910-1971

Александр Трифонович Твардовский 1910-1971 Бумажная пластика. Игрушки на елке

Бумажная пластика. Игрушки на елке Самоходные погрузчики

Самоходные погрузчики СПб ГБПОУ Ленинградский машиностроительный техникум им. Ж.Я. Котина

СПб ГБПОУ Ленинградский машиностроительный техникум им. Ж.Я. Котина Кроссворд по правилам дорожного движения (с использованием клавиатуры)

Кроссворд по правилам дорожного движения (с использованием клавиатуры) Цветы в технике квиллинга

Цветы в технике квиллинга Кампания г. Санкт-Петербург: GRP 90.83 OTS 4039.30

Кампания г. Санкт-Петербург: GRP 90.83 OTS 4039.30 Способы решения показательных уравнений

Способы решения показательных уравнений Банк Хоум Кредит

Банк Хоум Кредит Экономика нефтегазовой отрасли

Экономика нефтегазовой отрасли Средиземноморская природная зона, или субтропики: жёстколистные вечнозелёные леса и кустарники, описание, климат, почвы

Средиземноморская природная зона, или субтропики: жёстколистные вечнозелёные леса и кустарники, описание, климат, почвы В бизнесе всё решают связью. Коммерческое предложение ПАО Ростелеком

В бизнесе всё решают связью. Коммерческое предложение ПАО Ростелеком Метод эквивалентного генератора

Метод эквивалентного генератора Мощность конвектора отопления

Мощность конвектора отопления Проект В лесном краю Почитаева

Проект В лесном краю Почитаева КОМПЬЮТЕРНАЯ ПРЕЗЕНТАЦИЯ ПО ГЕОГРАФИИ 11 КЛАСС ФРГ

КОМПЬЮТЕРНАЯ ПРЕЗЕНТАЦИЯ ПО ГЕОГРАФИИ 11 КЛАСС ФРГ Неделя игры и игрушки в подготовительной группе №8

Неделя игры и игрушки в подготовительной группе №8 Структура письма

Структура письма Актуальные проблемы транспортной инфраструктуры в субъектах России

Актуальные проблемы транспортной инфраструктуры в субъектах России Проектирование системы электроснабжения производственного цеха машиностроительного завода

Проектирование системы электроснабжения производственного цеха машиностроительного завода Механические процессы

Механические процессы Замбия Республикасы

Замбия Республикасы Презентация к исследованию

Презентация к исследованию Речной транспорт

Речной транспорт