Содержание

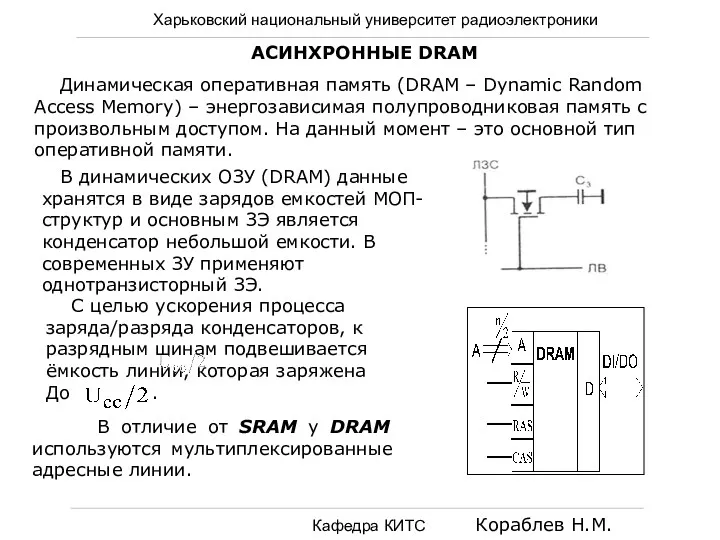

- 2. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. АСИНХРОННЫЕ DRAM В динамических ОЗУ (DRAM) данные хранятся

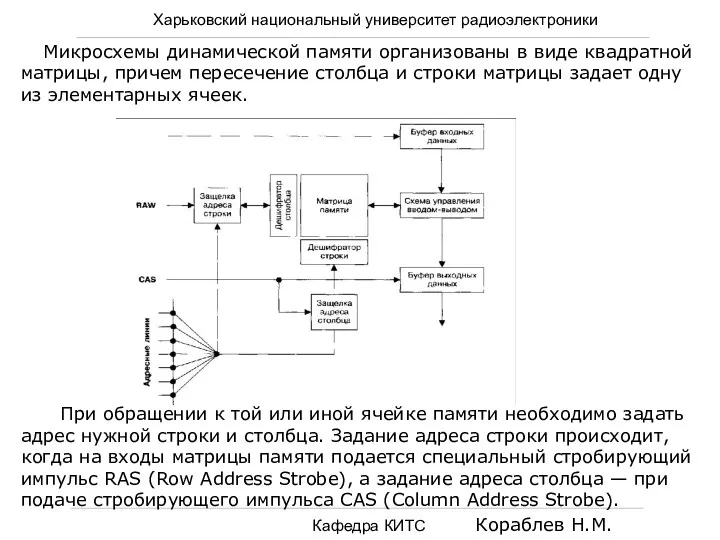

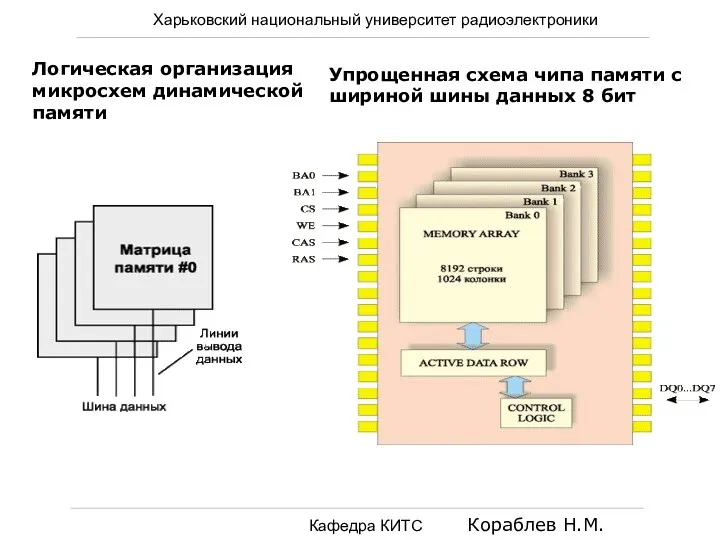

- 3. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Микросхемы динамической памяти организованы в виде квадратной матрицы,

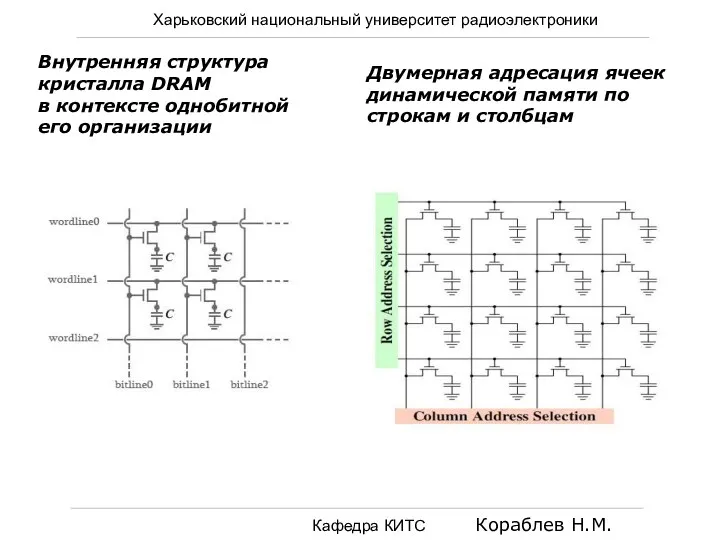

- 4. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Внутренняя структура кристалла DRAM в контексте однобитной его

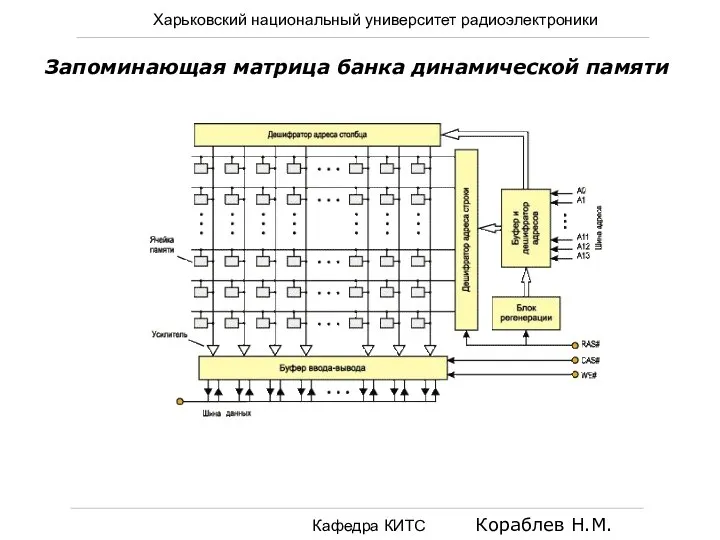

- 5. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Запоминающая матрица банка динамической памяти

- 6. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Упрощенная схема чипа памяти с шириной шины данных

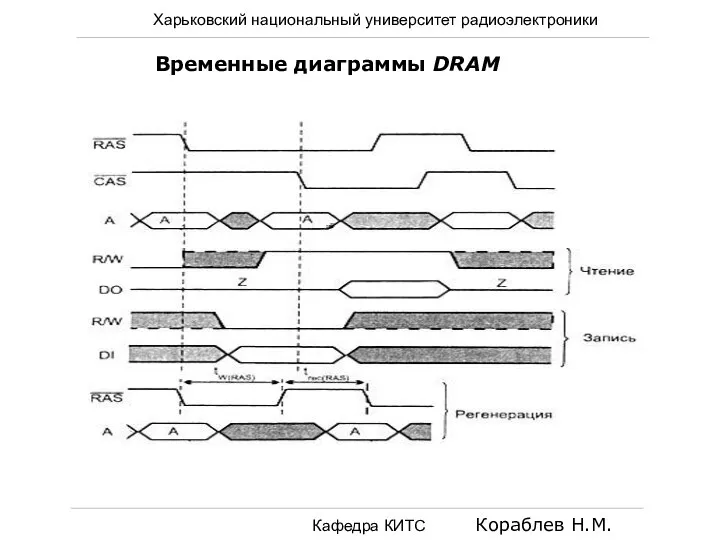

- 7. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Временные диаграммы DRAM

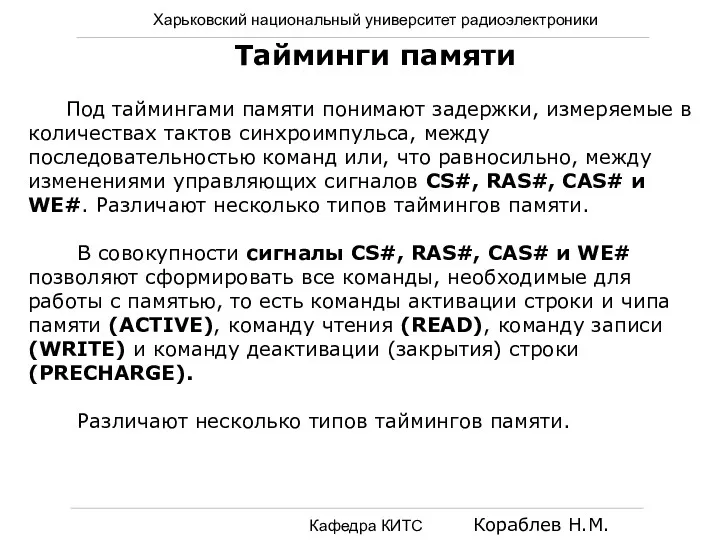

- 8. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти Под таймингами памяти понимают задержки, измеряемые

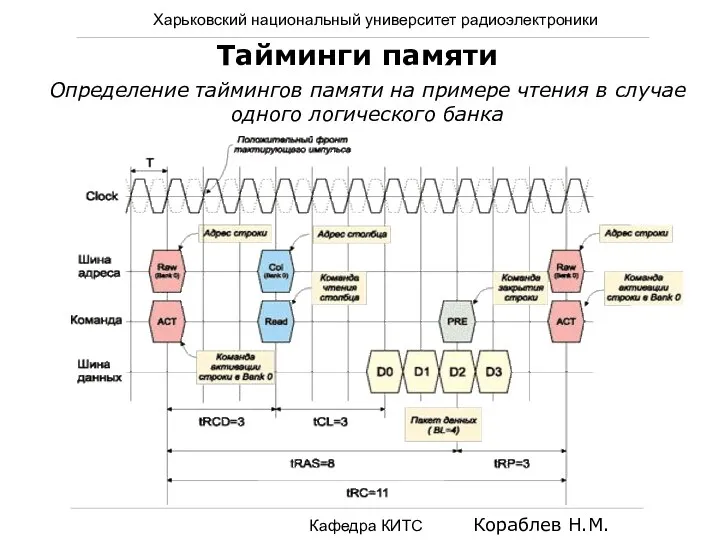

- 9. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти Определение таймингов памяти на примере чтения

- 10. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти 1. RAS# to CAS# Delay (tRCD)

- 11. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти 4. RAS# Precharge (tRP) Завершение цикла

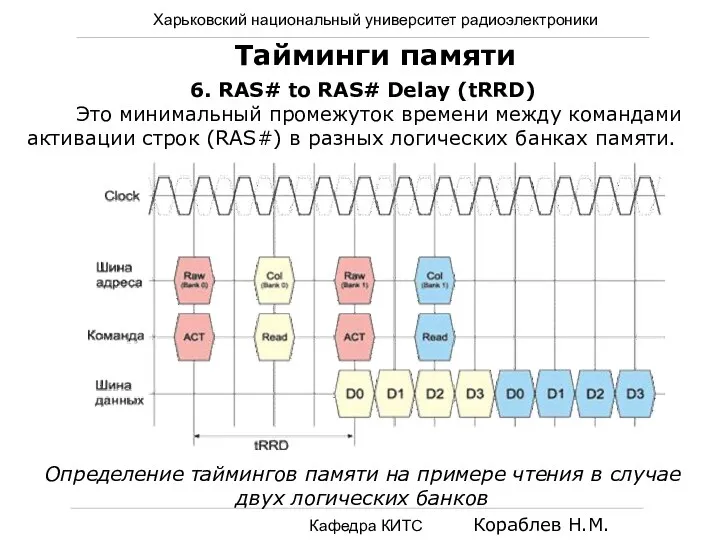

- 12. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти 6. RAS# to RAS# Delay (tRRD)

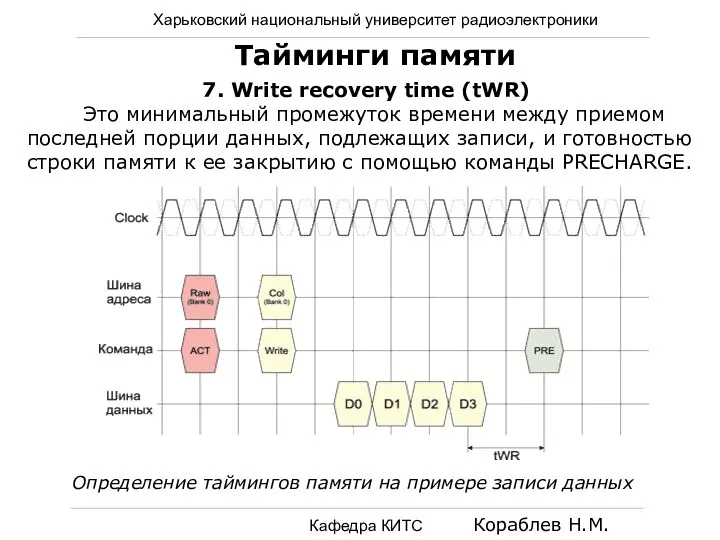

- 13. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти 7. Write recovery time (tWR) Это

- 14. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти 8. Write to Read Delay (tWTR)

- 15. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Тайминги памяти Запись таймингов памяти Наиболее значимыми по

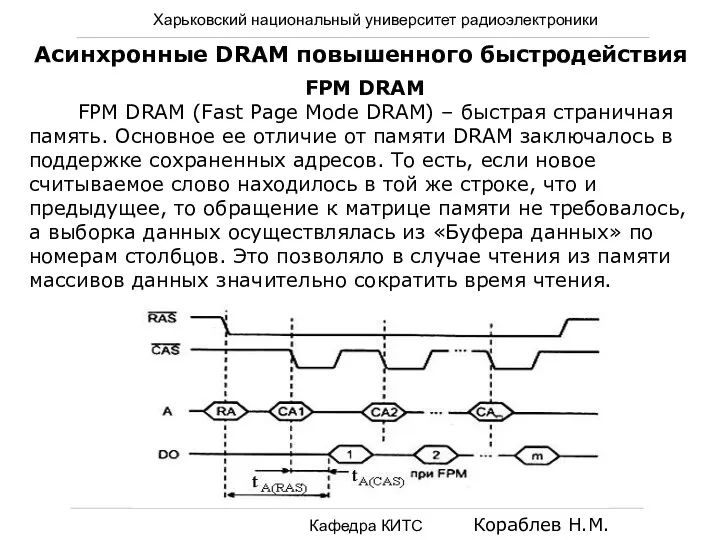

- 16. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Асинхронные DRAM повышенного быстродействия FPM DRAM FPM DRAM

- 17. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Асинхронные DRAM повышенного быстродействия EDO-DRAM EDO-DRAM (Extended Data

- 19. Скачать презентацию

Жеке дара ұдайы өндіріс теориясының негізі. Дәріс 6

Жеке дара ұдайы өндіріс теориясының негізі. Дәріс 6 Время. Скорость. Расстояние

Время. Скорость. Расстояние веселые игрушки

веселые игрушки Информация для родителей будущих первоклассников

Информация для родителей будущих первоклассников Сложение и вычитание векторов

Сложение и вычитание векторов Млечный Путь

Млечный Путь Макроэкономика. Макроэкономическая нестабильность: циклическое развитие экономики, инфляция, безработица. Тема 4

Макроэкономика. Макроэкономическая нестабильность: циклическое развитие экономики, инфляция, безработица. Тема 4 Шаблон Фракталы-9

Шаблон Фракталы-9 Семь мудрецов Древней Греции

Семь мудрецов Древней Греции Компас и азимут

Компас и азимут Организация видов работ при эксплуатации и реконструкции строительных объектов

Организация видов работ при эксплуатации и реконструкции строительных объектов Служба главного механика Интерпайп сталь

Служба главного механика Интерпайп сталь Общее учение об опухолях. Мезенхимальные опухоли

Общее учение об опухолях. Мезенхимальные опухоли Презентация к уроку: Классификация кислородсодержащих органических веществ

Презентация к уроку: Классификация кислородсодержащих органических веществ HNX Series Show you a real world!

HNX Series Show you a real world! Проблемы трудоустройства молодых специалистов в России

Проблемы трудоустройства молодых специалистов в России Преобразование комплексного чертежа

Преобразование комплексного чертежа Женская одежда

Женская одежда Методическая разработка урока по химии Металлы

Методическая разработка урока по химии Металлы Выигрышные стратегии

Выигрышные стратегии Особенности окраски полов. Лаки и эмали. Дефекты и способы их устранения

Особенности окраски полов. Лаки и эмали. Дефекты и способы их устранения Работа с таблицами как средство формирования УУД на уроках математики

Работа с таблицами как средство формирования УУД на уроках математики Lectio divina або наука Божа

Lectio divina або наука Божа Презентация к классному часу на тему Здоровые дети в здоровой семье.

Презентация к классному часу на тему Здоровые дети в здоровой семье. Презентация к уроку технологии Что такое телеграмма

Презентация к уроку технологии Что такое телеграмма Лабораторная работа с применением Ц. Л. Архимед проводится на обобщающем уроке в 10 классе на органической химии, после изучения тем: Сложные эфиры, Жиры, Моющие вещества.

Лабораторная работа с применением Ц. Л. Архимед проводится на обобщающем уроке в 10 классе на органической химии, после изучения тем: Сложные эфиры, Жиры, Моющие вещества. Комплаентность пациента с артериальной гипертензией. Роль фельдшера

Комплаентность пациента с артериальной гипертензией. Роль фельдшера Приоритетные линейки топливных изделий на основе местного сырья и технологий термохимической конверсии

Приоритетные линейки топливных изделий на основе местного сырья и технологий термохимической конверсии