Содержание

- 2. Модуль центрального процессора С28x В целом укрупненная структура ЦСП TMS320F2812 может быть представлена в виде 4-х

- 3. Основные характеристики ЦСП семейства С28x ЦСП TMS320F2812 имеет высокопроизводительную статическую КМОП-технологию. Максимальная тактовая частота ядра составляет

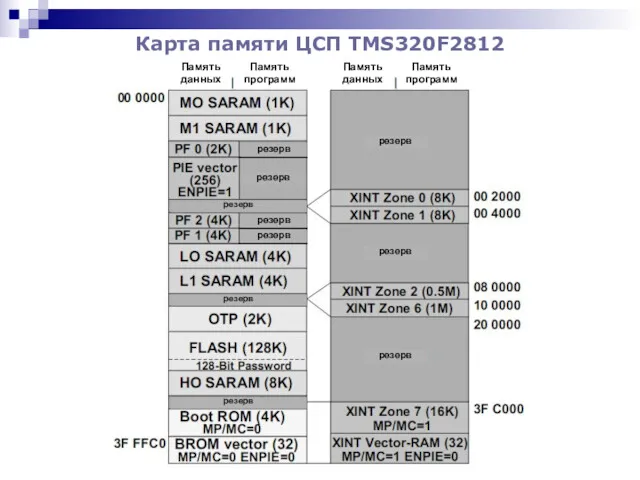

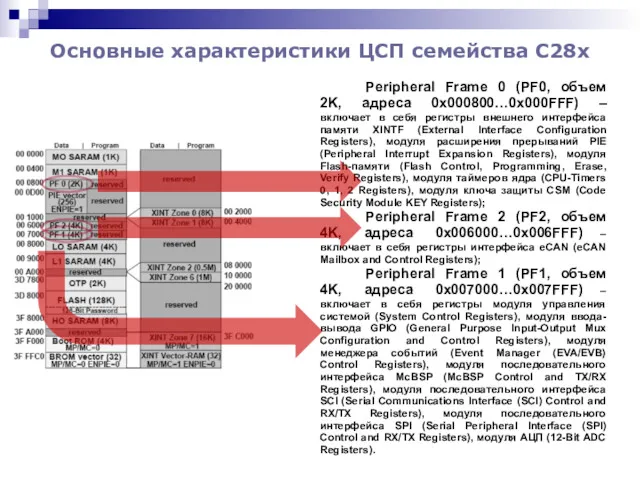

- 4. Карта памяти ЦСП TMS320F2812 Память данных Память программ Память данных Память программ резерв резерв резерв резерв

- 5. Основные характеристики ЦСП семейства С28x В качестве памяти данных используется исключительно ОЗУ однократного доступа общим объёмом

- 6. Основные характеристики ЦСП семейства С28x Peripheral Frame 0 (PF0, объем 2K, адреса 0x000800…0x000FFF) – включает в

- 7. Основные характеристики ЦСП семейства С28x Загрузочное ПЗУ (Boot ROM) объёмом 4 Кслова программируется на заводе-изготовителе и

- 8. Основные характеристики ЦСП семейства С28x Интерфейс внешней памяти XINTF (имеется только в ИМС TMS320F2812) состоит из

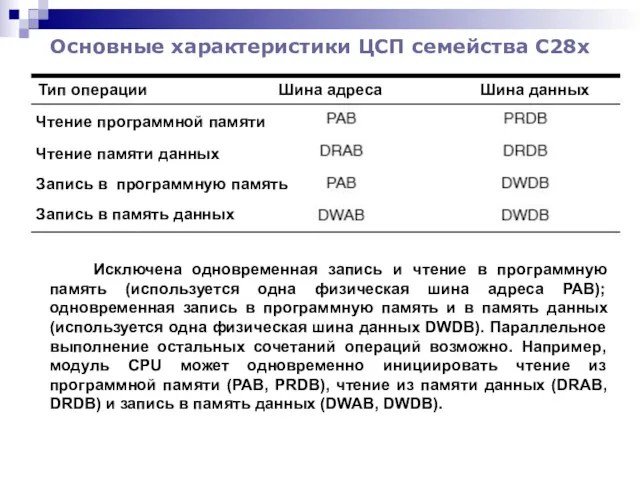

- 9. Основные характеристики ЦСП семейства С28x Функционально внутренняя шинная организация ЦСП семейства С28x включает в себя три

- 10. Основные характеристики ЦСП семейства С28x Исключена одновременная запись и чтение в программную память (используется одна физическая

- 11. Основные характеристики ЦСП семейства С28x Указанная система внутренних шин названа разработчиками Texas Instruments «модифицированная гарвардская архитектура».

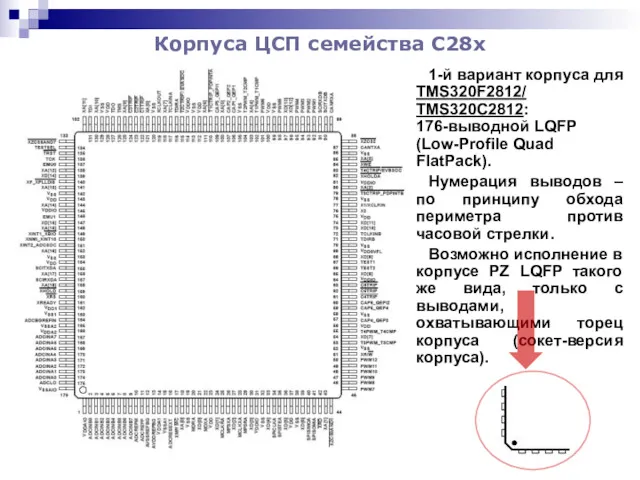

- 12. Корпуса ЦСП семейства С28x 1-й вариант корпуса для TMS320F2812/ TMS320С2812: 176-выводной LQFP (Low-Profile Quad FlatPack). Нумерация

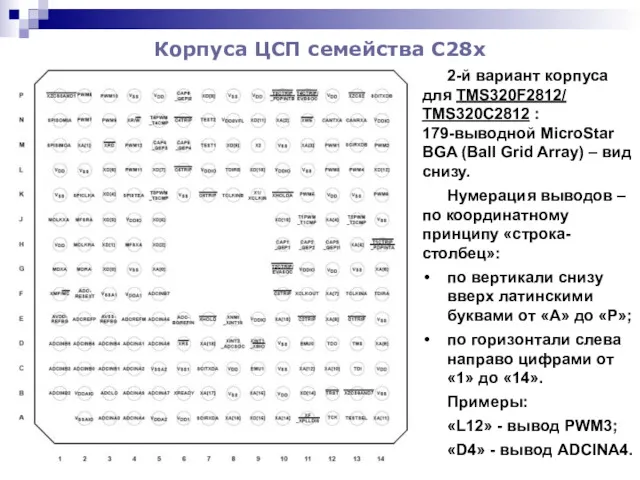

- 13. Корпуса ЦСП семейства С28x 2-й вариант корпуса для TMS320F2812/ TMS320С2812 : 179-выводной MicroStar BGA (Ball Grid

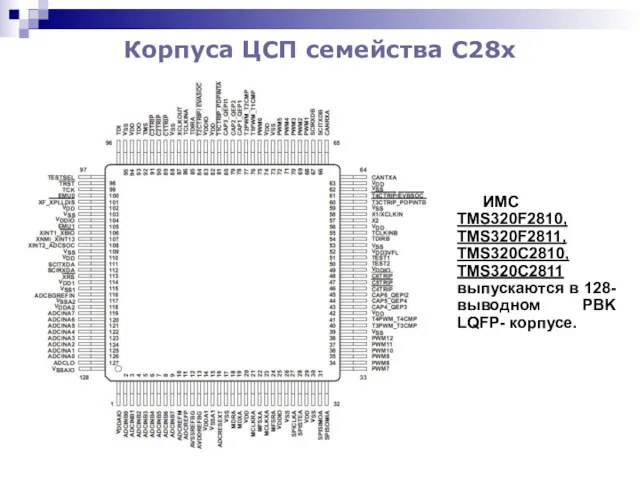

- 14. Корпуса ЦСП семейства С28x ИМС TMS320F2810, TMS320F2811, TMS320С2810, TMS320С2811 выпускаются в 128-выводном PBK LQFP- корпусе.

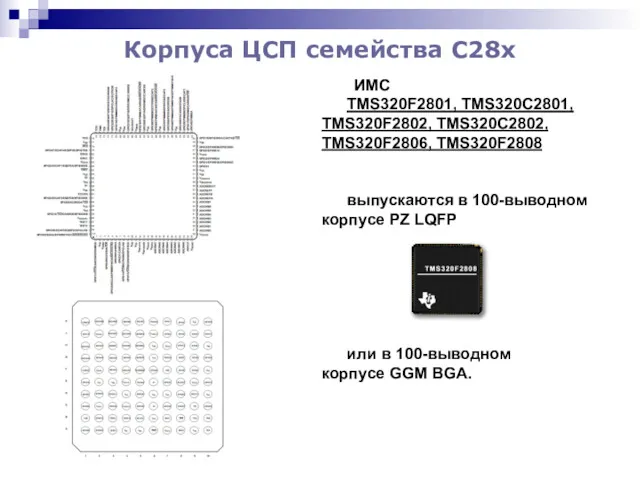

- 15. Корпуса ЦСП семейства С28x ИМС TMS320F2801, TMS320С2801, TMS320F2802, TMS320С2802, TMS320F2806, TMS320F2808 выпускаются в 100-выводном корпусе PZ

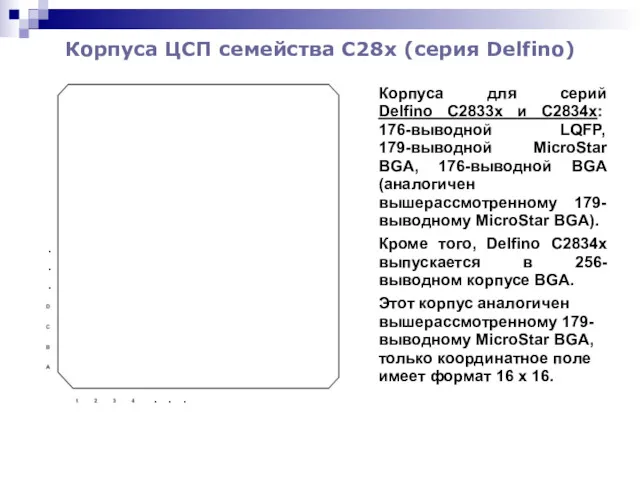

- 16. Корпуса ЦСП семейства С28x (серия Delfino) Корпуса для серий Delfino C2833x и C2834x: 176-выводной LQFP, 179-выводной

- 17. Корпуса ЦСП семейства С28x (серия Piccolo) Серия Piccolo C2802x: 38- выводной корпус TSSOP, шаг выводов 0.65mm

- 19. Скачать презентацию

Презентация Государственные символы Республики Башкортостан и символы Белокатайского района

Презентация Государственные символы Республики Башкортостан и символы Белокатайского района Поверхности нагрева паровых котлов

Поверхности нагрева паровых котлов Вводные слова и знаки препинания при них. 8 класс

Вводные слова и знаки препинания при них. 8 класс Третейское судопроизводство

Третейское судопроизводство Союз как часть речи

Союз как часть речи Реки Ставропольского края

Реки Ставропольского края Аппликация, виды аппликации

Аппликация, виды аппликации Мифология. Религия. Философия. Сходства и различия

Мифология. Религия. Философия. Сходства и различия Бытовые приборы для уборки и создания микроклимата помещений

Бытовые приборы для уборки и создания микроклимата помещений Рекреационное обустройство лесного участка в Новоспасском лесничестве Ульяновской области

Рекреационное обустройство лесного участка в Новоспасском лесничестве Ульяновской области Организация местной работы станции Хабаровск-2

Организация местной работы станции Хабаровск-2 Сварка чугуна

Сварка чугуна Эффективное общение

Эффективное общение Презентация Вода, которую мы пьём

Презентация Вода, которую мы пьём Развитие коммуникативных навыков.

Развитие коммуникативных навыков. Презентация Правила дорожного движения в первой младшей группе

Презентация Правила дорожного движения в первой младшей группе Профессия - стропальщик

Профессия - стропальщик Реализация принципов личностно-ориентированного обучения в работе с одаренными детьми.

Реализация принципов личностно-ориентированного обучения в работе с одаренными детьми. Гики как субкультура

Гики как субкультура Моя родина - Калькутта

Моя родина - Калькутта Духовно-нравственное развитие и воспитание личности гражданина России

Духовно-нравственное развитие и воспитание личности гражданина России Источники гражданского права

Источники гражданского права Шерстяные ткани

Шерстяные ткани Гидролазалар. Гидролаза классына жалпы сипаттама. Классификациясы

Гидролазалар. Гидролаза классына жалпы сипаттама. Классификациясы Появление славян

Появление славян Бухгалтерский учет в бюджетных, казенных и автономных учреждениях

Бухгалтерский учет в бюджетных, казенных и автономных учреждениях Проектирование поковок, получаемых горячей объемной штамповкой

Проектирование поковок, получаемых горячей объемной штамповкой Канализвция внутренняя, внешняя, система очистки стоков

Канализвция внутренняя, внешняя, система очистки стоков