Содержание

- 2. Все собирают одноразрядный комбинационный сумматор (описан в разделе 1, схема - **). Он затем используется как

- 3. Сумматор – это операционный элемент, предназначенный для выполнения микрооперации сложения чисел. Если операнды и результат сложения

- 4. Операционное устройство может производить арифметические и логические операции в соответствии с заложенной в его основу микропрограммой

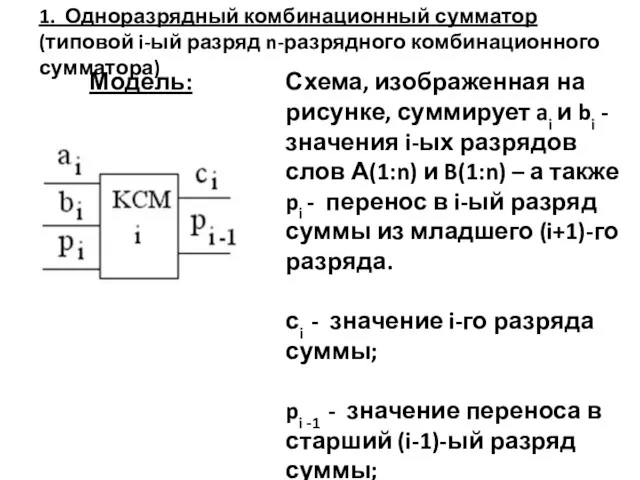

- 5. 1. Одноразрядный комбинационный сумматор (типовой i-ый разряд n-разрядного комбинационного сумматора) Модель: Схема, изображенная на рисунке, суммирует

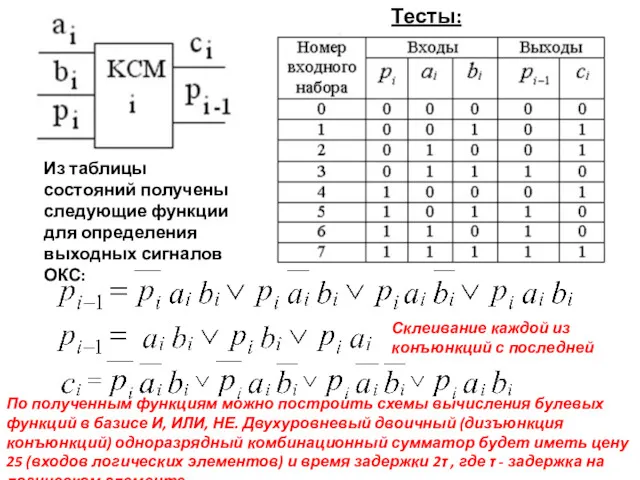

- 6. Тесты: Склеивание каждой из конъюнкций с последней По полученным функциям можно построить схемы вычисления булевых функций

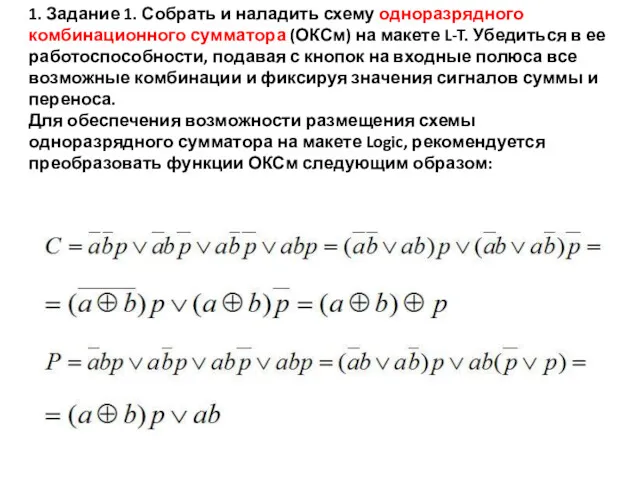

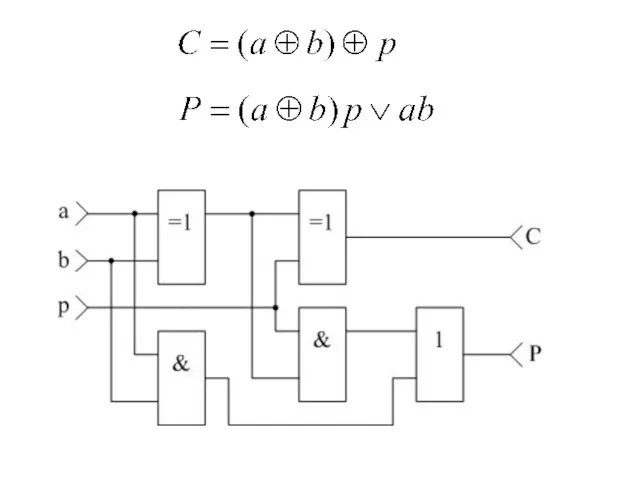

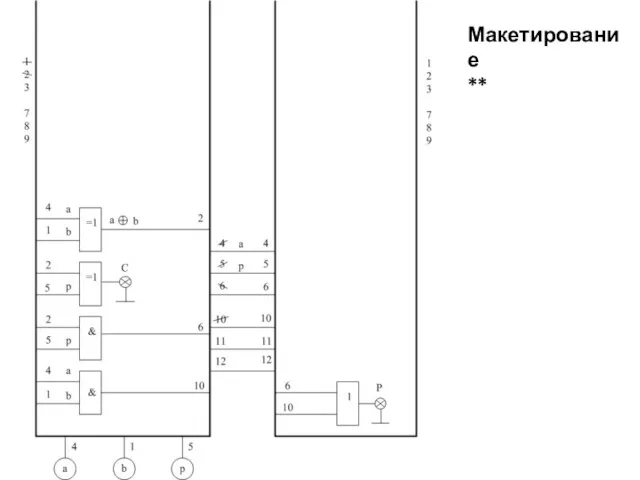

- 7. 1. Задание 1. Собрать и наладить схему одноразрядного комбинационного сумматора (ОКСм) на макете L-T. Убедиться в

- 9. Макетирование **

- 10. 2. Последовательный накапливающий сумматор

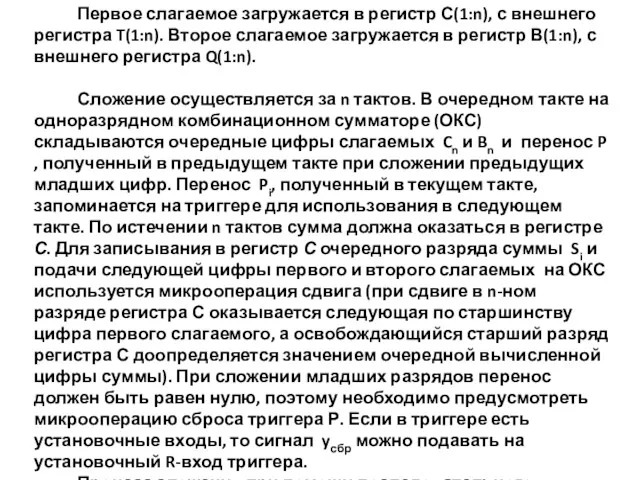

- 11. Первое слагаемое загружается в регистр С(1:n), с внешнего регистра T(1:n). Второе слагаемое загружается в регистр В(1:n),

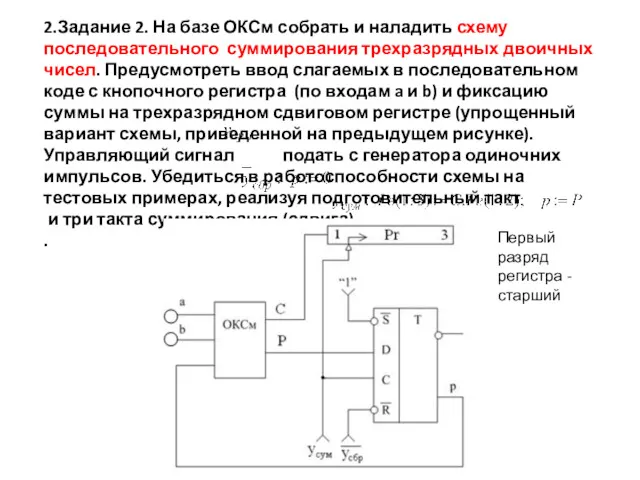

- 12. 2.Задание 2. На базе ОКСм собрать и наладить схему последовательного суммирования трехразрядных двоичных чисел. Предусмотреть ввод

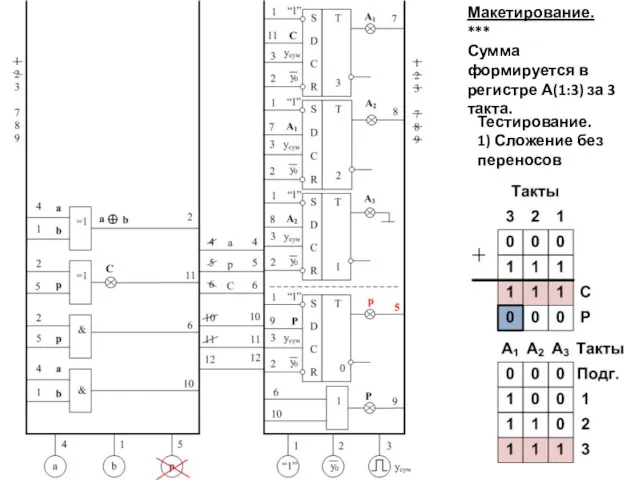

- 13. Макетирование. *** Сумма формируется в регистре А(1:3) за 3 такта. Тестирование. 1) Сложение без переносов

- 14. 2). Сложение с переносами.

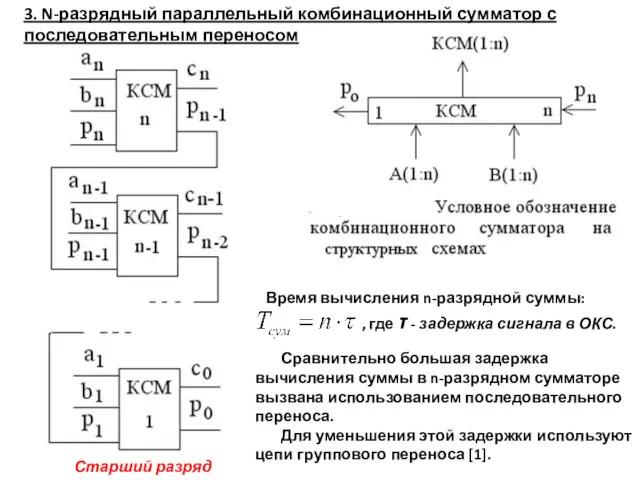

- 15. 3. N-разрядный параллельный комбинационный сумматор с последовательным переносом Время вычисления n-разрядной суммы: , где τ -

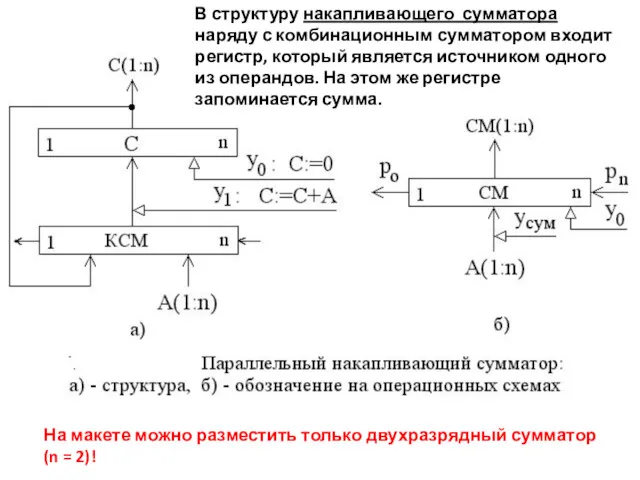

- 16. В структуру накапливающего сумматора наряду с комбинационным сумматором входит регистр, который является источником одного из операндов.

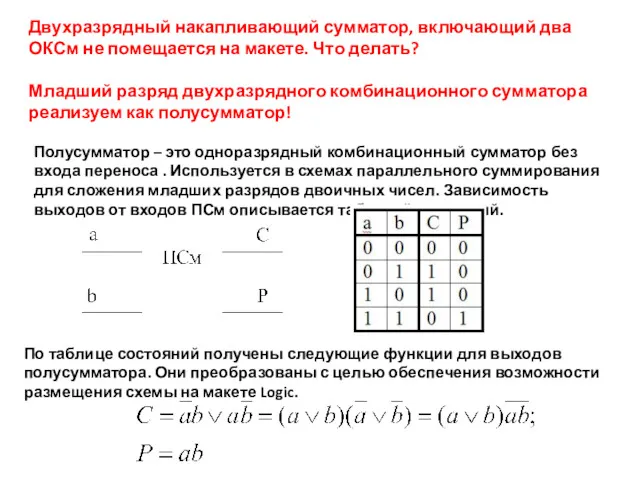

- 17. Двухразрядный накапливающий сумматор, включающий два ОКСм не помещается на макете. Что делать? Младший разряд двухразрядного комбинационного

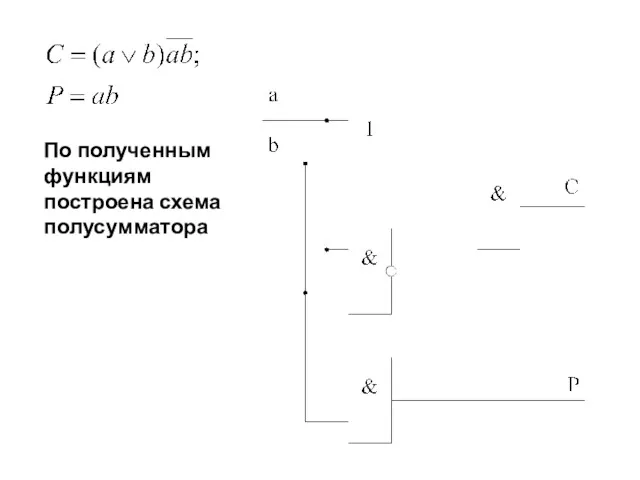

- 18. По полученным функциям построена схема полусумматора

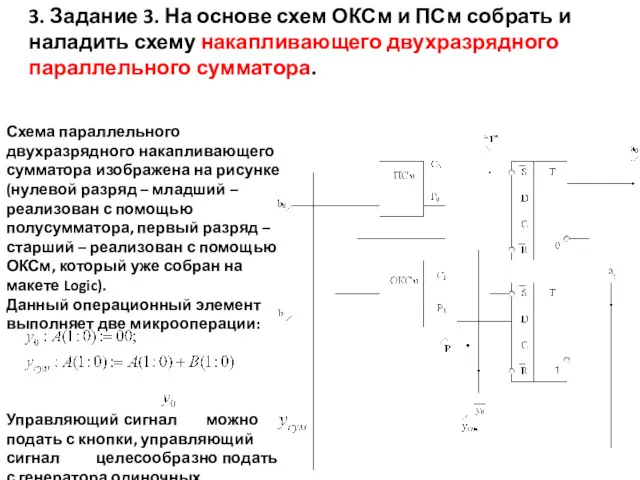

- 19. 3. Задание 3. На основе схем ОКСм и ПСм собрать и наладить схему накапливающего двухразрядного параллельного

- 20. 3.1. Сначала на макете Logic соберем и отладим схему двухразрядного параллельного комбинационного сумматора с последовательным переносом.

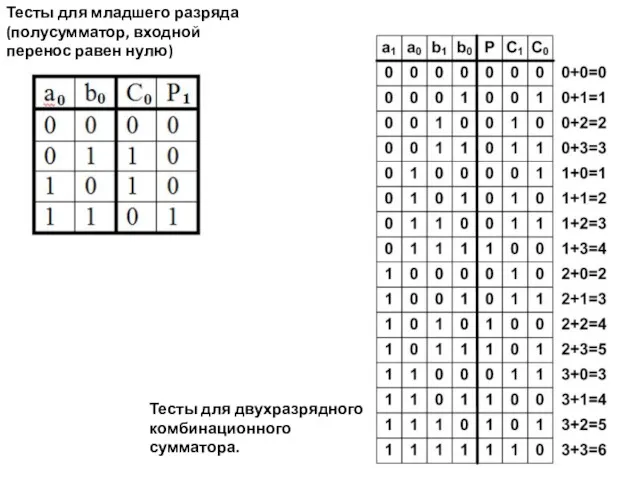

- 21. Тесты для младшего разряда (полусумматор, входной перенос равен нулю) Тесты для двухразрядного комбинационного сумматора.

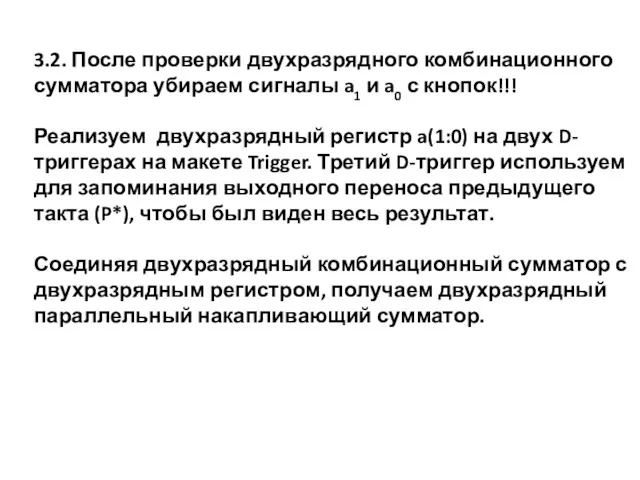

- 22. 3.2. После проверки двухразрядного комбинационного сумматора убираем сигналы a1 и a0 с кнопок!!! Реализуем двухразрядный регистр

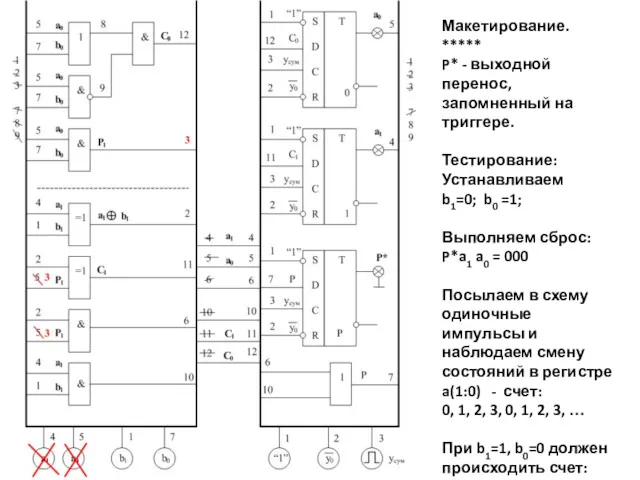

- 23. Макетирование. ***** P* - выходной перенос, запомненный на триггере. Тестирование: Устанавливаем b1=0; b0 =1; Выполняем сброс:

- 25. Скачать презентацию

Троянский конь

Троянский конь Напівпровідниковий діод

Напівпровідниковий діод Человек в ландшафте

Человек в ландшафте 8 Марта

8 Марта Профилактика агрессивного поведения

Профилактика агрессивного поведения Чудеса света. Колизей

Чудеса света. Колизей Неогнестрельные переломы нижней челюсти. Клиника, диагностика

Неогнестрельные переломы нижней челюсти. Клиника, диагностика монастыри

монастыри Цемент и его производство

Цемент и его производство Динамика системы материальных точек. Лекция 3.0

Динамика системы материальных точек. Лекция 3.0 Родительское собрание первый раз в первый класс

Родительское собрание первый раз в первый класс Смешанные числа. 5 класс

Смешанные числа. 5 класс БезОпасный интернет

БезОпасный интернет Технологическая оснастка

Технологическая оснастка Презентация Герои войны - кто они?

Презентация Герои войны - кто они? Сказка о Весёлом Язычке

Сказка о Весёлом Язычке Сказкотерапия. Работа со сказками

Сказкотерапия. Работа со сказками Механическое оборудование предприятий

Механическое оборудование предприятий Расселение древнейшего человека. Человек разумный

Расселение древнейшего человека. Человек разумный Легенды о короле Артуре: Мифы и Реальность

Легенды о короле Артуре: Мифы и Реальность Предложения РААСН для строительного комплекса и ЖКХ

Предложения РААСН для строительного комплекса и ЖКХ Высокомолекулярные соединения

Высокомолекулярные соединения Симонов Константин Михайлович 28.11.1915 – 28.08.1975

Симонов Константин Михайлович 28.11.1915 – 28.08.1975 Кто где живёт?

Кто где живёт? Урок знаний, посвященный 20-летию Конституции Российской Федерации.

Урок знаний, посвященный 20-летию Конституции Российской Федерации. Педагогический проект

Педагогический проект Выступление на районном конкурсе Учитель года 2004.

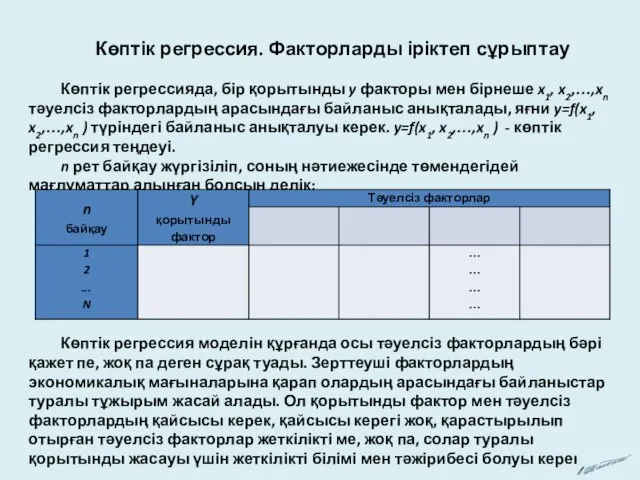

Выступление на районном конкурсе Учитель года 2004. Көптік регрессия. Факторларды іріктеп сұрыптау

Көптік регрессия. Факторларды іріктеп сұрыптау