Содержание

- 2. Постановка задач: Как компьютер выполняет арифметические действия? Как устроен его «ум»? Как компьютер запоминает информацию? Какова

- 3. ПОЛУСУММАТОР И в двоичной системе счисления и в алгебре логики информация представлена в виде двоичных кодов.

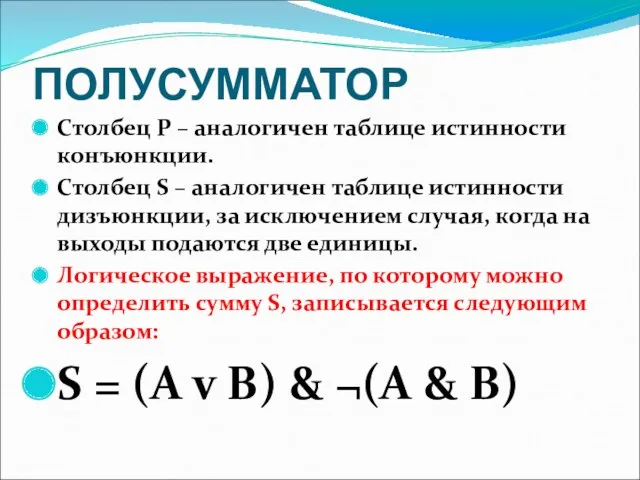

- 4. ПОЛУСУММАТОР Столбец P – аналогичен таблице истинности конъюнкции. Столбец S – аналогичен таблице истинности дизъюнкции, за

- 5. ПОЛУСУММАТОР Построим к этому логическому выражению логическую схему: Полученная нами схема выполняет сложение двоичных одноразрядных чисел

- 6. СУММАТОР Более «умным» является устройство, которое при сложении учитывает перенос из младшего разряда. Называется оно полный

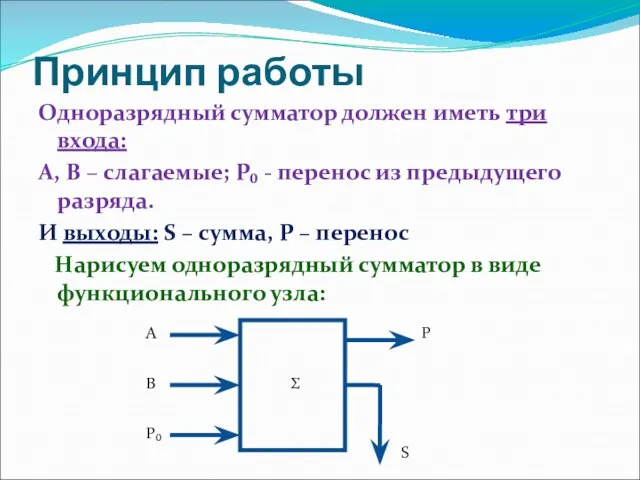

- 7. Принцип работы Одноразрядный сумматор должен иметь три входа: А, В – слагаемые; Р₀ - перенос из

- 8. Многоразрядный сумматор Но процессор, как правило складывает многоразрядные двоичные числа. Для того, чтобы вычислить сумму n-разрядных

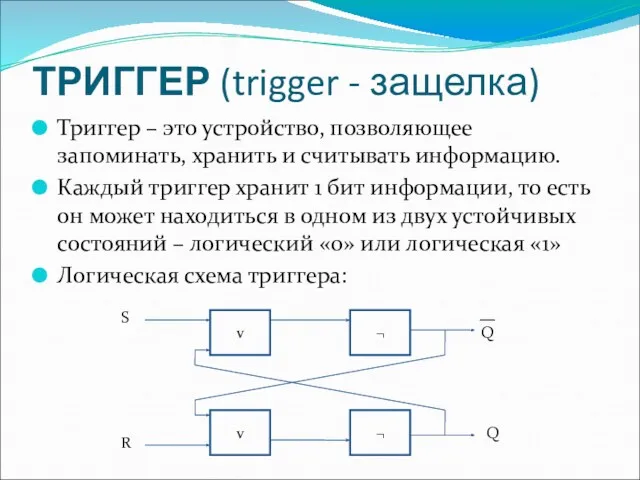

- 9. ТРИГГЕР (trigger - защелка) Триггер – это устройство, позволяющее запоминать, хранить и считывать информацию. Каждый триггер

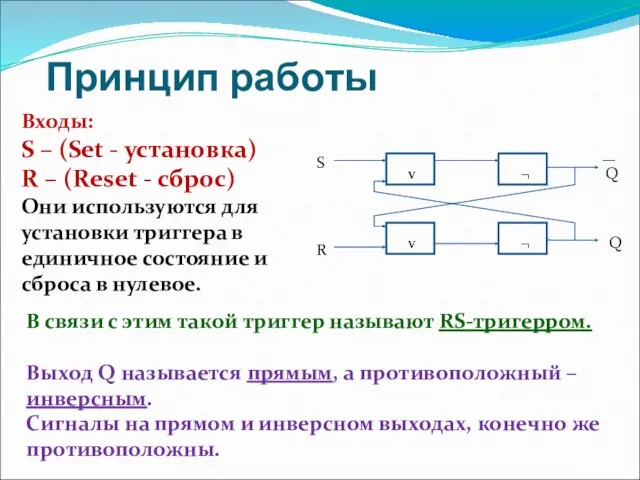

- 10. Принцип работы Входы: S – (Set - установка) R – (Reset - сброс) Они используются для

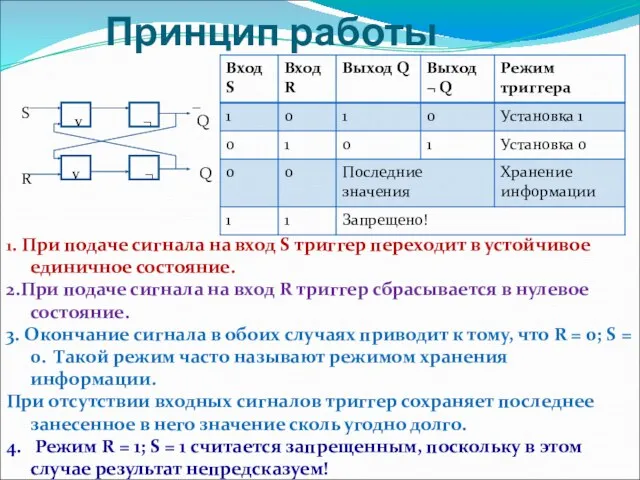

- 11. Принцип работы 1. При подаче сигнала на вход S триггер переходит в устойчивое единичное состояние. 2.При

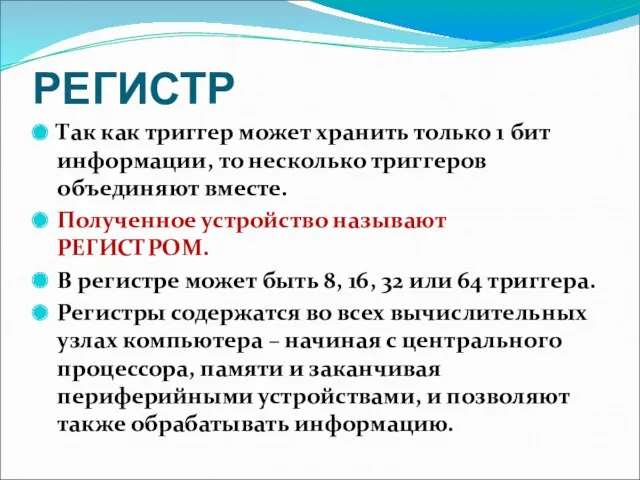

- 12. РЕГИСТР Так как триггер может хранить только 1 бит информации, то несколько триггеров объединяют вместе. Полученное

- 14. Скачать презентацию

Звездный час

Звездный час Азбука.

Азбука. Молекулярная биология. Достижения, проблемы и перспективы. (Лекция 13-а)

Молекулярная биология. Достижения, проблемы и перспективы. (Лекция 13-а) Клеточная теория. Методы цитологии

Клеточная теория. Методы цитологии Викторина Курск - любимый город!

Викторина Курск - любимый город! Т_Equines Cushing Syndrom (ECS) 19.05.2015

Т_Equines Cushing Syndrom (ECS) 19.05.2015 Моделювання і конструюваня зачісок

Моделювання і конструюваня зачісок Неорганические вещества клетки

Неорганические вещества клетки Рак гортани

Рак гортани Всероссийская стартап-школа молодого изобретателя

Всероссийская стартап-школа молодого изобретателя портфолио социального педагога

портфолио социального педагога Хеширование данных

Хеширование данных Крахмал

Крахмал Географическая мозаика

Географическая мозаика Склейка Ландыши

Склейка Ландыши Обеспечение предприятий автосервиса материально-техническими ресурсами. Материальные ресурсы. (Тема 9.15)

Обеспечение предприятий автосервиса материально-техническими ресурсами. Материальные ресурсы. (Тема 9.15) Клинико-фармакологическая экспертиза. Ошибки и необоснованные назначения

Клинико-фармакологическая экспертиза. Ошибки и необоснованные назначения Общие вопросы организации микропроцессорных систем

Общие вопросы организации микропроцессорных систем The grammar: Gerund

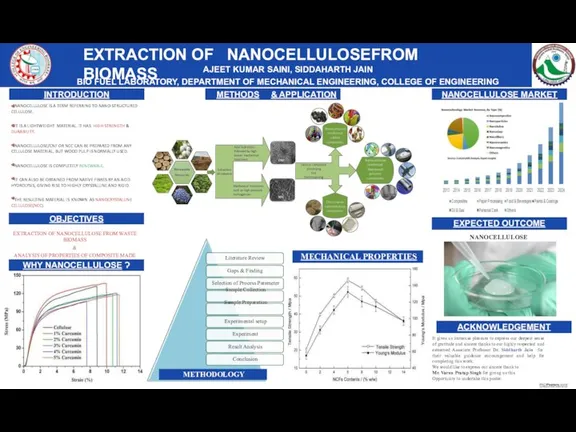

The grammar: Gerund Extraction of nanocellulose from biomass

Extraction of nanocellulose from biomass Философия средневековья

Философия средневековья Задачи, содержание и технологии образования умственно отсталых учащихся при изучении дисциплины Домоводство

Задачи, содержание и технологии образования умственно отсталых учащихся при изучении дисциплины Домоводство 8 марта

8 марта Найдём лишний предмет

Найдём лишний предмет Правила игры в волейбол

Правила игры в волейбол Классный час Брейн-ринг Твои права и обязанности

Классный час Брейн-ринг Твои права и обязанности Правила поведения и меры безопасности на льду в осенне-зимний период

Правила поведения и меры безопасности на льду в осенне-зимний период Молекулярная физика. Строение вещества

Молекулярная физика. Строение вещества