Слайд 2

2

Лекция 4. Комбинационные логические устройства. Арифметико-логические устройства (АЛУ)

Учебные вопросы:

Комбинационные логические устройства:

дешифраторы, шифраторы, мультиплексоры, демультиплексоры, сумматоры

Арифметико-логические устройства (АЛУ): применение, обобщенная структурная схема.

Слайд 3

3

Вопрос 1.

Комбинационные логические устройства

К комбинационным устройствам относятся функциональные узлы, в которых

отсутствуют элементы памяти.

Состояние комбинационного узла однозначно определяется комбинацией входных сигналов в данный момент и не зависит от предыдущего состояния.

К таким узлам относятся шифраторы, дешифраторы, сумматоры, мультиплексоры, демультиплексоры, компараторы, преобразователи кодов и другие.

Слайд 4

4

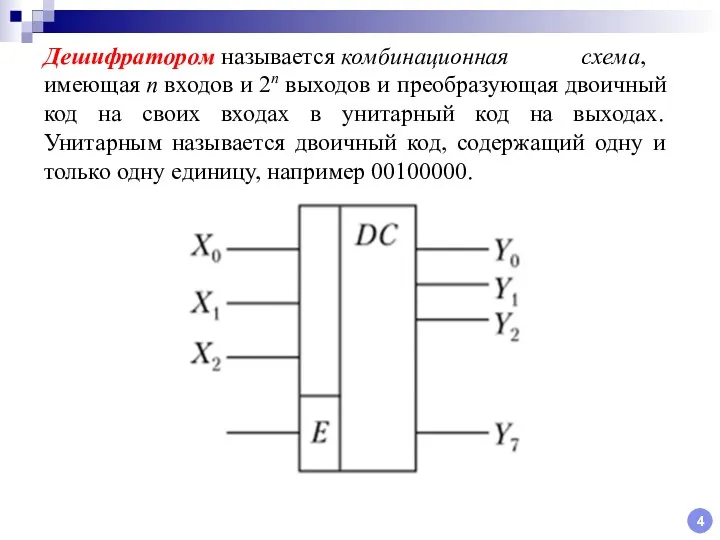

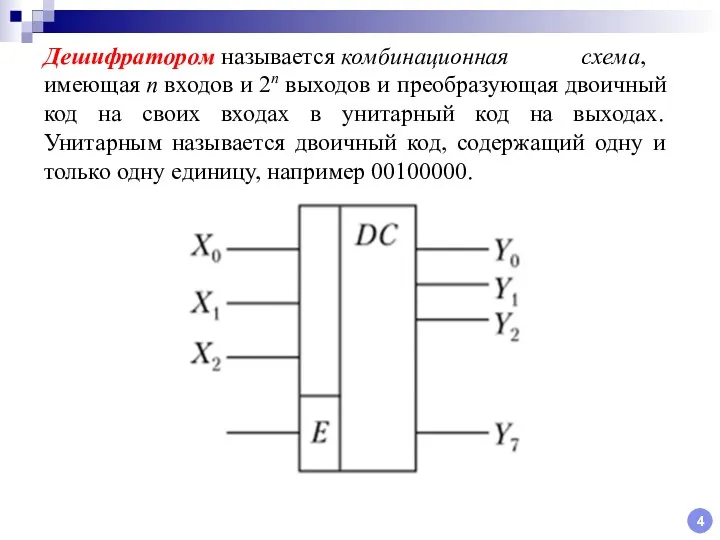

Дешифратором называется комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах

в унитарный код на выходах. Унитарным называется двоичный код, содержащий одну и только одну единицу, например 00100000.

Слайд 5

Слайд 6

6

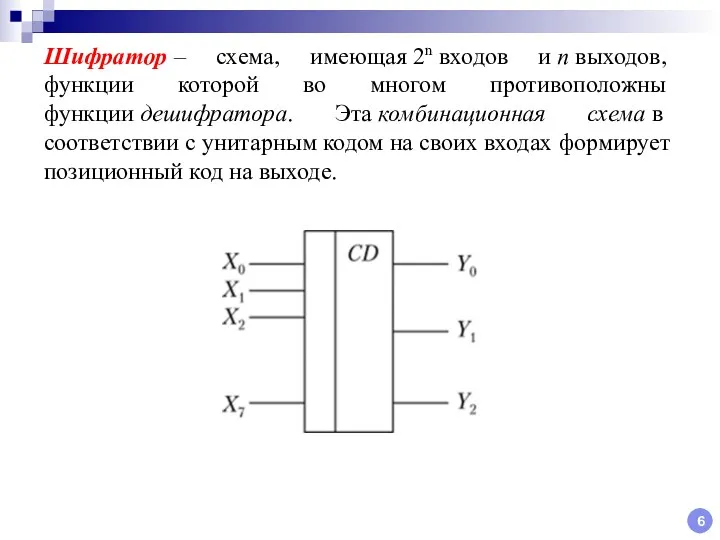

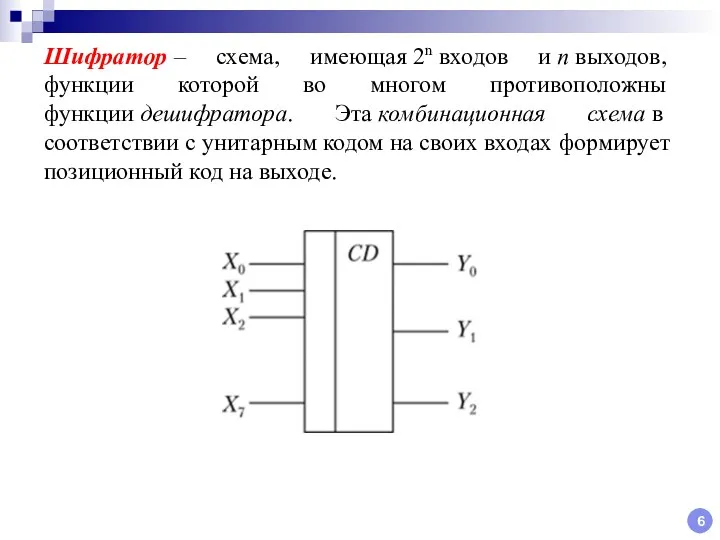

Шифратор – схема, имеющая 2n входов и n выходов, функции которой во многом противоположны функции дешифратора. Эта комбинационная

схема в соответствии с унитарным кодом на своих входах формирует позиционный код на выходе.

Слайд 7

7

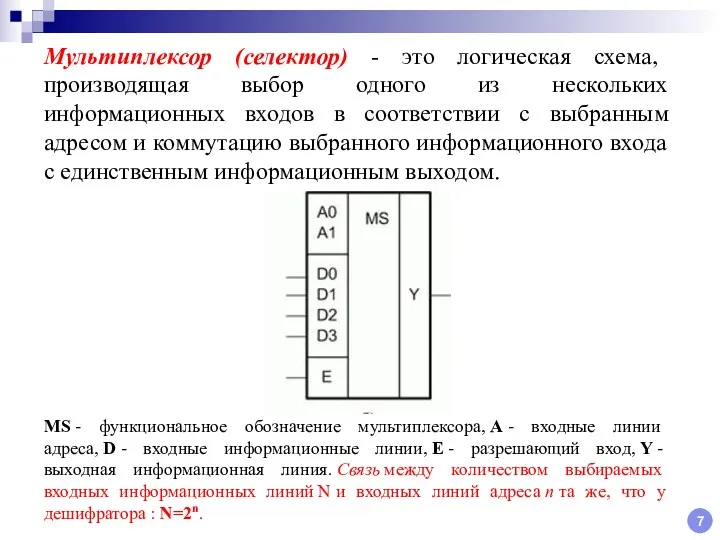

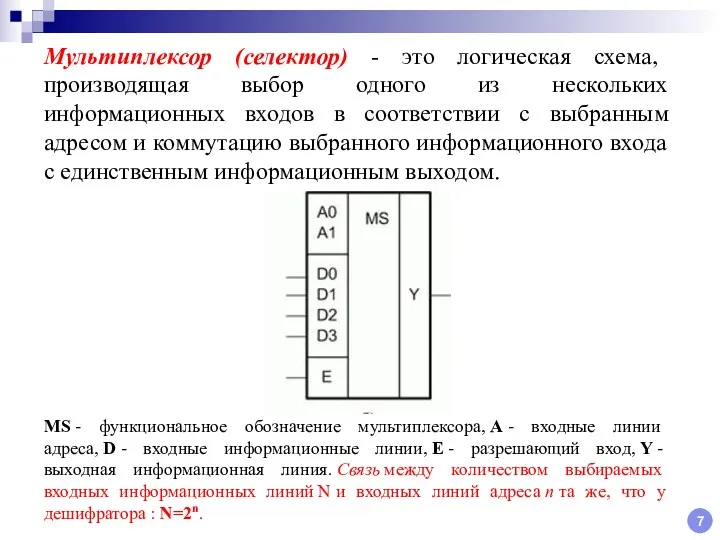

Мультиплексор (селектор) - это логическая схема, производящая выбор одного из нескольких

информационных входов в соответствии с выбранным адресом и коммутацию выбранного информационного входа с единственным информационным выходом.

MS - функциональное обозначение мультиплексора, А - входные линии адреса, D - входные информационные линии, Е - разрешающий вход, Y - выходная информационная линия. Связь между количеством выбираемых входных информационных линий N и входных линий адреса n та же, что у дешифратора : N=2n.

Слайд 8

8

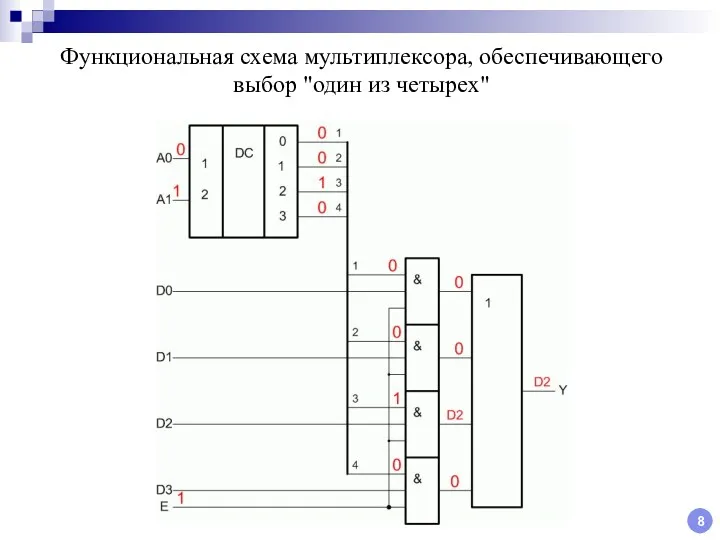

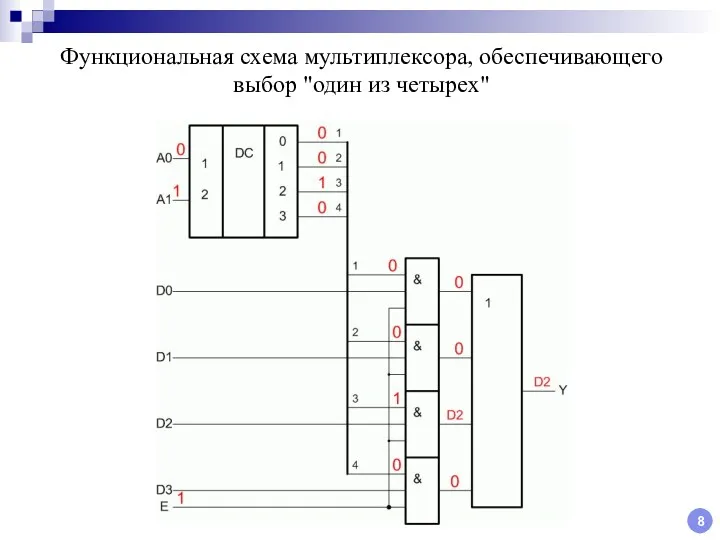

Функциональная схема мультиплексора, обеспечивающего выбор "один из четырех"

Слайд 9

9

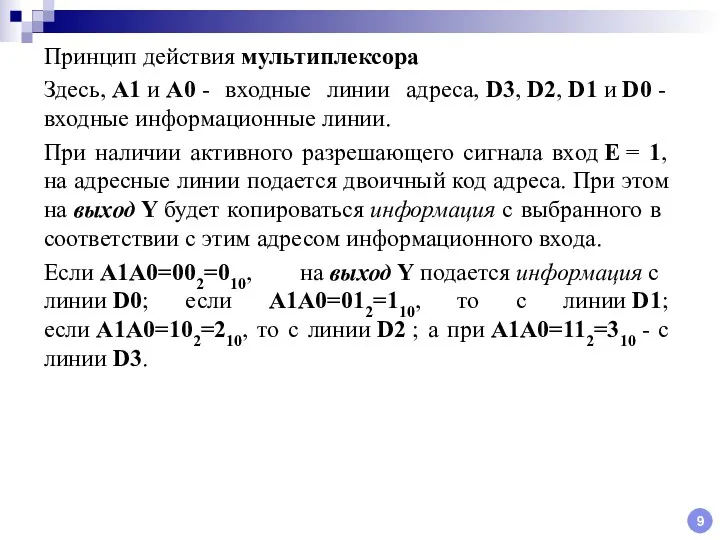

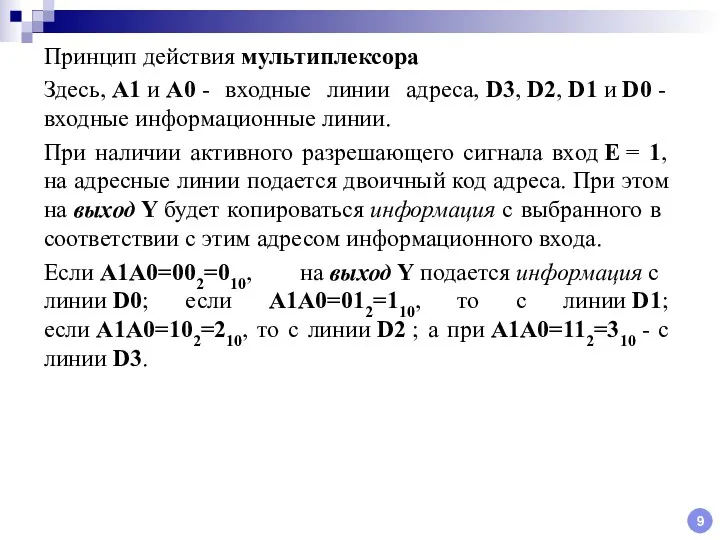

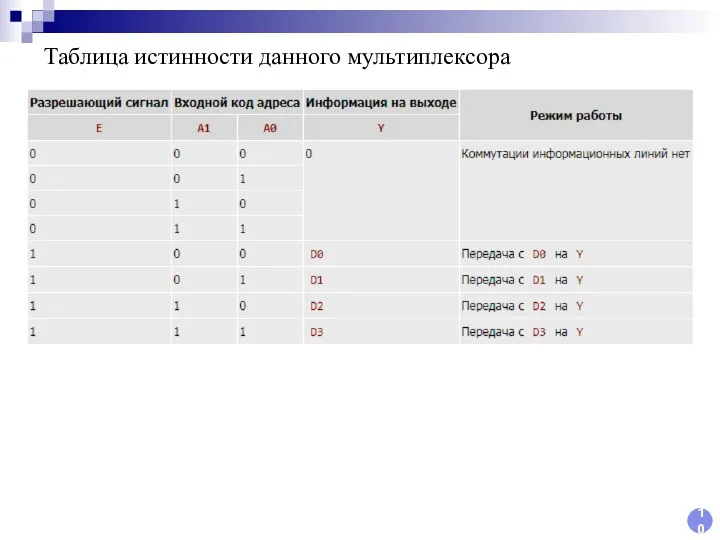

Принцип действия мультиплексора

Здесь, А1 и А0 - входные линии адреса, D3, D2, D1 и D0 - входные информационные линии.

При наличии активного разрешающего

сигнала вход Е = 1, на адресные линии подается двоичный код адреса. При этом на выход Y будет копироваться информация с выбранного в соответствии с этим адресом информационного входа.

Если А1А0=002=010, на выход Y подается информация с линии D0; если А1А0=012=110, то с линии D1; если А1А0=102=210, то с линии D2 ; а при А1А0=112=310 - с линии D3.

Слайд 10

10

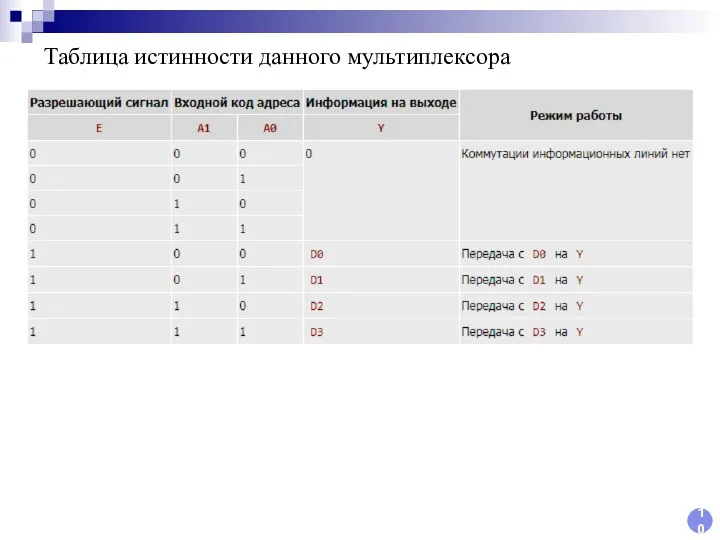

Таблица истинности данного мультиплексора

Слайд 11

11

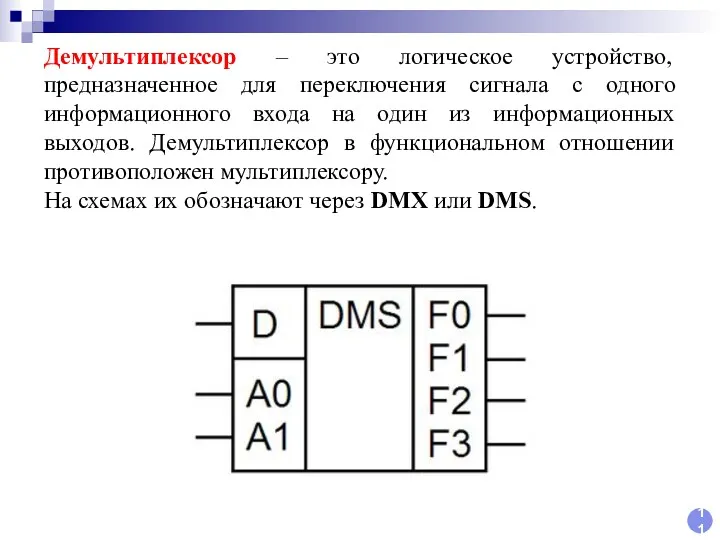

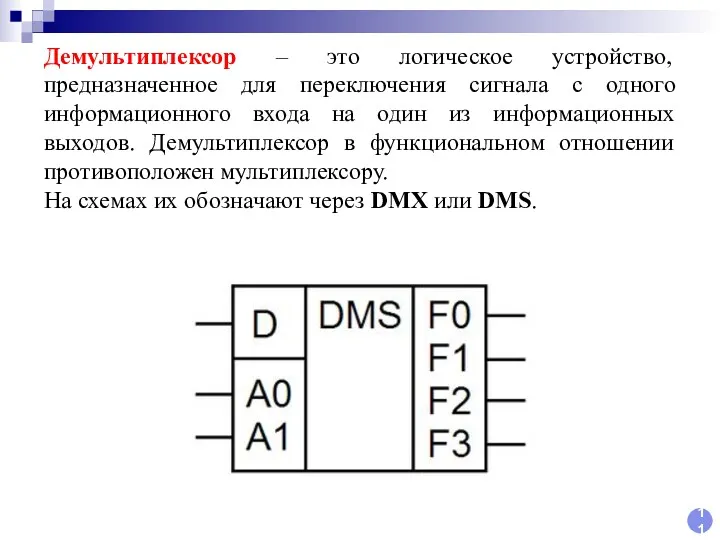

Демультиплексор – это логическое устройство, предназначенное для переключения сигнала с одного

информационного входа на один из информационных выходов. Демультиплексор в функциональном отношении противоположен мультиплексору.

На схемах их обозначают через DMX или DMS.

Слайд 12

13

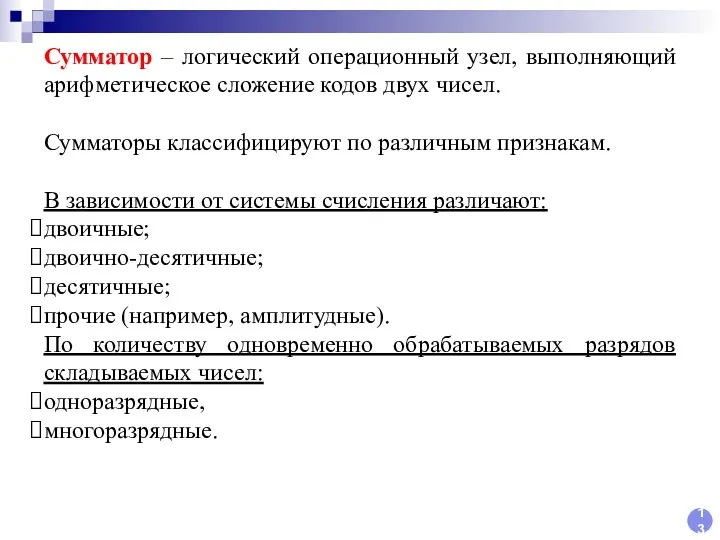

Сумматор – логический операционный узел, выполняющий арифметическое сложение кодов двух чисел.

Сумматоры

классифицируют по различным признакам.

В зависимости от системы счисления различают:

двоичные;

двоично-десятичные;

десятичные;

прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел:

одноразрядные,

многоразрядные.

Слайд 13

14

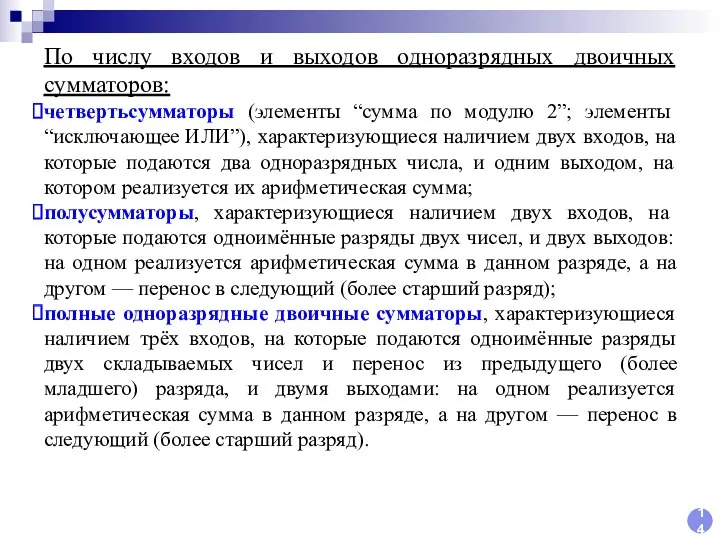

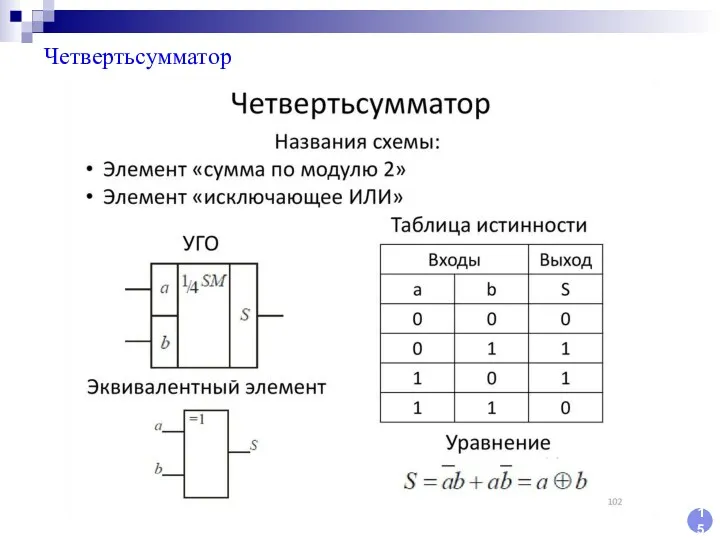

По числу входов и выходов одноразрядных двоичных сумматоров:

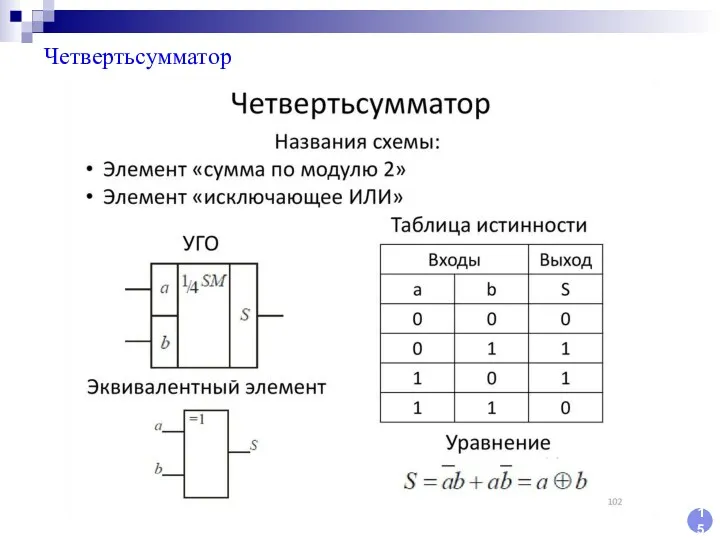

четвертьсумматоры (элементы “сумма по

модулю 2”; элементы “исключающее ИЛИ”), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

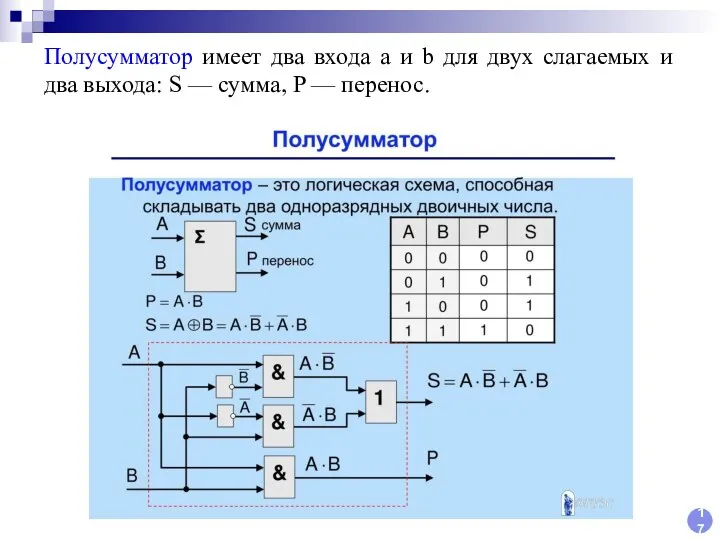

полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд);

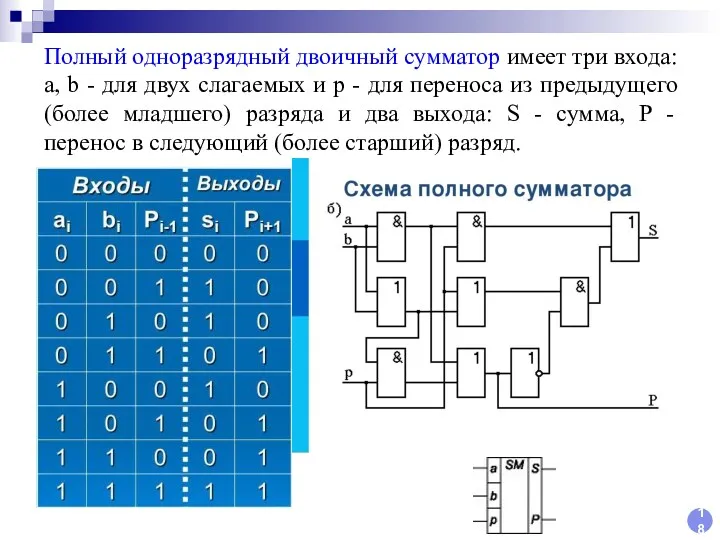

полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд).

Слайд 14

Слайд 15

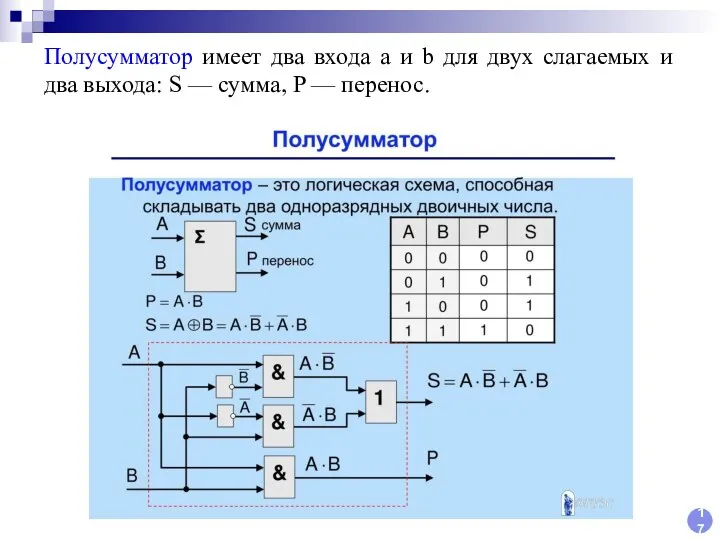

17

Полусумматор имеет два входа a и b для двух слагаемых и

два выхода: S — сумма, P — перенос.

Слайд 16

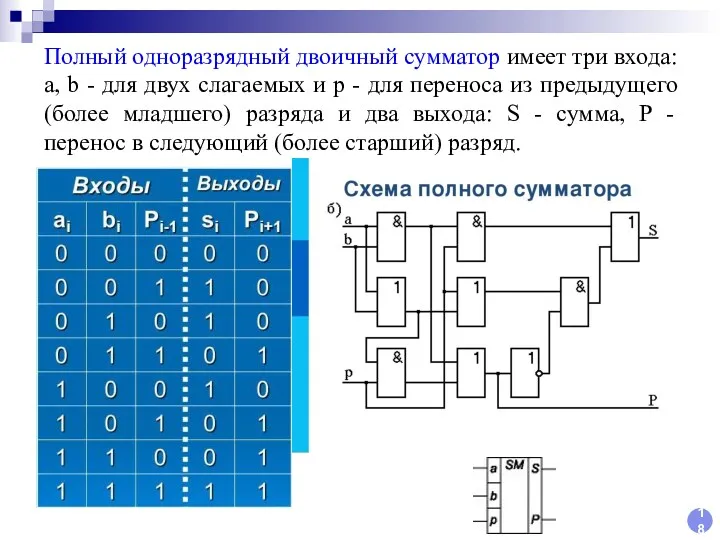

18

Полный одноразрядный двоичный сумматор имеет три входа: a, b - для

двух слагаемых и p - для переноса из предыдущего (более младшего) разряда и два выхода: S - сумма, P - перенос в следующий (более старший) разряд.

Слайд 17

19

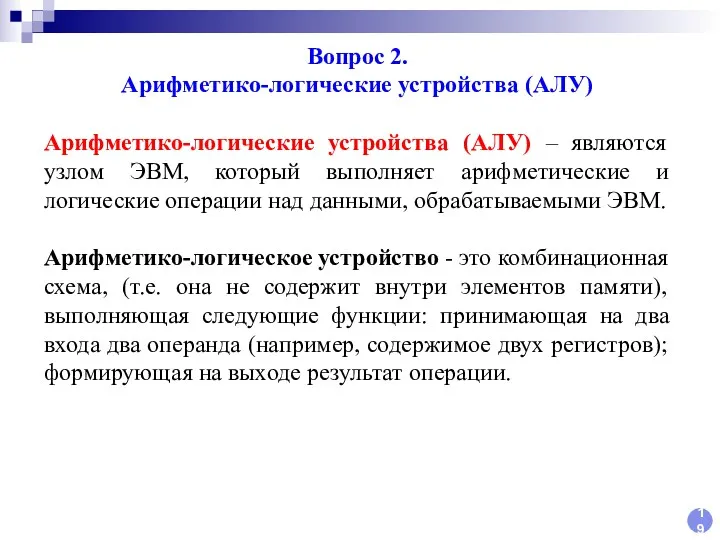

Вопрос 2.

Арифметико-логические устройства (АЛУ)

Арифметико-логические устройства (АЛУ) – являются узлом ЭВМ, который

выполняет арифметические и логические операции над данными, обрабатываемыми ЭВМ.

Арифметико-логическое устройство - это комбинационная схема, (т.е. она не содержит внутри элементов памяти), выполняющая следующие функции: принимающая на два входа два операнда (например, содержимое двух регистров); формирующая на выходе результат операции.

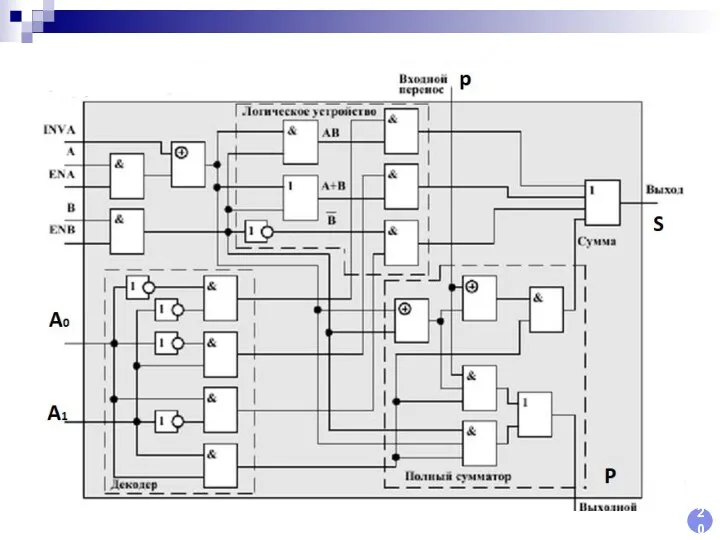

Слайд 18

Слайд 19

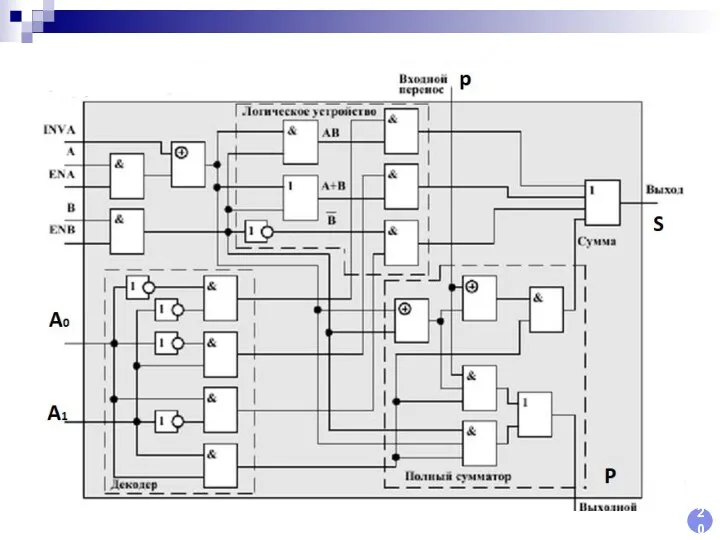

21

АЛУ выполняет одну из 4 следующих операций:

А И В (логич.

умножение);

А ИЛИ В (логич. сложение);

не В (инверсия по входу В);

А + В (арифметическая сумма А и В).

Выбор операции зависит от того, какие сигналы поступают на адресные входы А0 и А1: 00, 01, 10 или 11 (в двоичной системе счисления).

Новороссийский морской порт

Новороссийский морской порт Лоскутное шитье. Птичка с пасхальным яйцом

Лоскутное шитье. Птичка с пасхальным яйцом Ресурсный метод определения сметной стоимости строительно-монтажных работ

Ресурсный метод определения сметной стоимости строительно-монтажных работ Урок-сказка Обыкновенные дроби

Урок-сказка Обыкновенные дроби Особенности окраски полов. Лаки и эмали. Дефекты и способы их устранения

Особенности окраски полов. Лаки и эмали. Дефекты и способы их устранения Памятки по чтению

Памятки по чтению Второстепенные члены предложения. Повторение и систематизация материала

Второстепенные члены предложения. Повторение и систематизация материала Марка Рено

Марка Рено Туберкулез бронхов

Туберкулез бронхов Сочинения о Великой Отечественной Войне

Сочинения о Великой Отечественной Войне Использование ИКТ в учебном процессе (2008 г.)

Использование ИКТ в учебном процессе (2008 г.) Классификация химических реакций

Классификация химических реакций Понятие и классификация теорий менеджмента

Понятие и классификация теорий менеджмента Координатный луч. Изображение обыкновенных дробей на координатном луче

Координатный луч. Изображение обыкновенных дробей на координатном луче Практический аспект алгоритма решений корреляции

Практический аспект алгоритма решений корреляции Информационные ресурсы общества

Информационные ресурсы общества открытый урок Антарктида

открытый урок Антарктида Мой друг - Светофор

Мой друг - Светофор Нормативно-правовое обеспечение аттестации педагогических кадров

Нормативно-правовое обеспечение аттестации педагогических кадров Я выбираю профессию Реставратор

Я выбираю профессию Реставратор Экологически чистые решения для грузовых автомобилей среднего и большого размера. V-600 и V-800

Экологически чистые решения для грузовых автомобилей среднего и большого размера. V-600 и V-800 Prezentatsia_Ryabov_N (2)

Prezentatsia_Ryabov_N (2) Презентация для родительского собрания Полезный завтрак в моей семье

Презентация для родительского собрания Полезный завтрак в моей семье Геологиялық барлау кәсіпорнының қосалқы өндірістері мен қызмет көрсетуші шаруашылықтарын ұйымдастыру

Геологиялық барлау кәсіпорнының қосалқы өндірістері мен қызмет көрсетуші шаруашылықтарын ұйымдастыру Камерная инструментальная музыка. Соната

Камерная инструментальная музыка. Соната Каталог инструмента Вихрь

Каталог инструмента Вихрь Современные стратегии поддержки одарённых детей: вызовы и перспективы

Современные стратегии поддержки одарённых детей: вызовы и перспективы Искусство конца XIX – начала XX веков

Искусство конца XIX – начала XX веков