Содержание

- 2. Современные мировые тенденции развития ВТ и ИТ Экспоненциальный рост числа транзисторов в микропроцессорах Массовое использование параллелизма

- 3. Инновационные технологии Эльбрус Параллельная энергоэффективная архитектура 25-48 оп. за такт, явный параллелизм операций Высокая однопоточная производительность

- 4. Достижение высокой логической скорости МП линии «Эльбрус»

- 5. Почему важна производительность ядра Экспоненциально растущие транзисторы вкладываются в аппаратный параллелизм Параллелизм ядра ограничен многими факторами

- 6. Параллелизм на уровне операций Анализ трасс исполнения показывает значительный потенциал параллелизма Целочисленные задачи: 81 - 240

- 7. Параллелизм архитектуры «Эльбрус» Параллелизм скалярных операций До 30 операций за такт в разрабатываемых МП До 40-50

- 8. Структура ядра МП линии Эльбрус 2 кластера IB –буфер команд (I$L1) CU – устр. управления PF

- 9. Пиковая производительность ядра лин.уч. циклы Int (8) / FP (9/12) / St (2) / Ld (4)

- 10. Одновременный запуск большого числа операций Большие регистровый и предикатный файлы Окна произвольного размера – экономия регистров

- 11. Параллелизм МП «Эльбрус» и суперскалярного МП Анализатор зависимостей, Перекодировщик операций, Планировщик, Распределитель регистров Суперскалярный МП Последовательный

- 12. Параллелизм операций (1) u = (a – c) – (b + c) – (c + d);

- 13. Параллелизм операций (2) u = (a – c) – (b + c) – (c + d);

- 14. Параллелизм операций (3) 1 2 3 4 5 6 7 8 9 10 11 12 13

- 15. Параллелизм операций (4) 1 3 8 2 9 16 4 11 20 22 5 6 12

- 16. Конвейеризованные циклы Переименование регистров в цикле Поддержка пролога и эпилога Спекулятивные вычисления и предикаты

- 17. Распараллеливание программ Компиляторы обеспечивают эффективное распараллеливание на уровне операций

- 18. Асинхронная подкачка данных

- 19. Исходный код SpMV (CSR) double A[size]; // Разреженная матрица в формате CSR double x[N]; // Вектор

- 20. Код Эльбруса для SpMV (CSR) { ! Подготовка внешнего цикла, начало конвейера } {! Внешний цикл

- 21. Архитектура и производительность МП: HPL & HPCG *) Задача HPCG предложена автором Linpack Донгаррой как более

- 22. Рост производительности за счет компилятора Производительность ядра Эльбрус существенно зависит от оптимизирующего компилятора На текущей версии

- 23. Обеспечение безопасности и надежности на базе МП линии «Эльбрус»

- 24. Существо защищенного исполнения Защита в МП «Эльбрус» Все указатели на объекты защищены тегами Подделать указатель невозможно

- 25. Защищенное исполнение программ Защищенное исполнение программ Защита памяти с помощью тегов Структурированная память Доступ к объектам

- 26. Обеспечение совместимости на базе МП линии «Эльбрус»

- 27. Двоичная трансляция для совместимости Обеспечивает эффективную совместимость за счет использования параллелизма

- 28. Параллелизм операций (5) 1 3 8 2 9 16 4 11 20 22 5 6 12

- 29. Эффективная двоичная совместимость с Intel x86, x64 Функциональность Полная совместимость с архитектурой Intel x86 (x86-64 с

- 30. Изделия на базе микропроцессоров с архитектурой «Эльбрус»

- 31. Изделия на базе МП Эльбрус-4С Настольный компьютер Сервер приложений Система хранения данных Сервер баз данных

- 32. Сервер и шкаф на МП Эльбрус-4С с воздушным охлаждением Характеристики сервера (узла) и шкафа Производительность, Тфлопс

- 33. Сервер на МП Эльбрус-8С с воздушным охлаждением Характеристики сервера (узла) и шкафа Производительность, Тфлопс – 0,5

- 34. ОПО Эльбрус Собственная программа начального старта (BIOS) Ядро базируется на ОС Linux со встроенными средствами защиты

- 35. Развитие МП линии «Эльбрус» и компьютеров на них

- 36. Развитие серверных МП линии «Эльбрус» На базе новых МП проектируются компьютеры и программное обеспечение Эльбрус-4C 0.8

- 37. МП Эльбрус-8СВ Госконтракт с Минпромторгом РФ. Сроки завершения: 2018 г. стадия разработки – готовность к первому

- 38. Решения на базе технологий «РСК-торнадо» Масштабируемая серверная система с водяным охлаждением на Э8С / Э16С Производительность,

- 39. Особенности МП Эльбрус-16С Характеристики МП: производительность - до 1500 / 750 Gflops (sp/dp); количество ядер –

- 40. СПАСИБО за внимание!

- 41. Проблемы кремниевой технологии «Закон» Мура дает сбои с середины нулевых остановился рост тактовой частоты из-за мощности

- 43. Скачать презентацию

Мои достижения

Мои достижения Родительское собрание 5 класс

Родительское собрание 5 класс Электрические аппараты и приборы, электрические цепи тепловоза, электрические цепи электровоза

Электрические аппараты и приборы, электрические цепи тепловоза, электрические цепи электровоза Организация деятельности аптеки

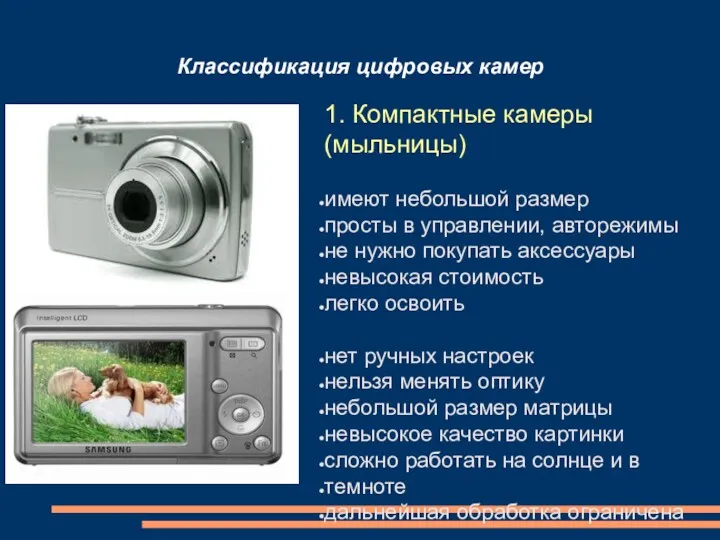

Организация деятельности аптеки Классификация цифровых камер

Классификация цифровых камер Рентгенодиагностика опухолей головного мозга

Рентгенодиагностика опухолей головного мозга Технология проектирования ключевых и предметных компетенций

Технология проектирования ключевых и предметных компетенций Синхронные машины. Устройство и принцип действия

Синхронные машины. Устройство и принцип действия История школы №25 г. Пермь

История школы №25 г. Пермь Территориальное общественное самоуправление в России: анализ современной практики

Территориальное общественное самоуправление в России: анализ современной практики Health Care systems using machine learning algorithms

Health Care systems using machine learning algorithms Редактирование текста

Редактирование текста Коммерческое предложение на поставку автопогрузчика CHERY грузоподъемностью 3,5т

Коммерческое предложение на поставку автопогрузчика CHERY грузоподъемностью 3,5т Как должно быть построено сочинение? ОГЭ 9

Как должно быть построено сочинение? ОГЭ 9 Агропромышленный комплекс. Растениеводство

Агропромышленный комплекс. Растениеводство 20231003_present_and_past_simple

20231003_present_and_past_simple Составление проектов бюджетов. Полномочия финансовых органов на разных этапах составления бюджетов

Составление проектов бюджетов. Полномочия финансовых органов на разных этапах составления бюджетов Волонтерский корпус 70-летия победы в Великой отечественной войне в городе Севастополе

Волонтерский корпус 70-летия победы в Великой отечественной войне в городе Севастополе Презентация Всемирный день снега

Презентация Всемирный день снега Памятка по оформлению краткой записи к задачам

Памятка по оформлению краткой записи к задачам Строительная теплотехника. Виды теплопередачи. Уравнение теплопроводности. Теплообмен на поверхностях ограждения. (Лекция 2)

Строительная теплотехника. Виды теплопередачи. Уравнение теплопроводности. Теплообмен на поверхностях ограждения. (Лекция 2) Европа в XIX веке

Европа в XIX веке материалы для педсовета Девиантное поведение

материалы для педсовета Девиантное поведение Основы медицинских знаний

Основы медицинских знаний Презентация Путешествие в зиму

Презентация Путешествие в зиму Культура и природа. Учение о ноосфере В.И. Вернадского. Экологическое сознание Востока и Запада

Культура и природа. Учение о ноосфере В.И. Вернадского. Экологическое сознание Востока и Запада Арифметическая и геометрическая прогрессии

Арифметическая и геометрическая прогрессии Теория организации и организационное поведение. Базовые понятия. Основные проблемы. Школы и концепции

Теория организации и организационное поведение. Базовые понятия. Основные проблемы. Школы и концепции