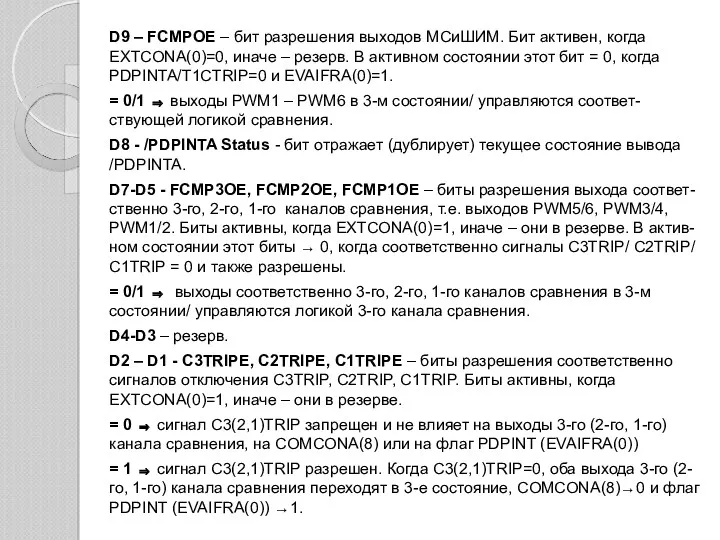

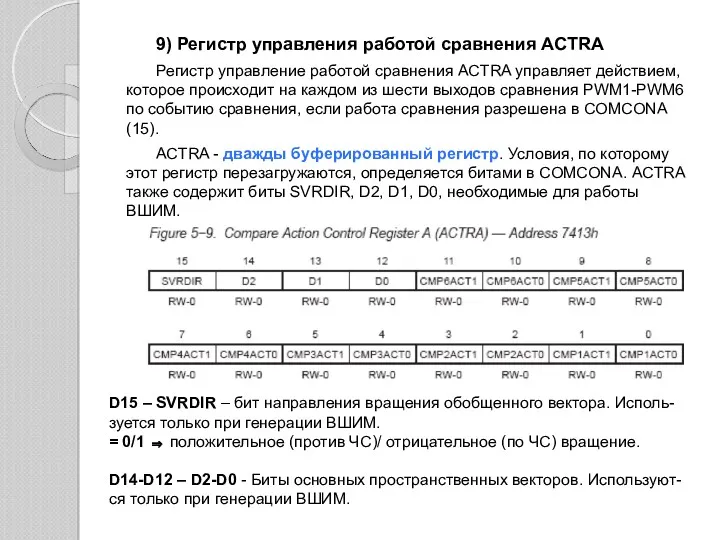

9) Регистр управления работой сравнения ACTRА

Регистр управление работой сравнения ACTRA

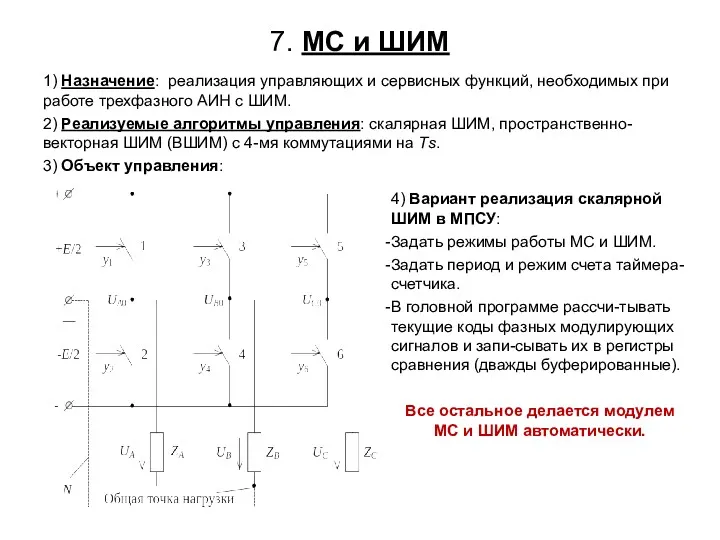

управляет действием, которое происходит на каждом из шести выходов сравнения PWM1-PWM6 по событию сравнения, если работа сравнения разрешена в COMCONА(15).

ACTRA - дважды буферированный регистр. Условия, по которому этот регистр перезагружаются, определяется битами в COMCONА. ACTRA также содержит биты SVRDIR, D2, D1, D0, необходимые для работы ВШИМ.

D15 – SVRDIR – бит направления вращения обобщенного вектора. Исполь-зуется только при генерации ВШИМ.

= 0/1 ⇒ положительное (против ЧС)/ отрицательное (по ЧС) вращение.

D14-D12 – D2-D0 - Биты основных пространственных векторов. Используют-ся только при генерации ВШИМ.

Расчет пневматической прессовой формовочной машины

Расчет пневматической прессовой формовочной машины АЛС и САУТ Автоматическая локомотивная сигнализация с автостопом

АЛС и САУТ Автоматическая локомотивная сигнализация с автостопом Тимуровское движение

Тимуровское движение Работа КМ 394 в III положении

Работа КМ 394 в III положении Показатели специализации Костромской области

Показатели специализации Костромской области Жарка мяса

Жарка мяса What is Customer Journey Framework (CJF)?

What is Customer Journey Framework (CJF)? Іріңді паротит. Мастит. Парапроктит, лимфангаит, лимфаденит,тромбофлебит

Іріңді паротит. Мастит. Парапроктит, лимфангаит, лимфаденит,тромбофлебит Новації вступної кампанії 2016

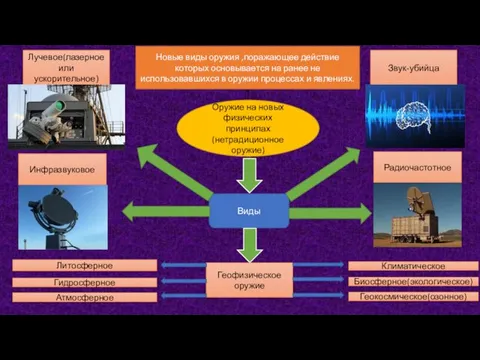

Новації вступної кампанії 2016 Новые виды оружия

Новые виды оружия Тропинками былинных героев. Задания

Тропинками былинных героев. Задания Презентация На зарядку становись! Диск

Презентация На зарядку становись! Диск Названия животных в Псалтири

Названия животных в Псалтири Подбор оборудования для центрального офиса

Подбор оборудования для центрального офиса Форсайт - сессия. Ресурсы системной оптимизации УдГУ

Форсайт - сессия. Ресурсы системной оптимизации УдГУ Методы и модели анализа и оценки инвестиционных проектов

Методы и модели анализа и оценки инвестиционных проектов Цели математического образования

Цели математического образования Презентация День рождения у Мишутки

Презентация День рождения у Мишутки Системы жизнеобеспечения. Системы водоснабжения. Инновационный центр Энергоэффективность, г. Иркутск

Системы жизнеобеспечения. Системы водоснабжения. Инновационный центр Энергоэффективность, г. Иркутск Барышня-крестьянка.Характеры героев (к аттестации)

Барышня-крестьянка.Характеры героев (к аттестации) Утренник Прощай, 2 класс!

Утренник Прощай, 2 класс! О состоянии наркоситуации на территории Мурманской области

О состоянии наркоситуации на территории Мурманской области Страдательный залог

Страдательный залог Спортивная подготовка туриста

Спортивная подготовка туриста Знакомство с Библией

Знакомство с Библией Анализ качества технологических процессов с помощью гистограмм

Анализ качества технологических процессов с помощью гистограмм Устройства электропривода для РЭУ и ТКС

Устройства электропривода для РЭУ и ТКС класс

класс