Содержание

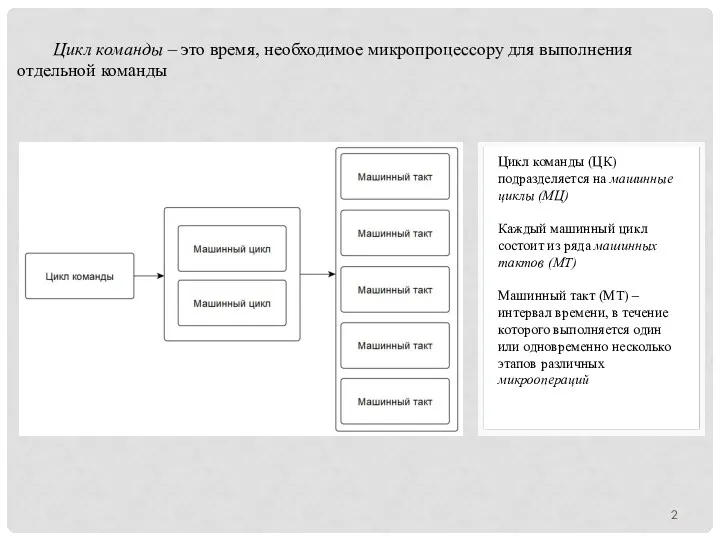

- 2. Цикл команды – это время, необходимое микропроцессору для выполнения отдельной команды

- 3. ЛЕКЦИЯ 3. ПАМЯТЬ МПС Выполнил: Провоторов Н.В. Москва 2018

- 4. Большинство современных микроконтроллеров имеют Гарвардскую архитектуру и содержат 3 вида памяти: Память программ (ПЗУ). 2. Память

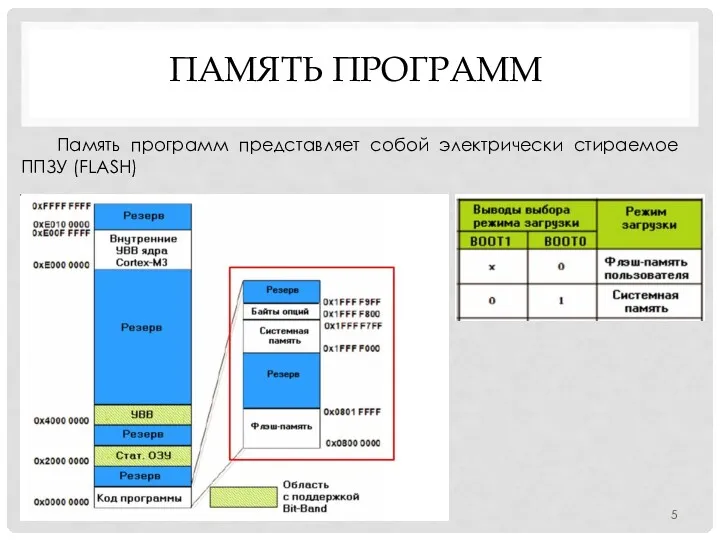

- 5. ПАМЯТЬ ПРОГРАММ Память программ представляет собой электрически стираемое ППЗУ (FLASH)

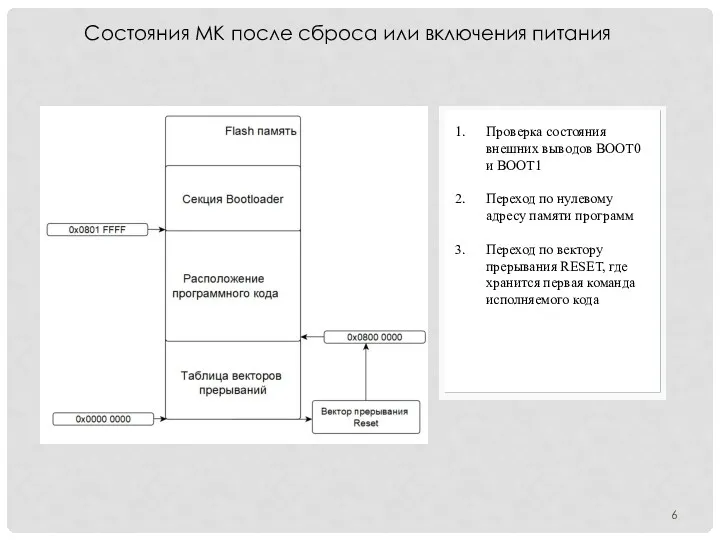

- 6. Состояния МК после сброса или включения питания

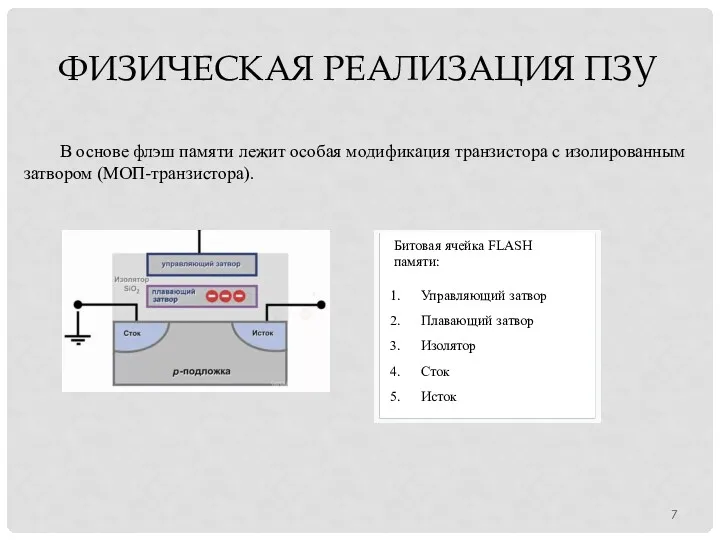

- 7. ФИЗИЧЕСКАЯ РЕАЛИЗАЦИЯ ПЗУ В основе флэш памяти лежит особая модификация транзистора с изолированным затвором (МОП-транзистора).

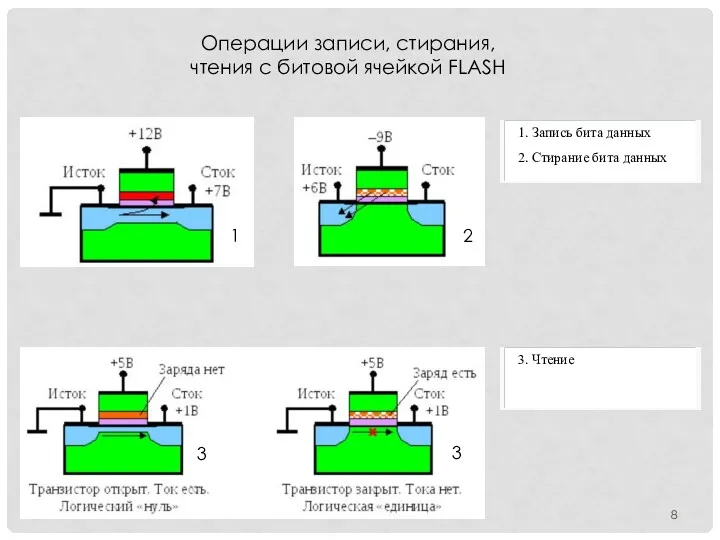

- 8. Операции записи, стирания, чтения с битовой ячейкой FLASH 1 2 3 3

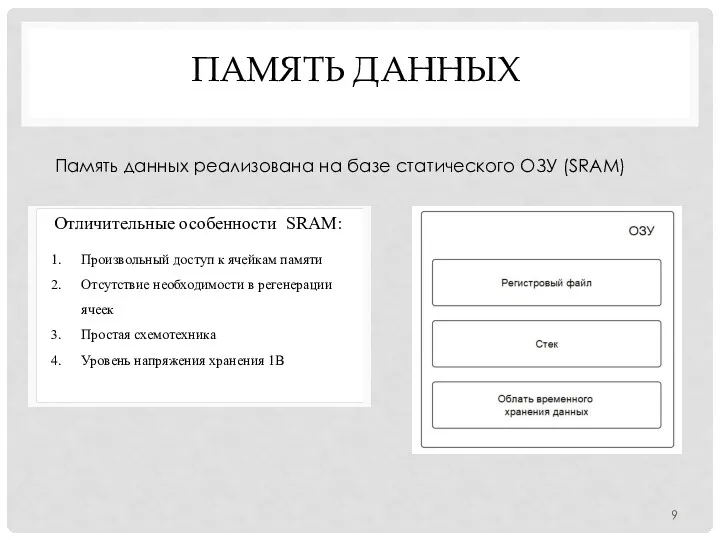

- 9. ПАМЯТЬ ДАННЫХ Память данных реализована на базе статического ОЗУ (SRAM)

- 10. ФИЗИЧЕСКАЯ РЕАЛИЗАЦИЯ ОЗУ Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии.

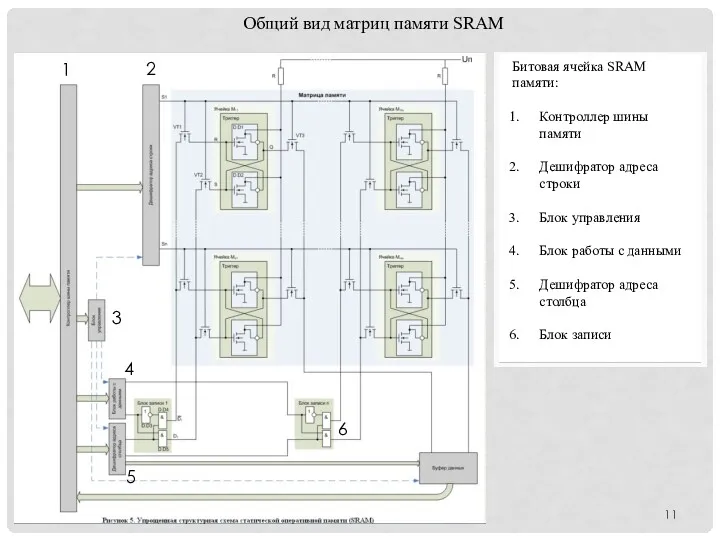

- 11. Общий вид матриц памяти SRAM 1 2 3 4 5 6

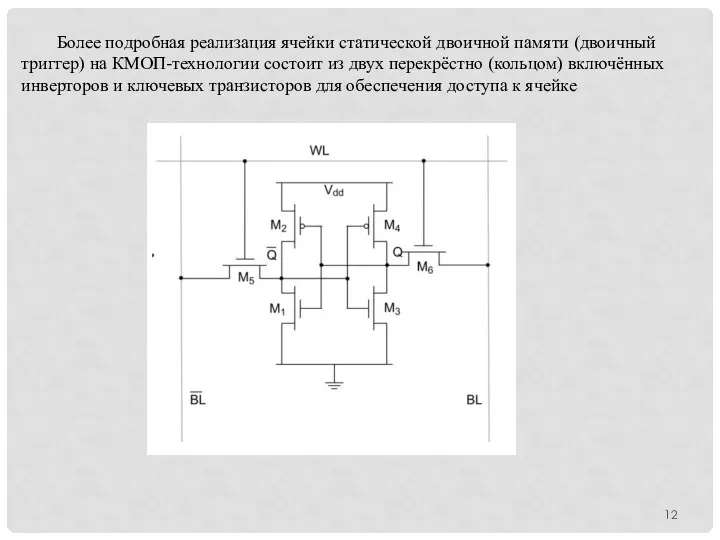

- 12. Более подробная реализация ячейки статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрёстно (кольцом)

- 13. РЕГИСТРЫ МК Регистры МК также выступают в качестве одного из видов памяти В число этих регистров

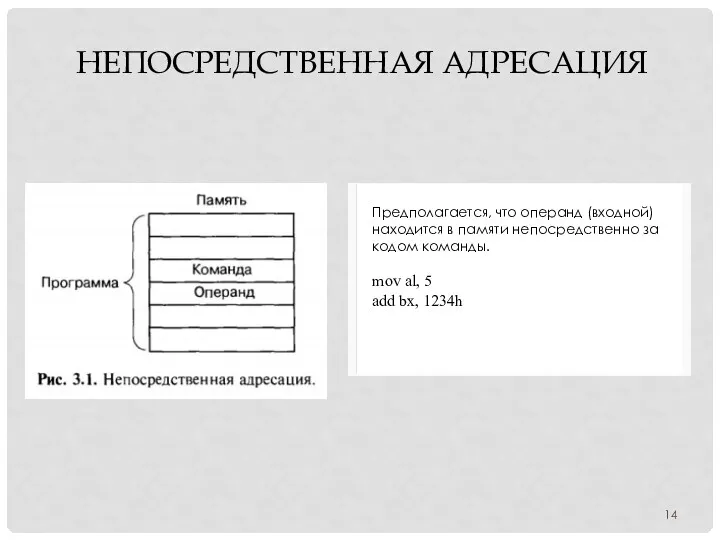

- 14. НЕПОСРЕДСТВЕННАЯ АДРЕСАЦИЯ

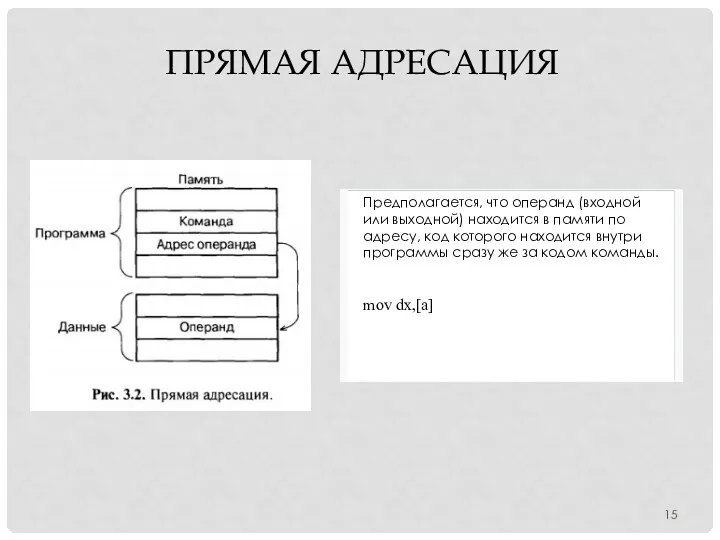

- 15. ПРЯМАЯ АДРЕСАЦИЯ

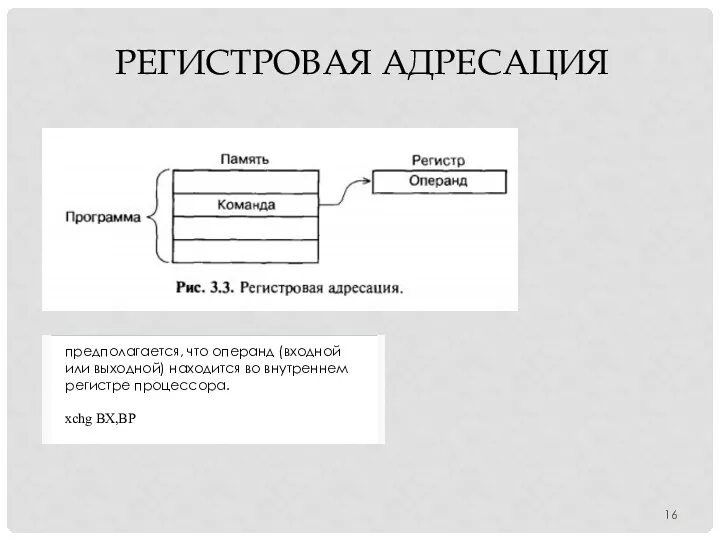

- 16. РЕГИСТРОВАЯ АДРЕСАЦИЯ

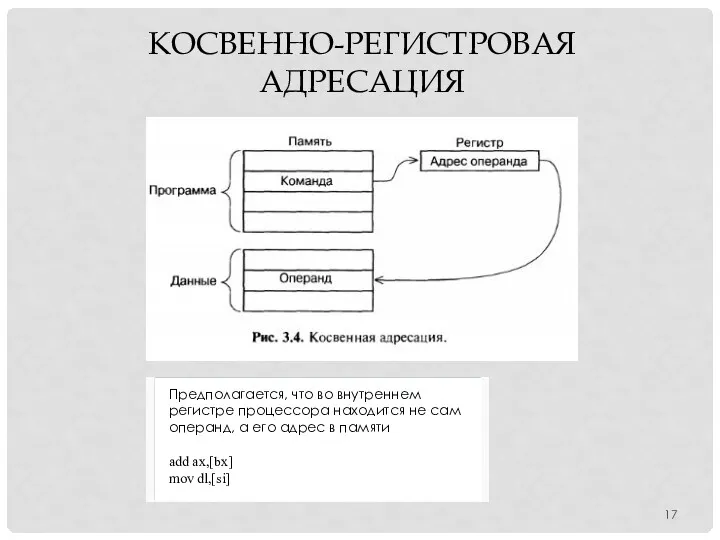

- 17. КОСВЕННО-РЕГИСТРОВАЯ АДРЕСАЦИЯ

- 19. Скачать презентацию

организация работы с родителями по соблюдению прав ребенка

организация работы с родителями по соблюдению прав ребенка Внеклассное мероприятие (презентация) для учащихся 6 класса Командная географическая игра Богатства недр Земли

Внеклассное мероприятие (презентация) для учащихся 6 класса Командная географическая игра Богатства недр Земли Положение металлов в Периодической системе Д.И. Менделеева. Особенности строения атомов, свойства. Цель и задачи урока: Форма урока: Методы и приёмы: Оборудование: ХОД УРОКА

Положение металлов в Периодической системе Д.И. Менделеева. Особенности строения атомов, свойства. Цель и задачи урока: Форма урока: Методы и приёмы: Оборудование: ХОД УРОКА Ship’s Stability. Final Examination Var. III

Ship’s Stability. Final Examination Var. III Конструювання одягу з трикотажу. (Частина 3)

Конструювання одягу з трикотажу. (Частина 3) Невротикалық бұзылулардың психогигенасы мен психопрофилактикасы

Невротикалық бұзылулардың психогигенасы мен психопрофилактикасы Текстиль. Виды текстиля

Текстиль. Виды текстиля Aluminium – the Most Abundant Metals

Aluminium – the Most Abundant Metals Правила проведения ремонта подъездов администрациями муниципальных образований

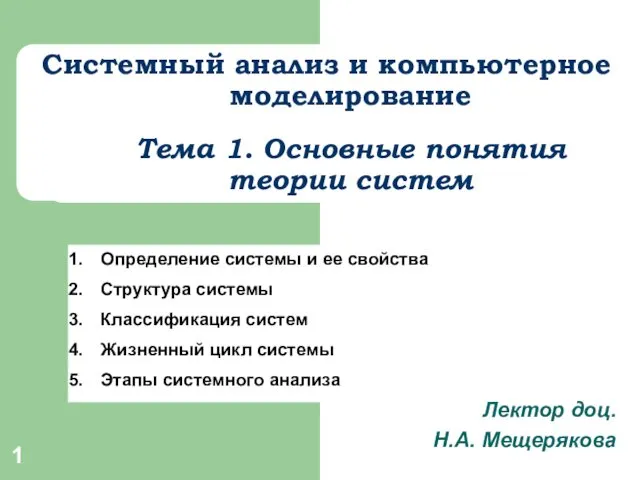

Правила проведения ремонта подъездов администрациями муниципальных образований Системный анализ и компьютерное моделирование. Основные понятие теории систем. (Лекция 1)

Системный анализ и компьютерное моделирование. Основные понятие теории систем. (Лекция 1) Земляные работы

Земляные работы Космические снимки

Космические снимки Мастер-класс по оригами. Цветы. Лилия.

Мастер-класс по оригами. Цветы. Лилия. Ice mechanics. Ice interface properties

Ice mechanics. Ice interface properties Готовимся к ВПР. 6 класс (за 5 класс)

Готовимся к ВПР. 6 класс (за 5 класс) Классификация стен

Классификация стен Introduction to Programming

Introduction to Programming Складки и шатры

Складки и шатры Презентация Проектная деятельность в детском саду

Презентация Проектная деятельность в детском саду Общая характеристика административных правонарушений в области таможенного дела

Общая характеристика административных правонарушений в области таможенного дела Сложные предложения с разными видами связи

Сложные предложения с разными видами связи Интерпретация рентгенограмм

Интерпретация рентгенограмм Elementary Class by Slidesgo

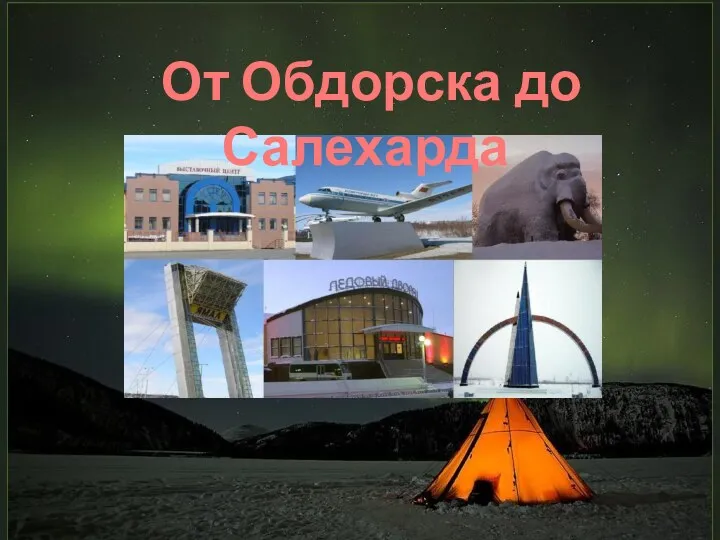

Elementary Class by Slidesgo Методическая разработка внеклассного мероприятия От Обдорска до Салехарда

Методическая разработка внеклассного мероприятия От Обдорска до Салехарда Земля и ее внутреннее строение.

Земля и ее внутреннее строение. Исследовательский проект Кристаллы

Исследовательский проект Кристаллы Усиление Московского княжества в XIV веке

Усиление Московского княжества в XIV веке Евразия. Географическое положение (приложение)

Евразия. Географическое положение (приложение)