Содержание

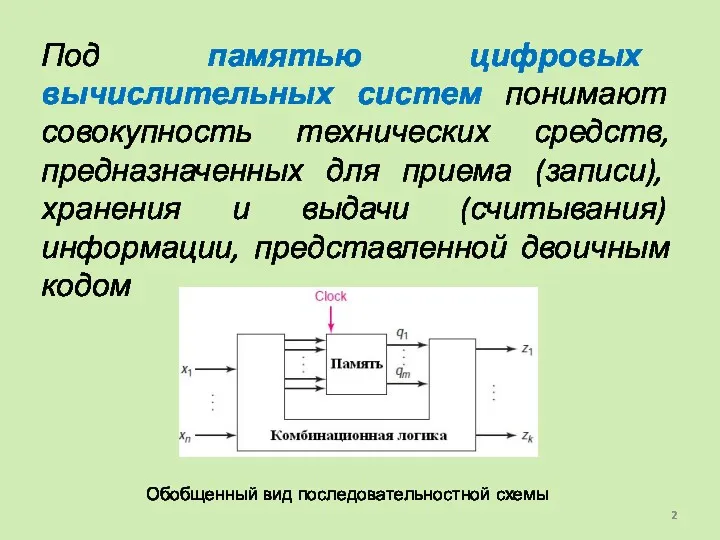

- 2. Под памятью цифровых вычислительных систем понимают совокупность технических средств, предназначенных для приема (записи), хранения и выдачи

- 3. Основные характеристики запоминающих устройств (ЗУ) информационная емкость, определяемая максимальным объемом хранимой информации в битах или байтах

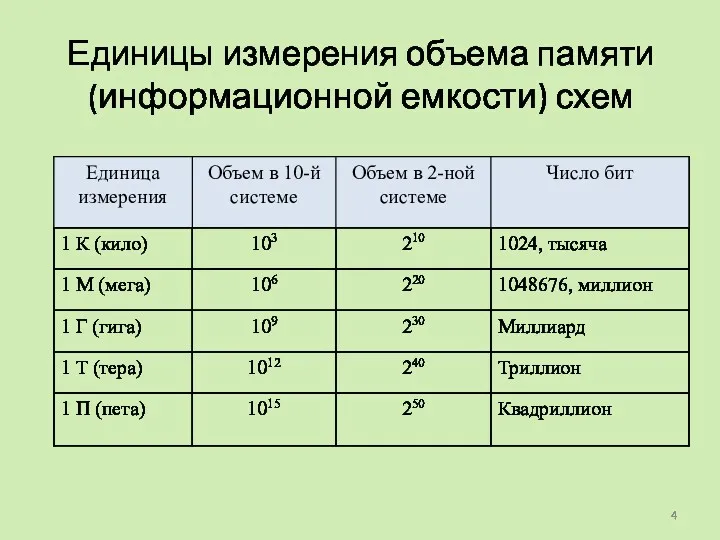

- 4. Единицы измерения объема памяти (информационной емкости) схем

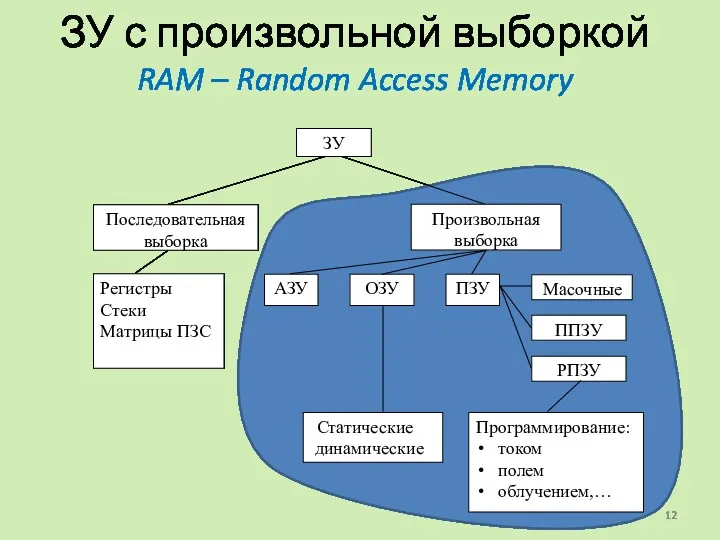

- 5. Классификация полупроводниковых ЗУ Основной признак приклассификации ЗУ – способ доступа к ячейкам памяти

- 6. Классификация по способу выборки информации ЗУ с последовательной выборкой – данные из ячеек выбираются в определенной

- 7. ЗУ с последовательной выборкой SERIAL-ACCESS MEMORY

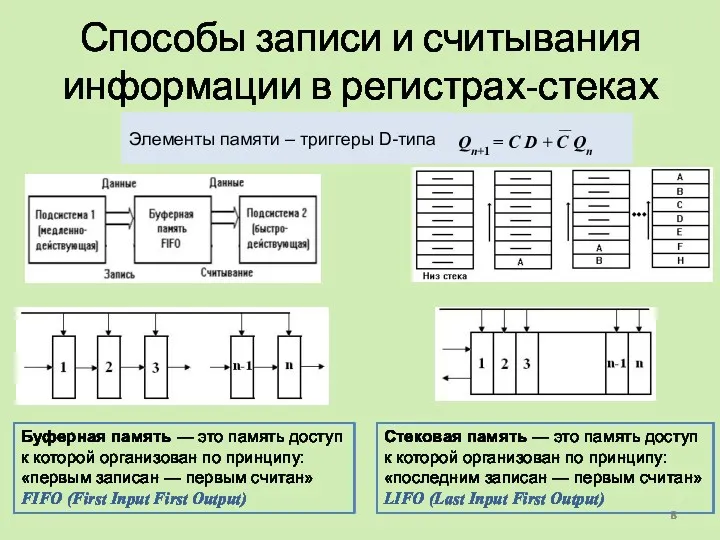

- 8. Способы записи и считывания информации в регистрах-стеках Стековая память — это память доступ к которой организован

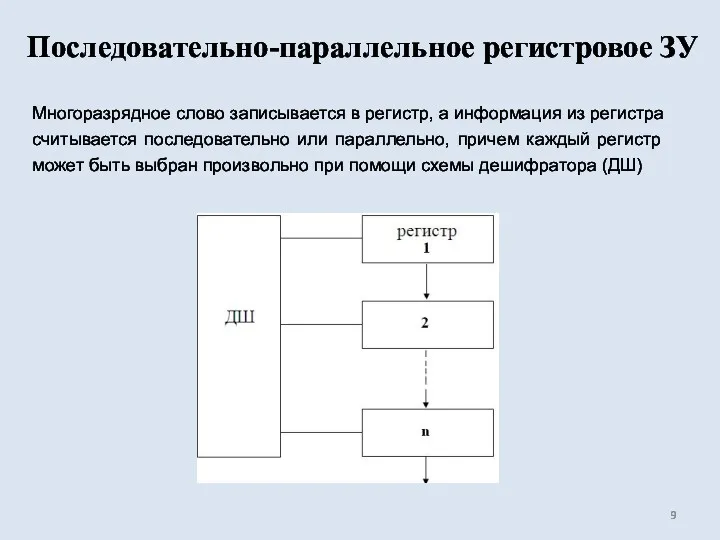

- 9. Последовательно-параллельное регистровое ЗУ Многоразрядное слово записывается в регистр, а информация из регистра считывается последовательно или параллельно,

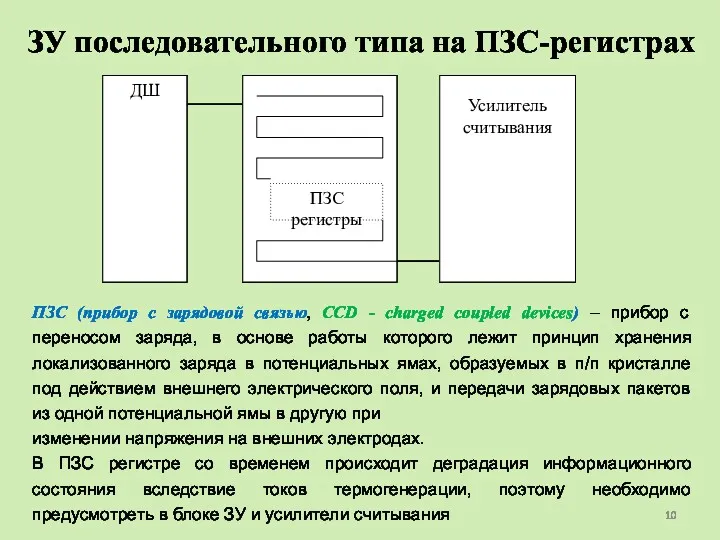

- 10. ЗУ последовательного типа на ПЗС-регистрах ПЗС (прибор с зарядовой связью, CCD - charged coupled devices) –

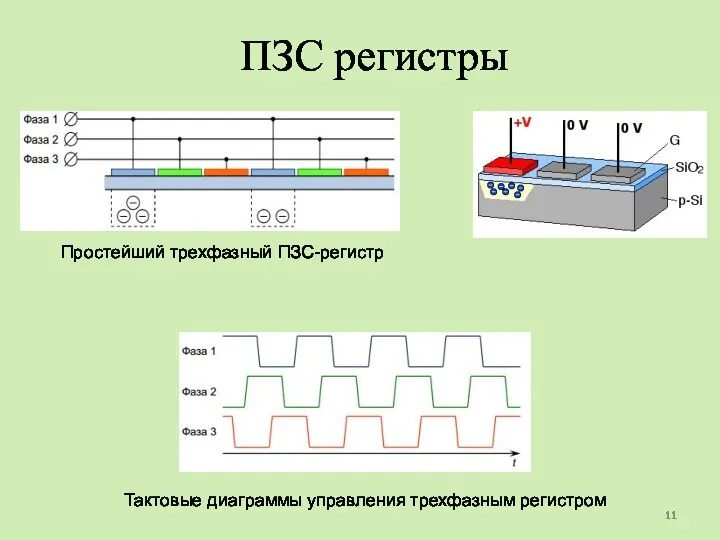

- 11. Простейший трехфазный ПЗС-регистр Тактовые диаграммы управления трехфазным регистром ПЗС регистры

- 12. ЗУ с произвольной выборкой RAM – Random Access Memory

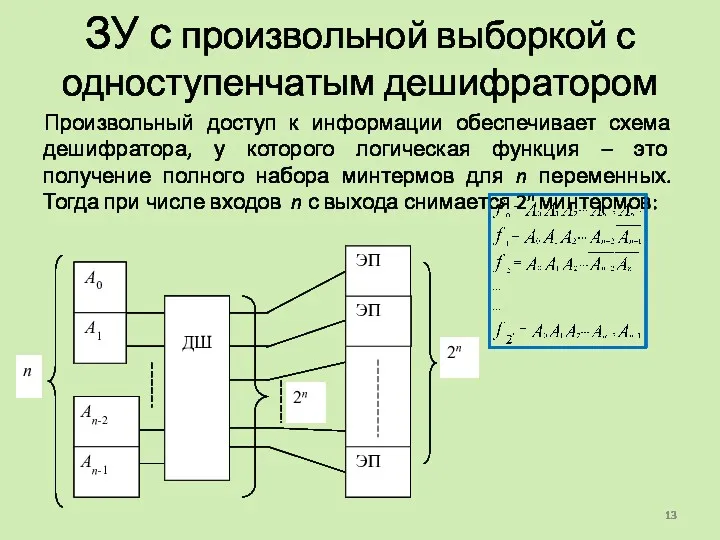

- 13. ЗУ с произвольной выборкой с одноступенчатым дешифратором Произвольный доступ к информации обеспечивает схема дешифратора, у которого

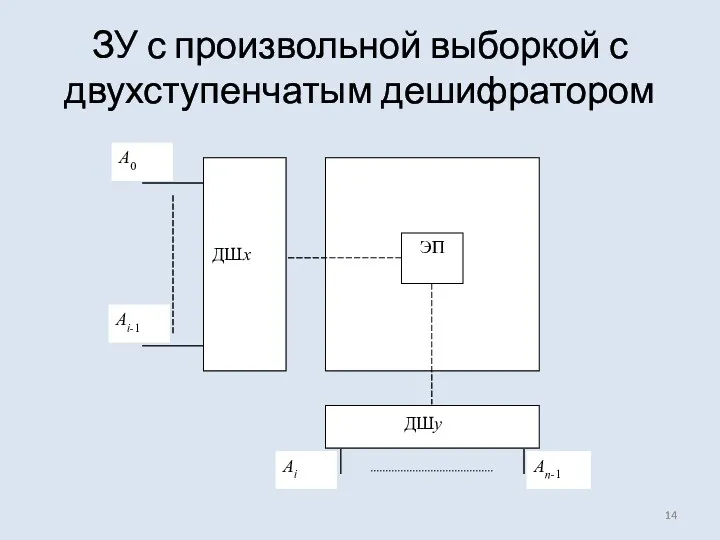

- 14. ЗУ с произвольной выборкой с двухступенчатым дешифратором

- 15. ЗУ с произвольной выборкой АЗУ (ассоциативное ЗУ, Content-addressable memory, associative memory) – схемы с выборкой-сравнением информации

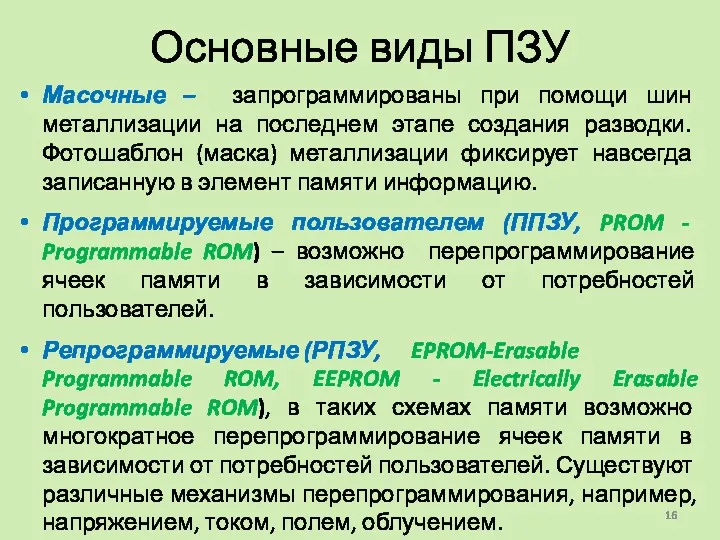

- 16. Основные виды ПЗУ Масочные – запрограммированы при помощи шин металлизации на последнем этапе создания разводки. Фотошаблон

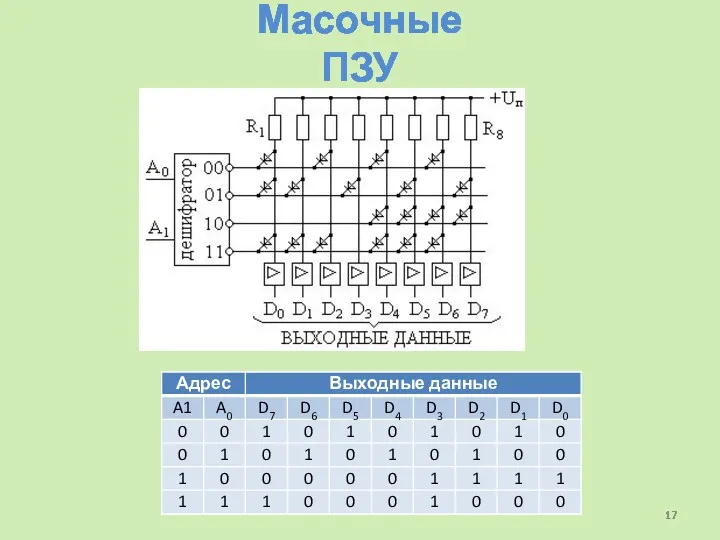

- 17. Масочные ПЗУ

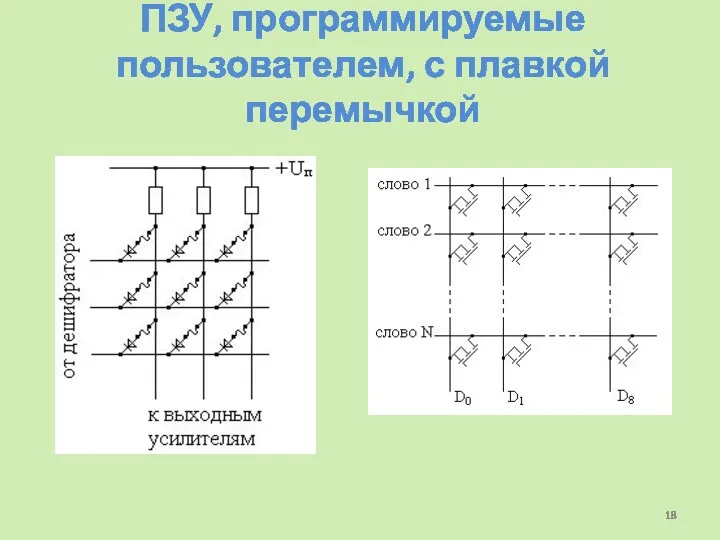

- 18. ПЗУ, программируемые пользователем, с плавкой перемычкой

- 19. Репрограммируемые ПЗУ (РПЗУ) Структура МНОП – металл-нитрид-окисел-полупроводник Структура МОПТ с плавающим затвором Пример режимов стирание запись

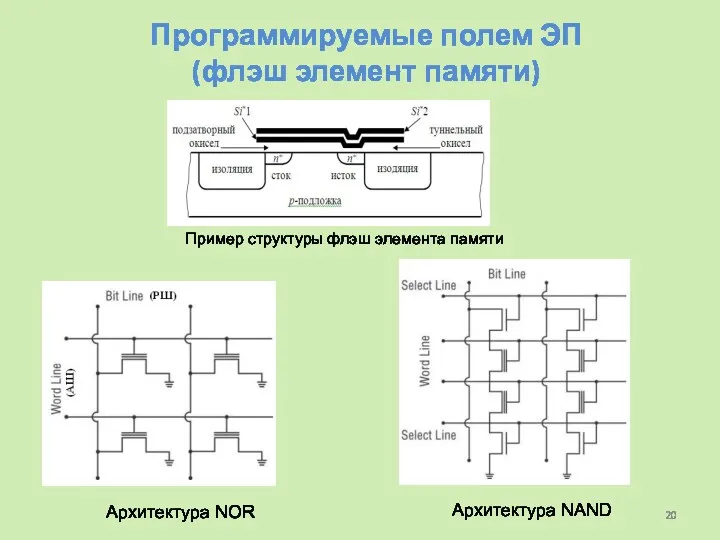

- 20. Программируемые полем ЭП (флэш элемент памяти) Пример структуры флэш элемента памяти Архитектура NOR Архитектура NAND

- 21. Оперативные ЗУ (ОЗУ) ОЗУ статического типа (SRAM - Static Random Access Memory). Элементом памяти служит триггер.

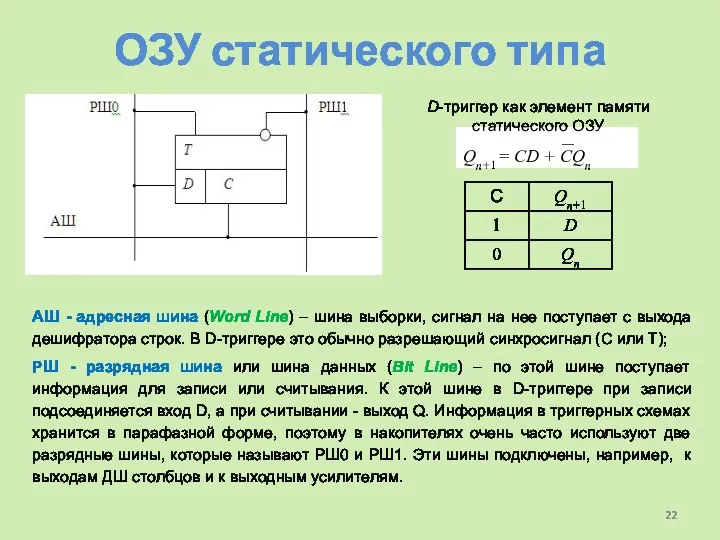

- 22. __ Qn+1 = CD + CQn ОЗУ статического типа D-триггер как элемент памяти статического ОЗУ АШ

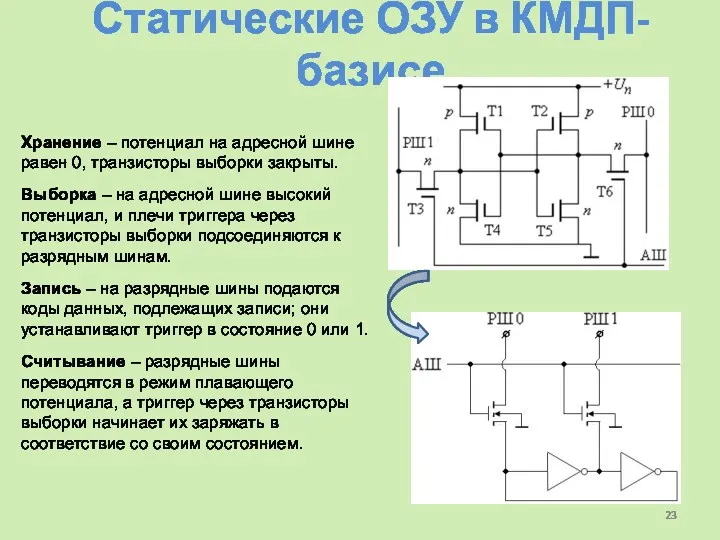

- 23. Статические ОЗУ в КМДП-базисе Хранение – потенциал на адресной шине равен 0, транзисторы выборки закрыты. Выборка

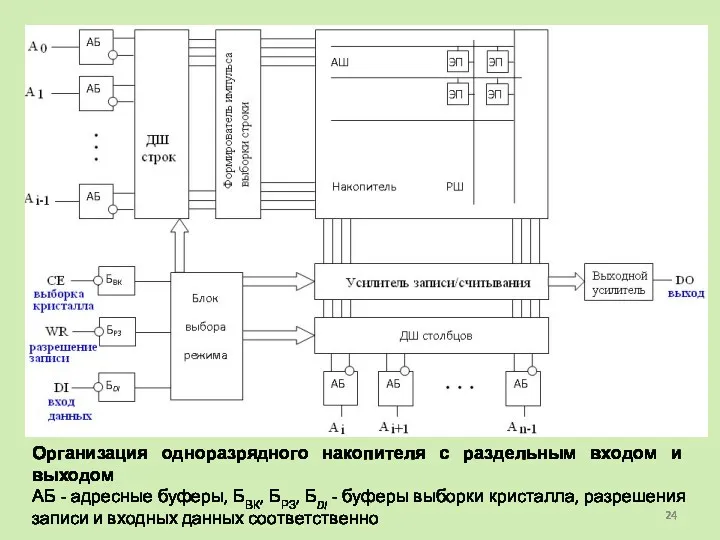

- 24. Организация одноразрядного накопителя с раздельным входом и выходом АБ - адресные буферы, БВК, БРЗ, БDI -

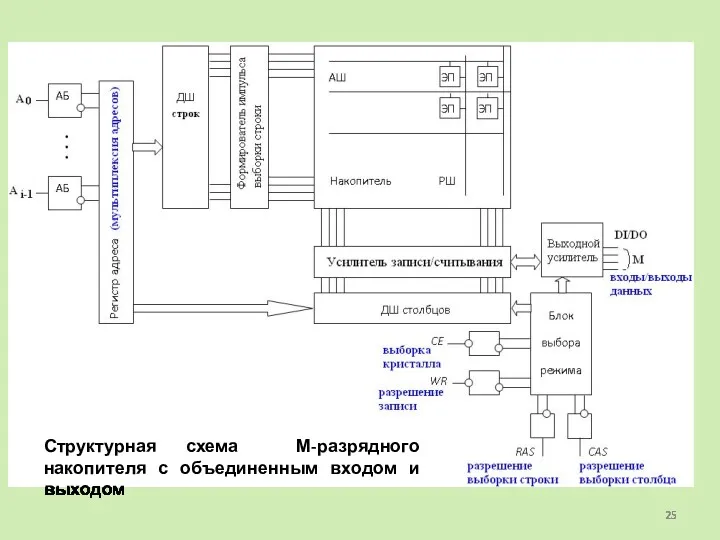

- 25. Структурная схема М-разрядного накопителя с объединенным входом и выходом

- 26. Достоинства и недостатки СОЗУ Достоинства – небольшое энергопотребление, высокое быстродействие. Отсутствие необходимости производить «регенерацию». Недостатки –

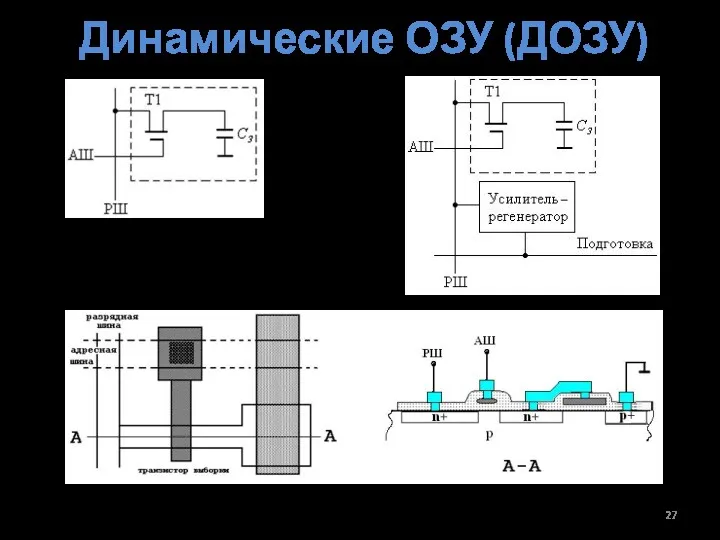

- 27. Динамические ОЗУ (ДОЗУ) Простейшая запоминающая ячейка ДОЗУ Вариант топологии и сечения ячейки ДОЗУ

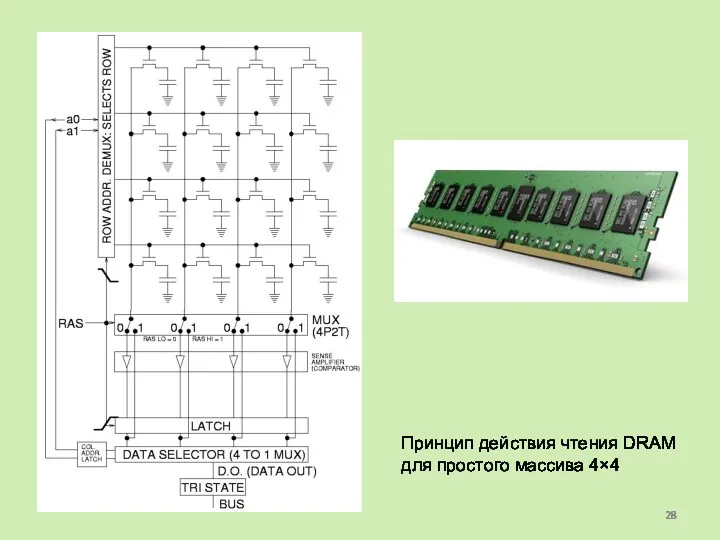

- 28. Принцип действия чтения DRAM для простого массива 4×4

- 30. Скачать презентацию

Христианская семья

Христианская семья Инновации в мире технологий

Инновации в мире технологий Повышение эффективности технического обеспечения молочно-товарного Комплекса в СПК Гожа Гродненского района

Повышение эффективности технического обеспечения молочно-товарного Комплекса в СПК Гожа Гродненского района Аксиомы стереометрии и их следствия

Аксиомы стереометрии и их следствия Великдень. Куличи на Пасху

Великдень. Куличи на Пасху Карамель. Формування споживних властивостей карамелі. Класифікація і формування асортименту карамелі

Карамель. Формування споживних властивостей карамелі. Класифікація і формування асортименту карамелі Система менеджмента безопасности движения

Система менеджмента безопасности движения Основы VBA. Арифметические операторы VBA

Основы VBA. Арифметические операторы VBA Лидеры и элиты в политической жизни

Лидеры и элиты в политической жизни Мейоз. Механизм мейоза

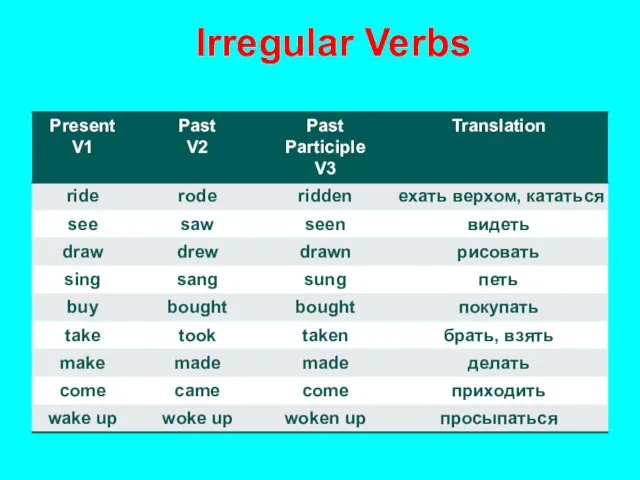

Мейоз. Механизм мейоза Irregular Verbs

Irregular Verbs Правила обращения за региональной социальной доплатой к пенсии, порядок ее установления, выплаты и пересмотра ее размера

Правила обращения за региональной социальной доплатой к пенсии, порядок ее установления, выплаты и пересмотра ее размера Дробные выражения. Устный счет

Дробные выражения. Устный счет Эпидемиология и профилактика сибирской язвы

Эпидемиология и профилактика сибирской язвы Биологическое и социальное в структуре личности

Биологическое и социальное в структуре личности Ударение

Ударение Презентация по творчеству С.Есенина

Презентация по творчеству С.Есенина Презентация для детей Новокуйбышевск - мой родной город

Презентация для детей Новокуйбышевск - мой родной город Неделя профилактики употребления алкоголя. Классный час в 5-Н классе – Альтернатива вредным привычкам

Неделя профилактики употребления алкоголя. Классный час в 5-Н классе – Альтернатива вредным привычкам Охранно - пожарная сигнализация. Виды сигнализаций

Охранно - пожарная сигнализация. Виды сигнализаций Технология изготовления металлического мангала

Технология изготовления металлического мангала Ми ісіктері мен инфекциялары кезіндегі психикалық бұзылыстар

Ми ісіктері мен инфекциялары кезіндегі психикалық бұзылыстар День матери

День матери Государственная идеология как социально-политический феномен

Государственная идеология как социально-политический феномен Компьютер – помощник и друг

Компьютер – помощник и друг активированный уголь

активированный уголь Прорастание семян

Прорастание семян Приёмные антенны и их параметры. Лекция № 7. АФУ

Приёмные антенны и их параметры. Лекция № 7. АФУ