Средства проектирования цифровых устройств с использованием программируемых логических интегральных схем презентация

Содержание

- 2. V.I Архитектура интегральных схем с программируемой структурой (ПЛИС) Список дополнительной литературы: Грушвицкий Р. И., Мурсаев А.

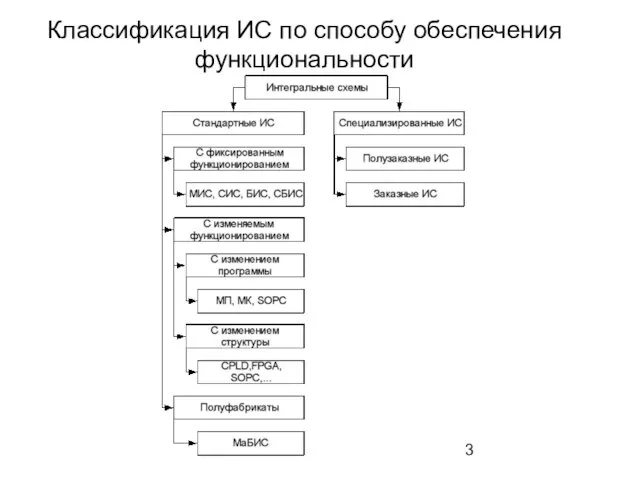

- 3. Классификация ИС по способу обеспечения функциональности

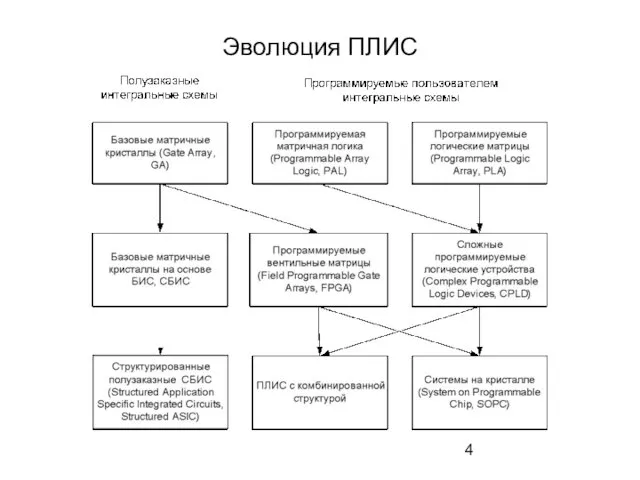

- 4. Эволюция ПЛИС

- 5. Преимуществами современных ПЛИС являются: Простота и малое время проектирования. Низкая стоимость разработки Сокращение используемого пространства печатных

- 6. Сравнение проектов на ASIC, FPGA,PSoC

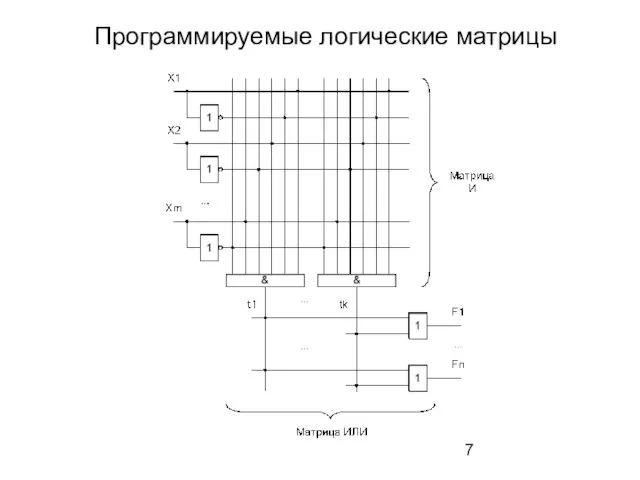

- 7. Программируемые логические матрицы

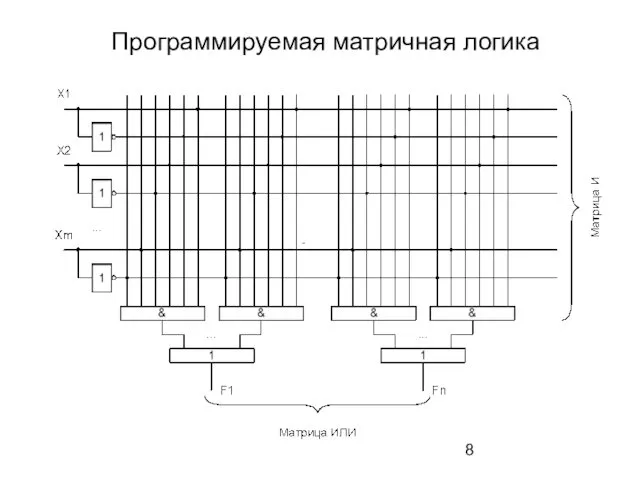

- 8. Программируемая матричная логика

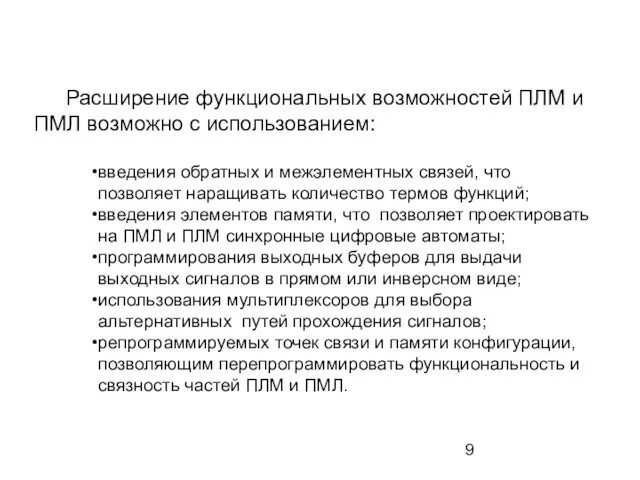

- 9. Расширение функциональных возможностей ПЛМ и ПМЛ возможно с использованием: введения обратных и межэлементных связей, что позволяет

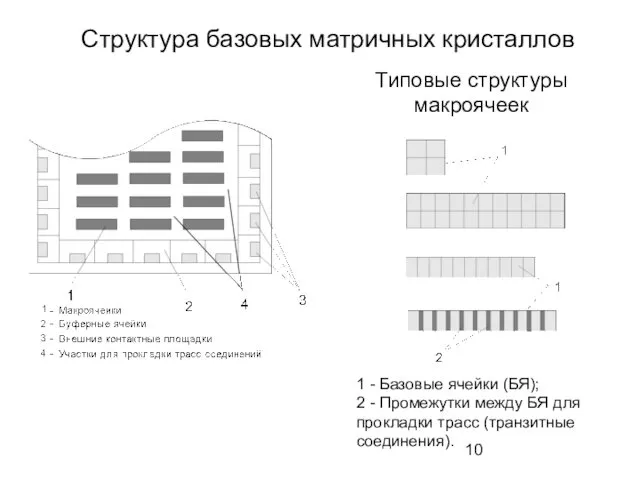

- 10. Структура базовых матричных кристаллов Типовые структуры макроячеек 1 - Базовые ячейки (БЯ); 2 - Промежутки между

- 11. Классификация ПЛИС по типу программируемых связей

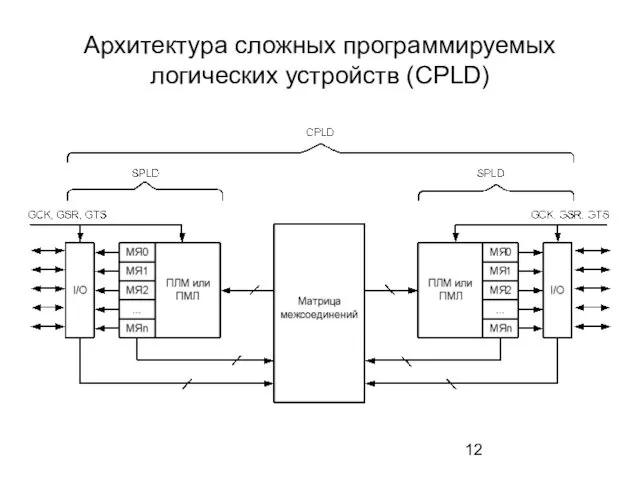

- 12. Архитектура сложных программируемых логических устройств (CPLD)

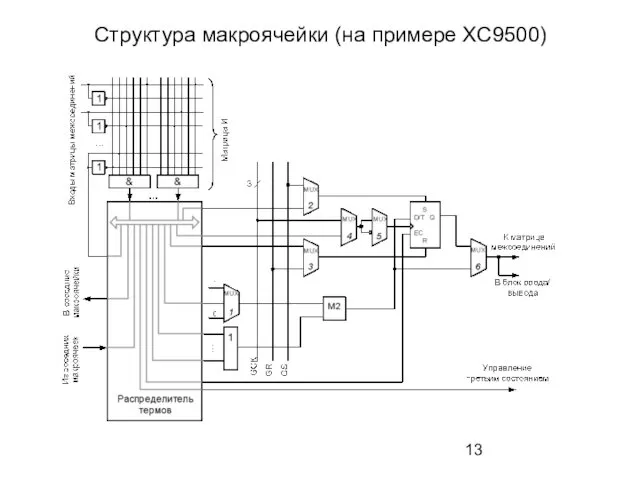

- 13. Структура макроячейки (на примере XC9500)

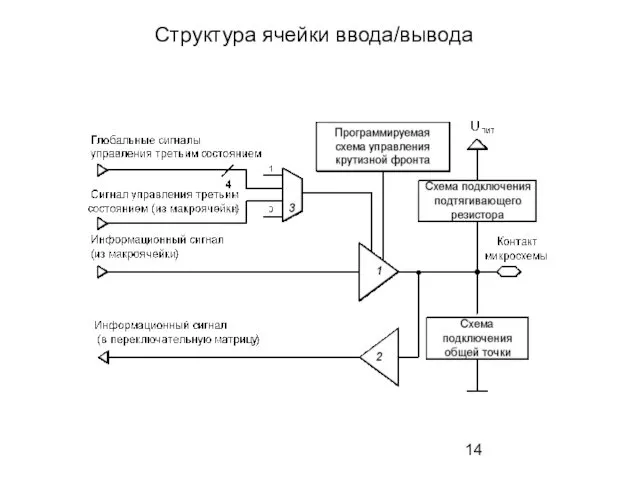

- 14. Структура ячейки ввода/вывода

- 15. Архитектура ПЛИС семейства кристаллов XC9500

- 16. Функциональный блок CPLD (на примере XC9500)

- 17. Макроячейка (на примере XC9500)

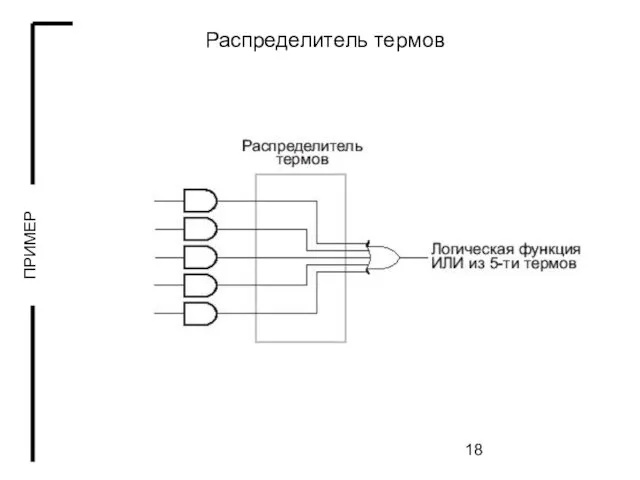

- 18. Распределитель термов

- 19. Увеличение функциональности распределитель термов CPLD

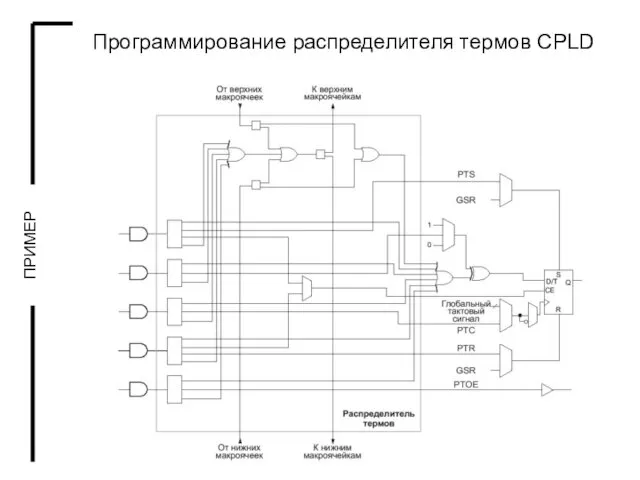

- 20. Программирование распределителя термов CPLD

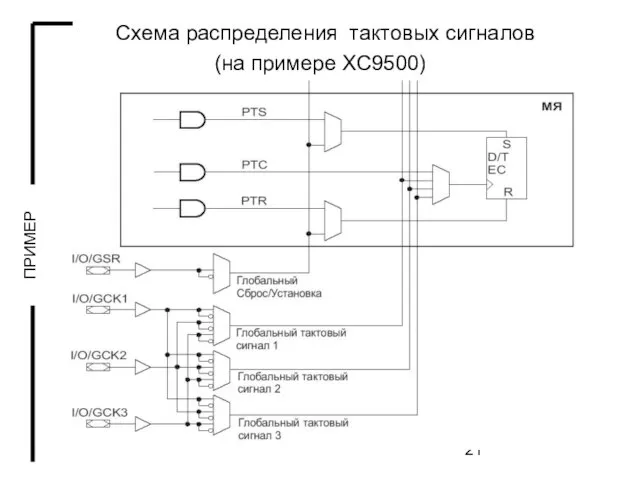

- 21. Схема распределения тактовых сигналов (на примере XC9500)

- 22. Программируемые вентильные матрицы (FPGA)

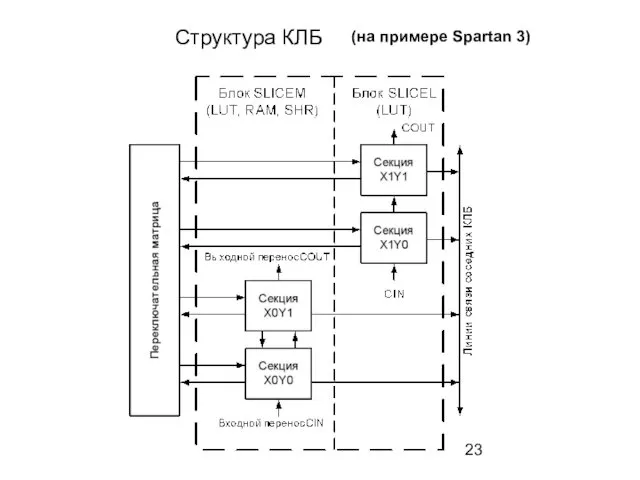

- 23. Структура КЛБ (на примере Spartan 3)

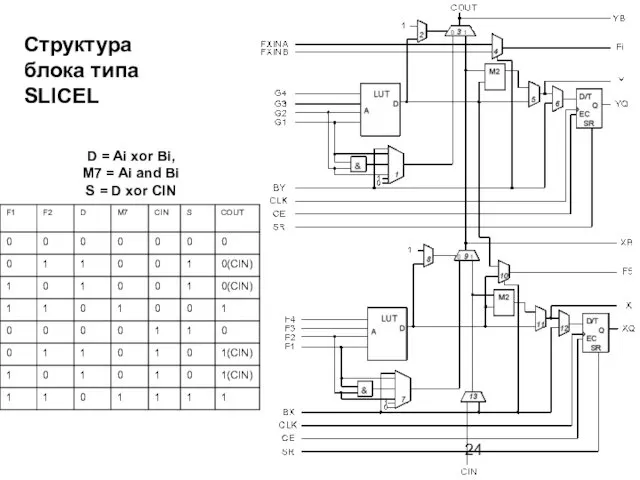

- 24. Структура блока типа SLICEL D = Ai xor Bi, M7 = Ai and Bi S =

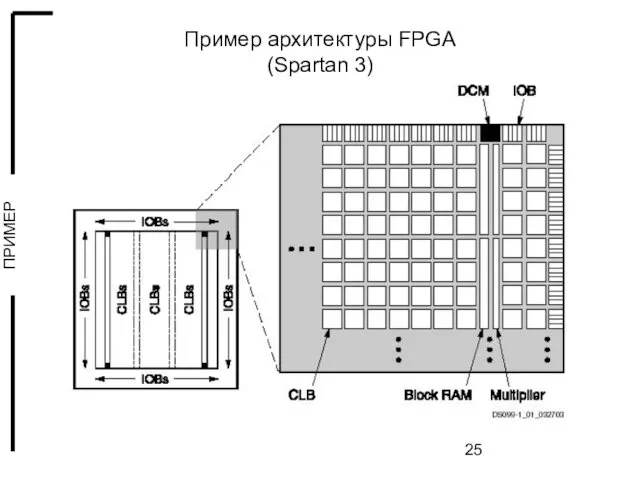

- 25. Пример архитектуры FPGA (Spartan 3)

- 26. Конфигурируемые логические блоки с памятью (Spartan 3)

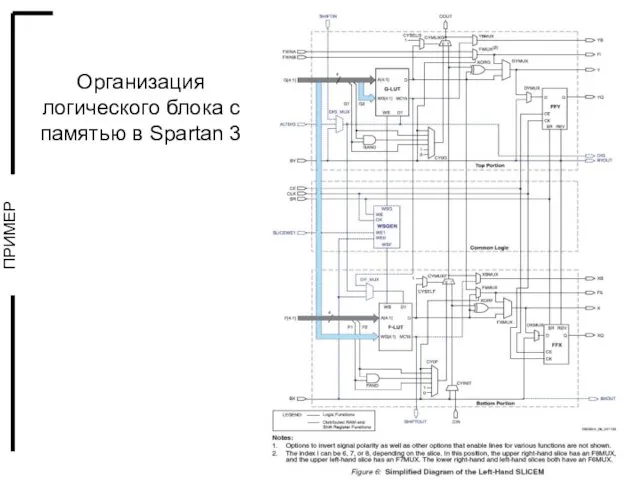

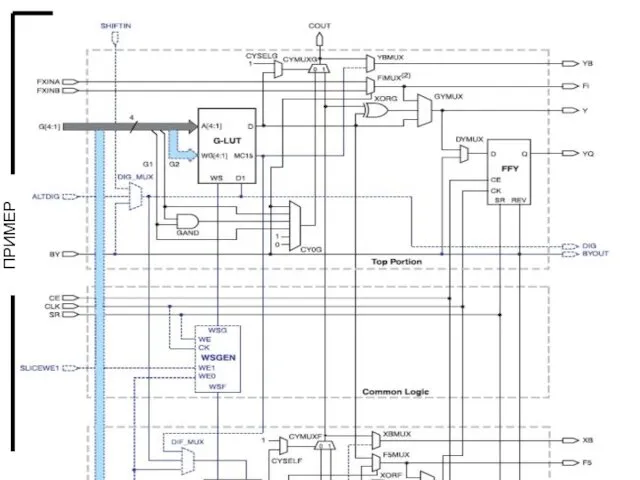

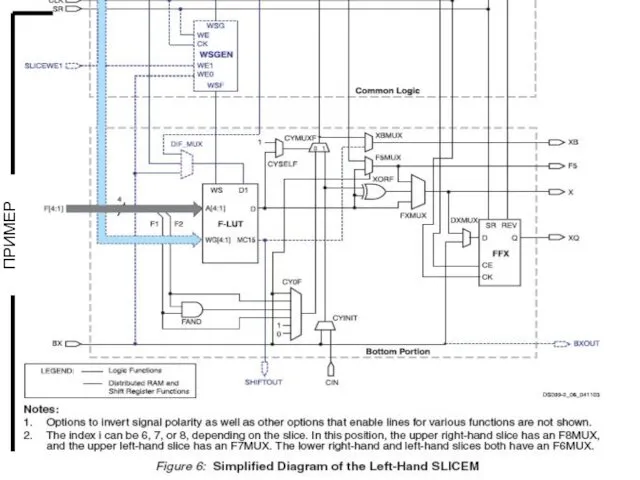

- 27. Организация логического блока с памятью в Spartan 3

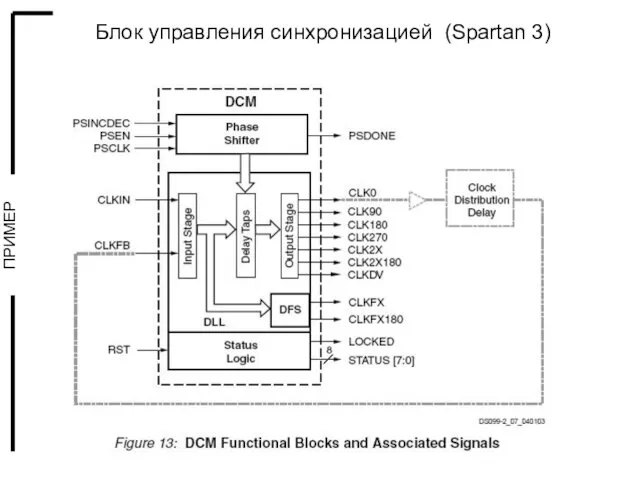

- 30. Блок управления синхронизацией (Spartan 3)

- 31. Устройство коррекции расфазирования синхросигналов (Delay Locked Loops)

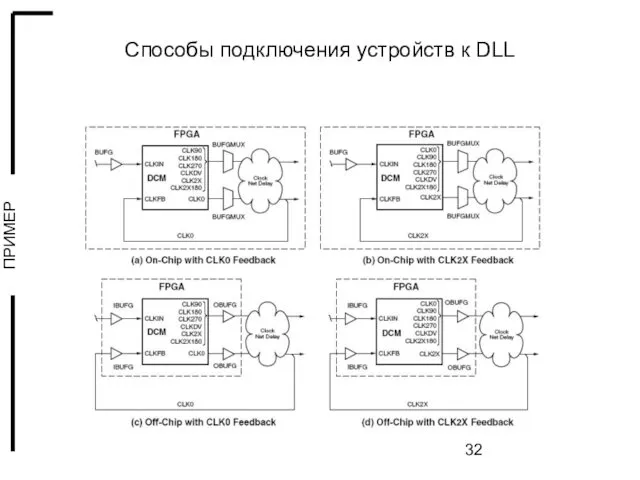

- 32. Способы подключения устройств к DLL

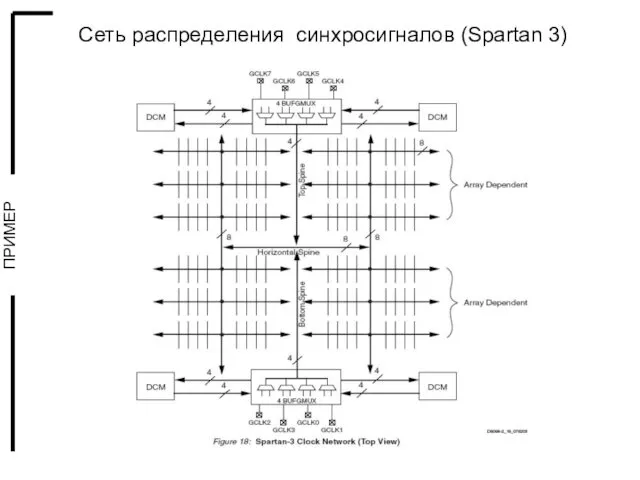

- 33. Сеть распределения синхросигналов (Spartan 3)

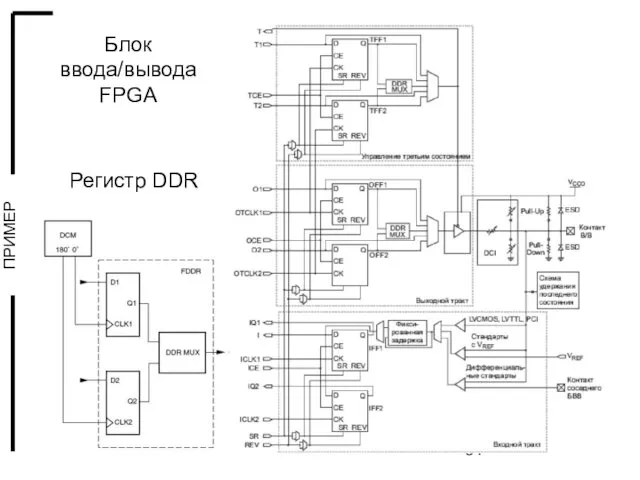

- 34. Блок ввода/вывода FPGA Регистр DDR

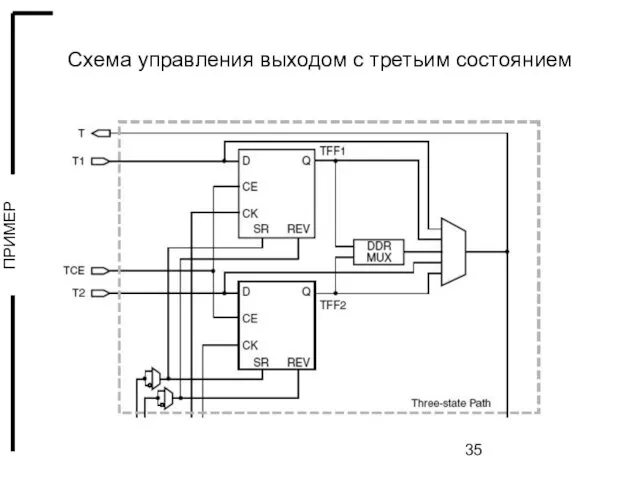

- 35. Схема управления выходом с третьим состоянием

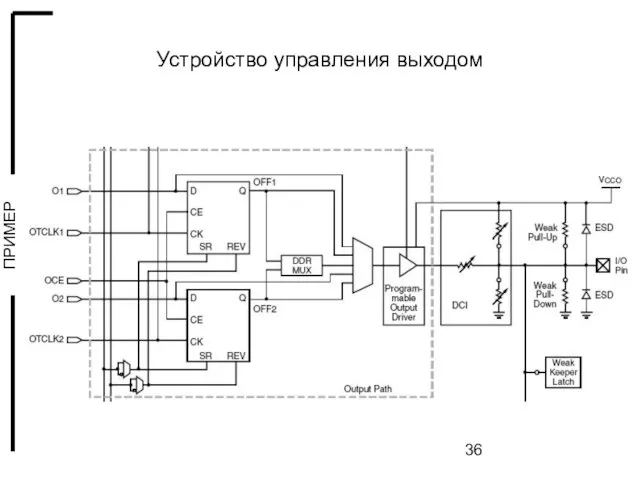

- 36. Устройство управления выходом

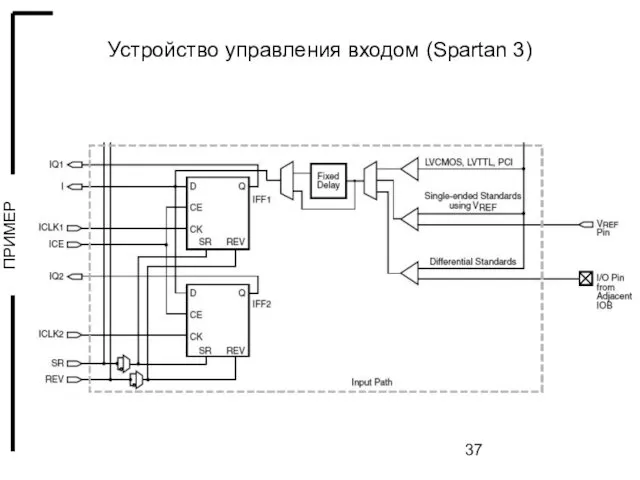

- 37. Устройство управления входом (Spartan 3)

- 38. Матрица коммутации КЛБ (Spartan 3)

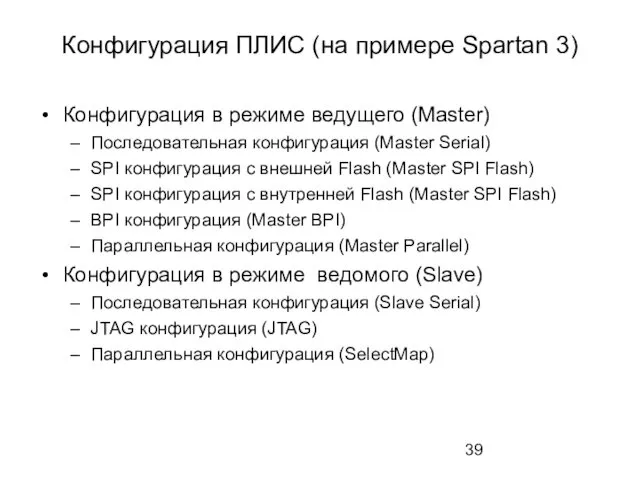

- 39. Конфигурация ПЛИС (на примере Spartan 3) Конфигурация в режиме ведущего (Master) Последовательная конфигурация (Master Serial) SPI

- 40. Последовательная конфигурация (Master Serial) Схема конфигурирования по JTAG интерфейсу (3.3 V)

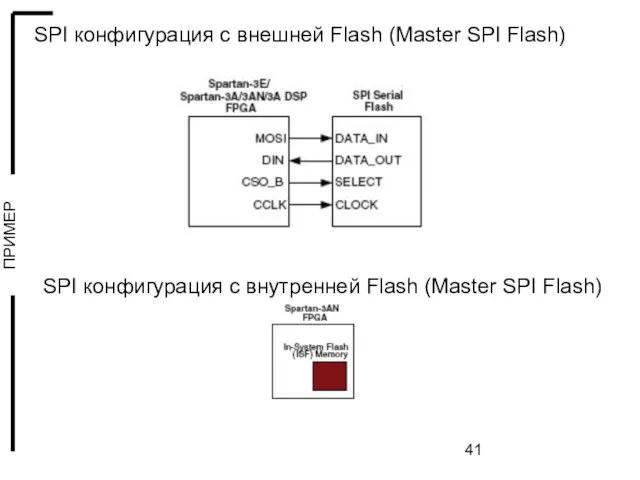

- 41. SPI конфигурация с внутренней Flash (Master SPI Flash) SPI конфигурация с внешней Flash (Master SPI Flash)

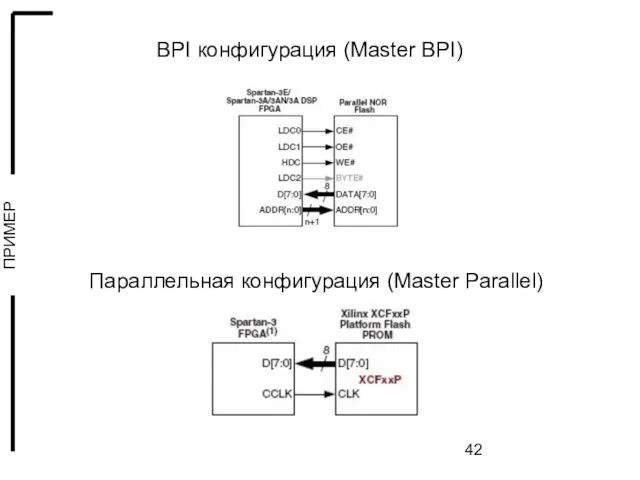

- 42. BPI конфигурация (Master BPI) Параллельная конфигурация (Master Parallel)

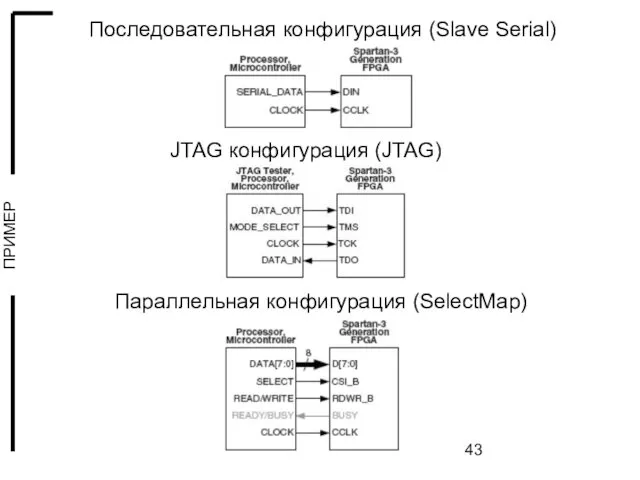

- 43. Последовательная конфигурация (Slave Serial) JTAG конфигурация (JTAG) Параллельная конфигурация (SelectMap)

- 44. Архитектура ПЛИС типа SOPC Варианты реализации библиотечных блоков: Soft - ядра. Firm - ядра. Hard –

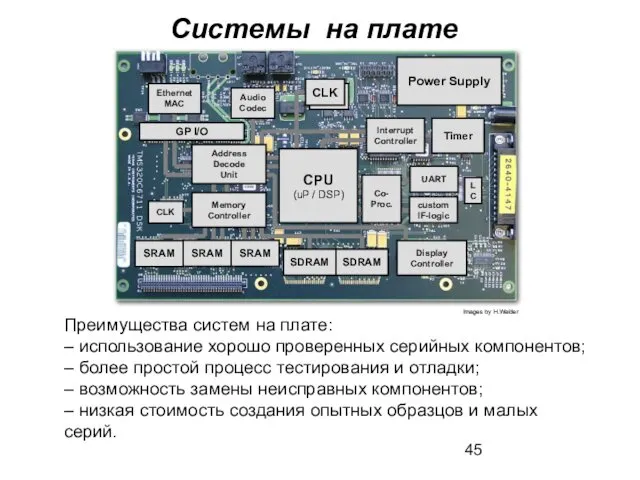

- 45. Преимущества систем на плате: – использование хорошо проверенных серийных компонентов; – более простой процесс тестирования и

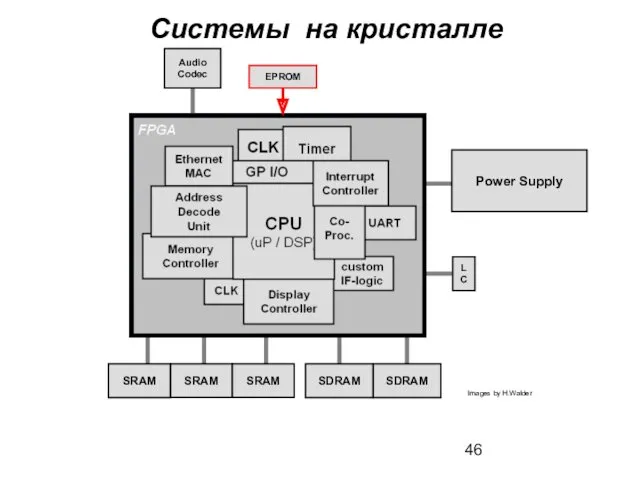

- 46. Системы на кристалле

- 47. –возможность получения более высоких технических показателей (производительность, энергопотребление, массогабаритные характеристики); – более низкая стоимость при крупносерийном

- 49. Скачать презентацию

Олимпиада - 2014 в Сочи

Олимпиада - 2014 в Сочи Дорожные знаки

Дорожные знаки Правила уборки номера в отеле (раздел 3)

Правила уборки номера в отеле (раздел 3) Государственное и муниципальное управление. Южный федеральный округ г. Анапа

Государственное и муниципальное управление. Южный федеральный округ г. Анапа Komodo National Park

Komodo National Park Жердің ғаламшар ретіндегі жалпы сипаттамасы

Жердің ғаламшар ретіндегі жалпы сипаттамасы Увлекательная математика

Увлекательная математика Ф.А.Искандер - советский и российский прозаик и абхазский поэт

Ф.А.Искандер - советский и российский прозаик и абхазский поэт Системы электроснабжения. Организация эксплуатации инженерных систем зданий и сооружений

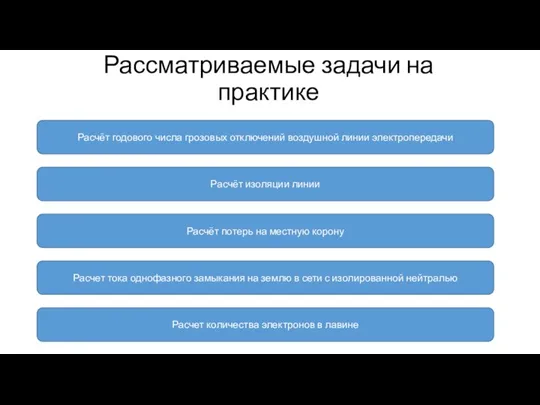

Системы электроснабжения. Организация эксплуатации инженерных систем зданий и сооружений Рассматриваемые задачи на практике

Рассматриваемые задачи на практике Моделирование в электротехнике

Моделирование в электротехнике Эквалайзер. Тест

Эквалайзер. Тест 9_Презентация_к_уроку_Галогены_и_их_соединения

9_Презентация_к_уроку_Галогены_и_их_соединения Урок рефлексии

Урок рефлексии Основы научно-исследовательской работы в школе. Выпускная квалификационная работа

Основы научно-исследовательской работы в школе. Выпускная квалификационная работа Параллелограмм, прямоугольник, ромб, квадрат

Параллелограмм, прямоугольник, ромб, квадрат Компьютерные сети

Компьютерные сети Урок географии 6 класс Рельеф дна Мирового океана

Урок географии 6 класс Рельеф дна Мирового океана Безопасность детей в интернете. Информационная памятка

Безопасность детей в интернете. Информационная памятка Я – за здоровый образ жизни

Я – за здоровый образ жизни Снпс-ақтөбемұнайгаз акционерлік қоғам

Снпс-ақтөбемұнайгаз акционерлік қоғам Приемы развития творческого мышления

Приемы развития творческого мышления Правотворчество

Правотворчество Скелет туловища, скелет конечностей

Скелет туловища, скелет конечностей Родительское собрание. Развиваем внимание

Родительское собрание. Развиваем внимание Театральное искусство в блокадном Ленинграде

Театральное искусство в блокадном Ленинграде Определение ориентации квартиры по сторонам света с помощью компаса

Определение ориентации квартиры по сторонам света с помощью компаса Топливно -энергетический комплекс Челябинской области

Топливно -энергетический комплекс Челябинской области