Содержание

- 2. Список использованных и рекомендуемых источников Технология, конструкции и методы моделирования кремниевых интегральных микросхем: в 2 ч.

- 5. Industrial Plasma Engineering Applications to Nonthermal Plasma Processing J Reece Roth Department of Electrical and Computer

- 6. Основным параметром технологии является минимальная технологическая (топологическая, проектная) норма (technology node, feature size). Говоря о проектной

- 7. Степень интеграции Ki=lgN, N – количество основных элементов, входящих в состав микросхемы Ki= ≤ 1 –

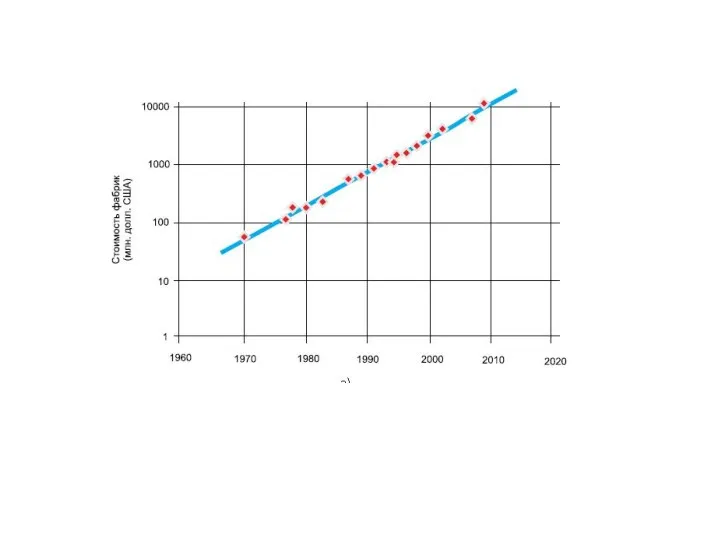

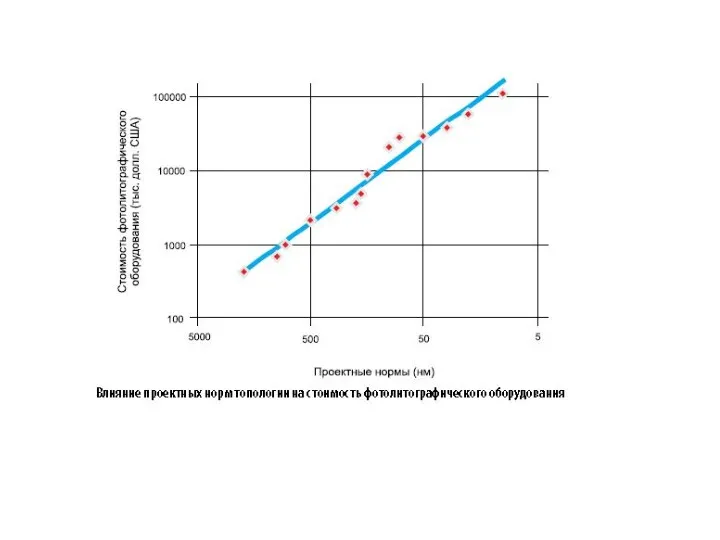

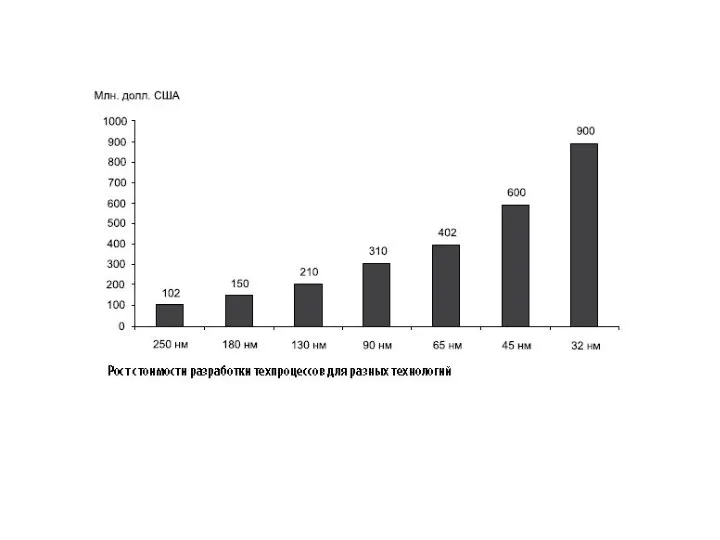

- 8. Увеличение диаметра пластин и снижение проектных топологических норм является неотъемлемой частью истории развития полупроводниковой микроэлектроники. За

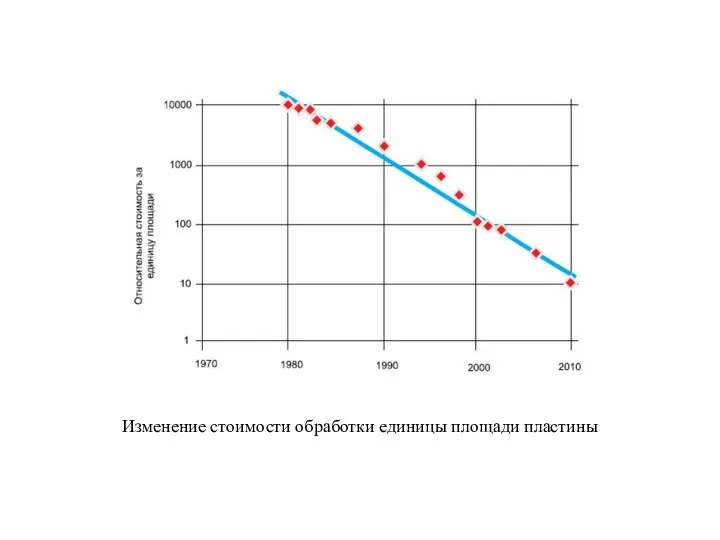

- 9. Изменение стоимости обработки единицы площади пластины

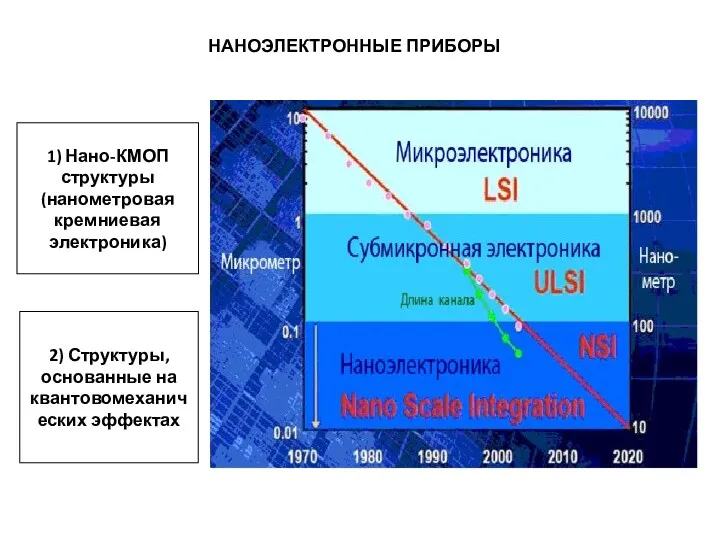

- 15. НАНОЭЛЕКТРОННЫЕ ПРИБОРЫ 2) Структуры, основанные на квантовомеханических эффектах 1) Нано-КМОП структуры (нанометровая кремниевая электроника)

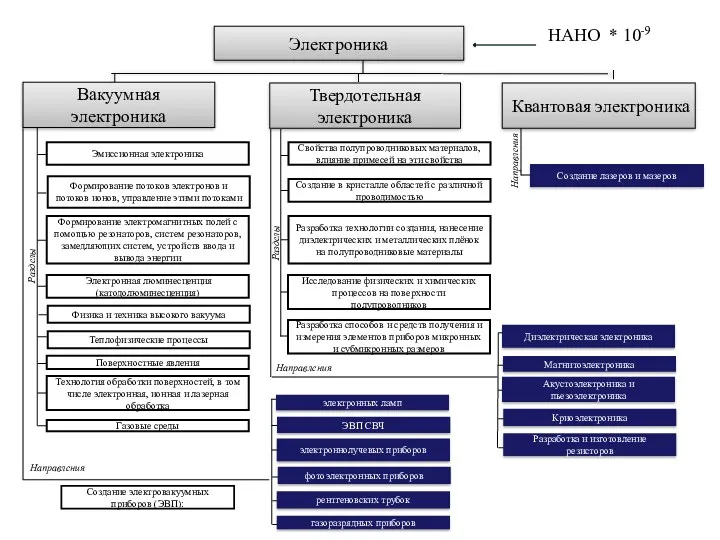

- 16. Электроника Квантовая электроника Создание электровакуумных приборов (ЭВП): Акустоэлектроника и пьезоэлектроника Разработка и изготовление резисторов Криоэлектроника Магнитоэлектроника

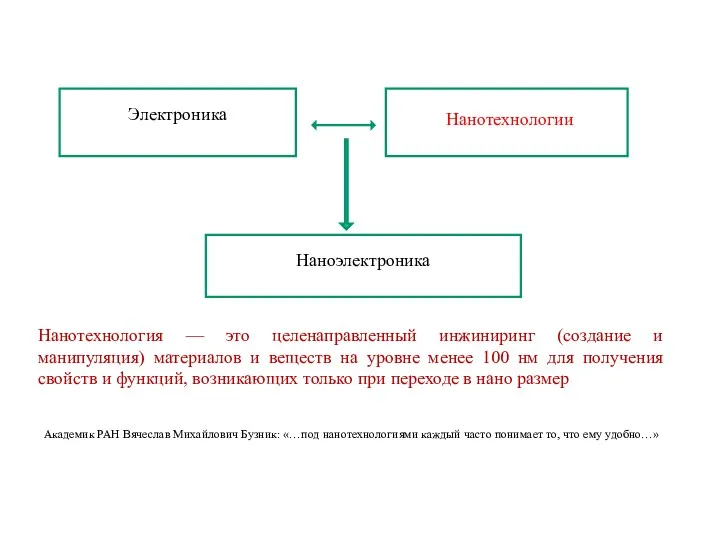

- 17. Академик РАН Вячеслав Михайлович Бузник: «…под нанотехнологиями каждый часто понимает то, что ему удобно…» Нанотехнология —

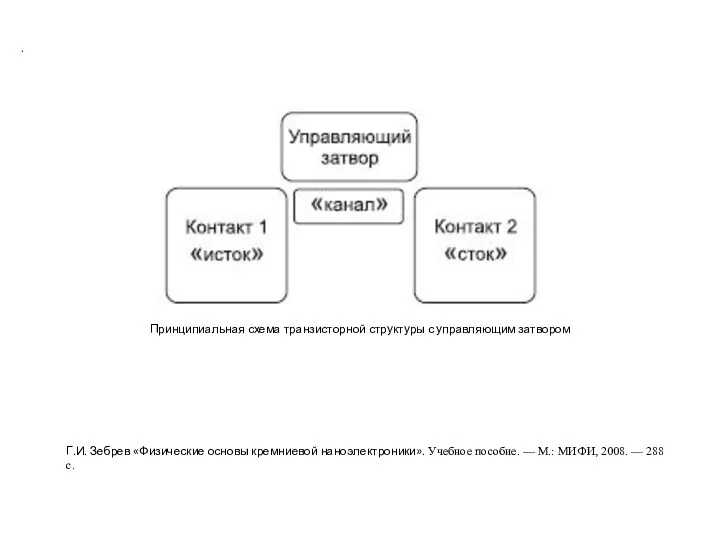

- 18. . Принципиальная схема транзисторной структуры с управляющим затвором Г.И. Зебрев «Физические основы кремниевой наноэлектроники». Учебное пособие.

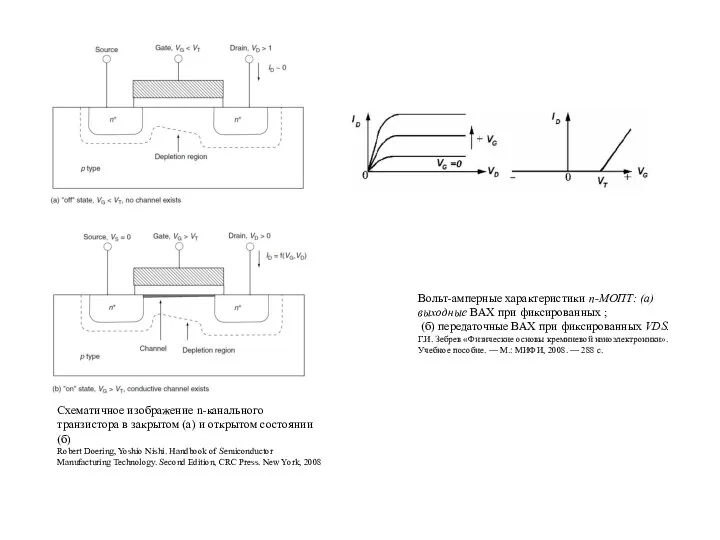

- 19. Схематичное изображение n-канального транзистора в закрытом (а) и открытом состоянии (б) Robert Doering, Yoshio Nishi. Handbook

- 20. Технологические проблемы УБИС в наиболее общем виде можно свести к : Как увеличить токовую нагрузочную способность

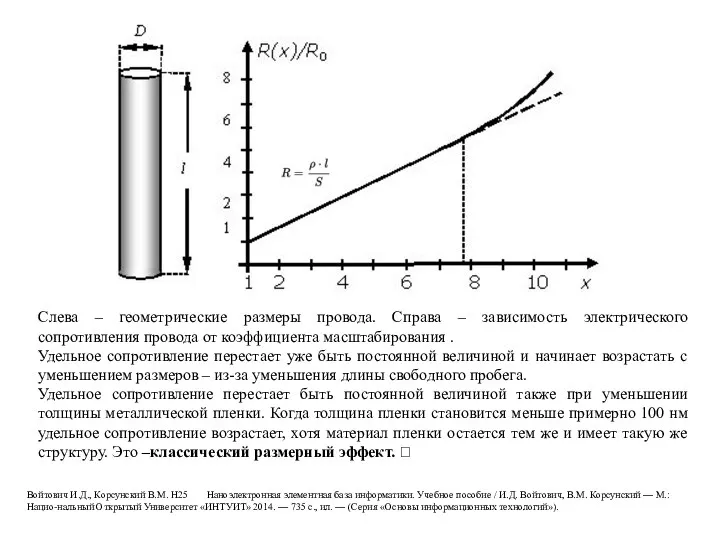

- 21. Слева – геометрические размеры провода. Справа – зависимость электрического сопротивления провода от коэффициента масштабирования . Удельное

- 22. Аналогично и в случае транзисторов. Когда размер активной области транзистора становится меньше длины свободного пробега носителей

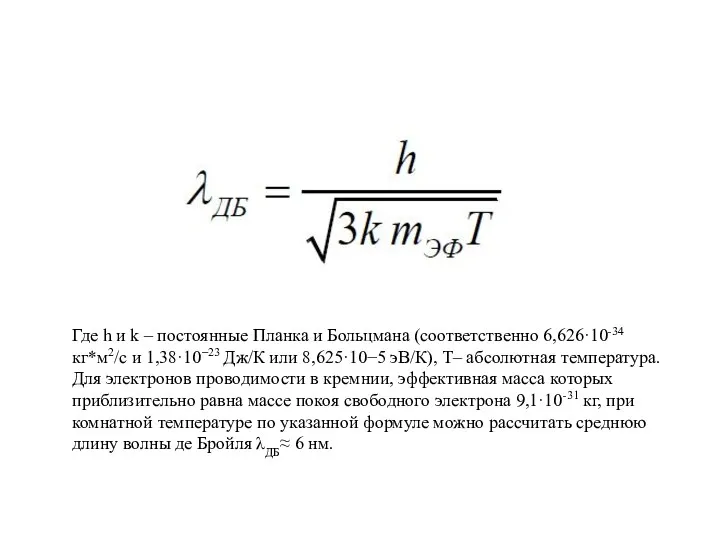

- 23. Где h и k – постоянные Планка и Больцмана (соответственно 6,626·10-34 кг*м2/с и 1,38·10−23 Дж/К или

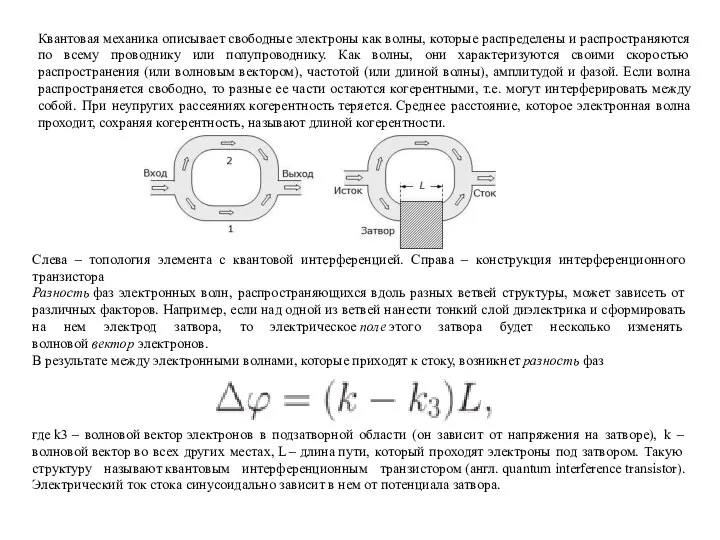

- 24. Слева – топология элемента с квантовой интерференцией. Справа – конструкция интерференционного транзистора Разность фаз электронных волн,

- 25. Красников Г.Я. Конструктивно-технологические особенности субмикронных МОП-транзисторов Издание 2-е, исправленное Москва: Техносфера, 2011. - 800 с., ISBN

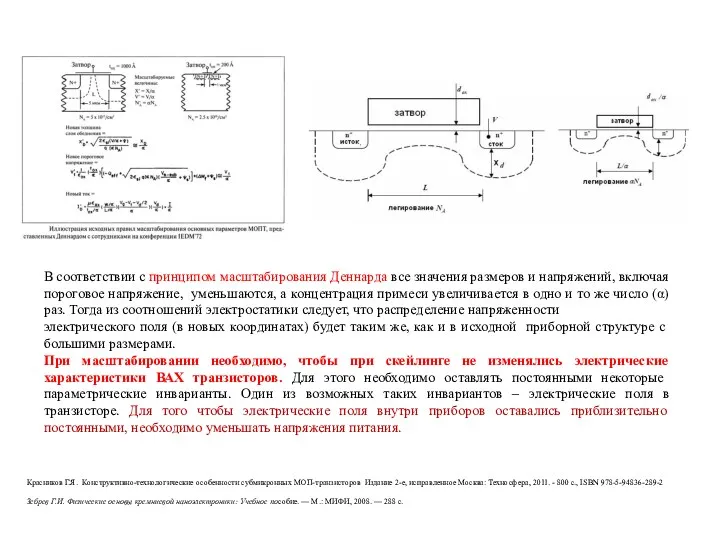

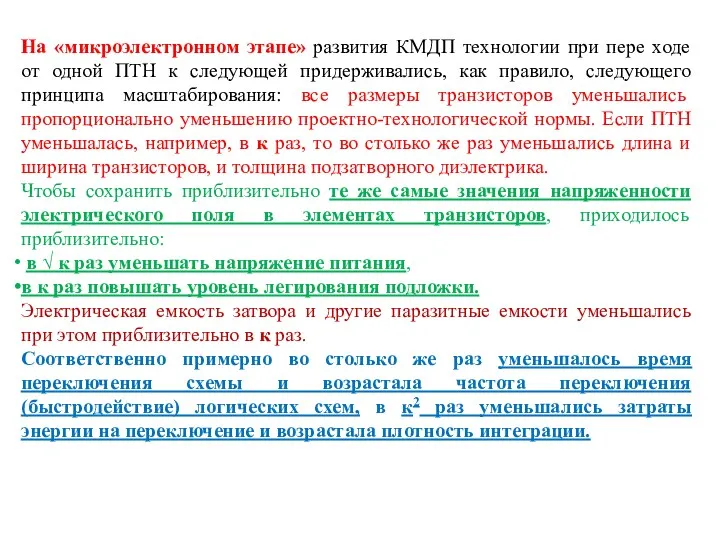

- 26. На «микроэлектронном этапе» развития КМДП технологии при пере ходе от одной ПТН к следующей придерживались, как

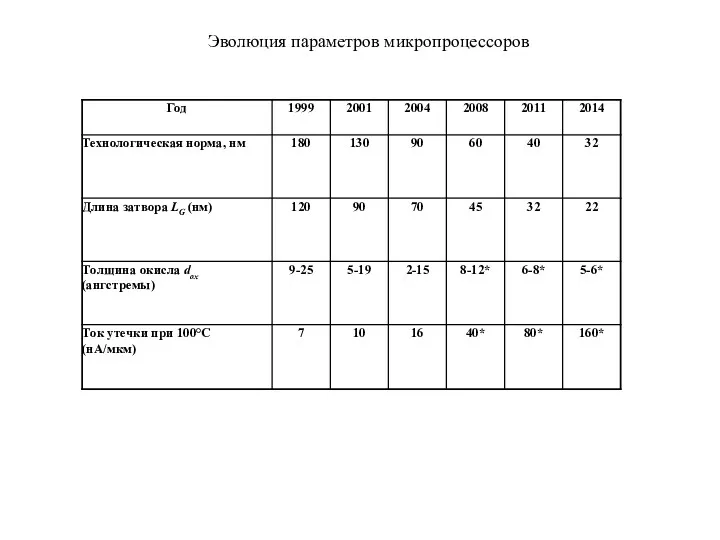

- 27. Эволюция параметров микропроцессоров

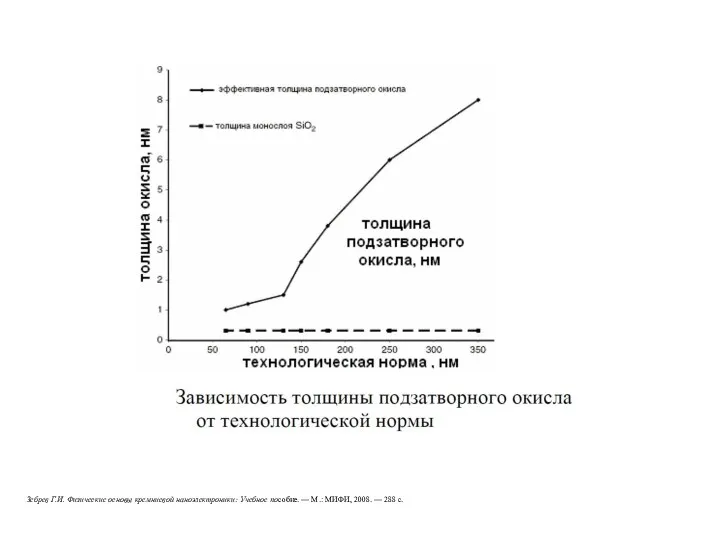

- 28. Зебрев Г.И. Физические основы кремниевой наноэлектроники: Учебное пособие. — М.: МИФИ, 2008. — 288 с.

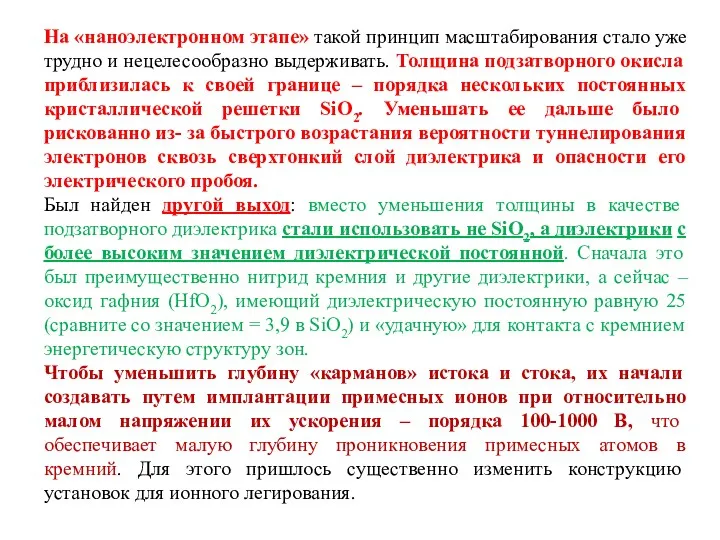

- 29. На «наноэлектронном этапе» такой принцип масштабирования стало уже трудно и нецелесообразно выдерживать. Толщина подзатворного окисла приблизилась

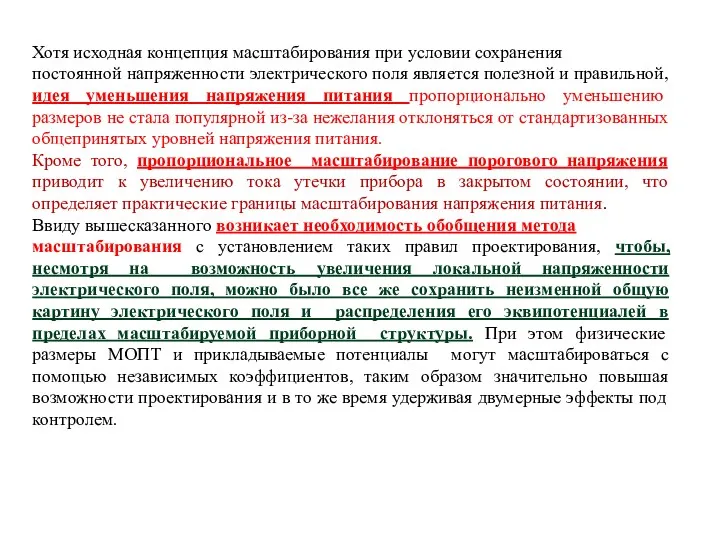

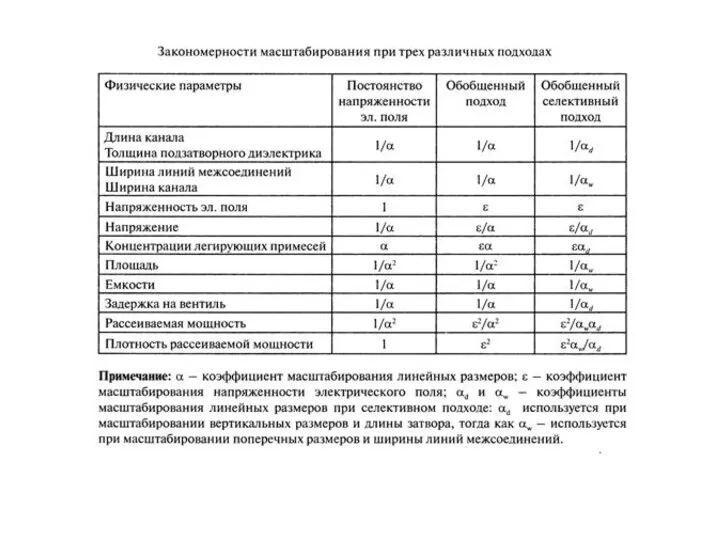

- 30. Хотя исходная концепция масштабирования при условии сохранения постоянной напряженности электрического поля является полезной и правильной, идея

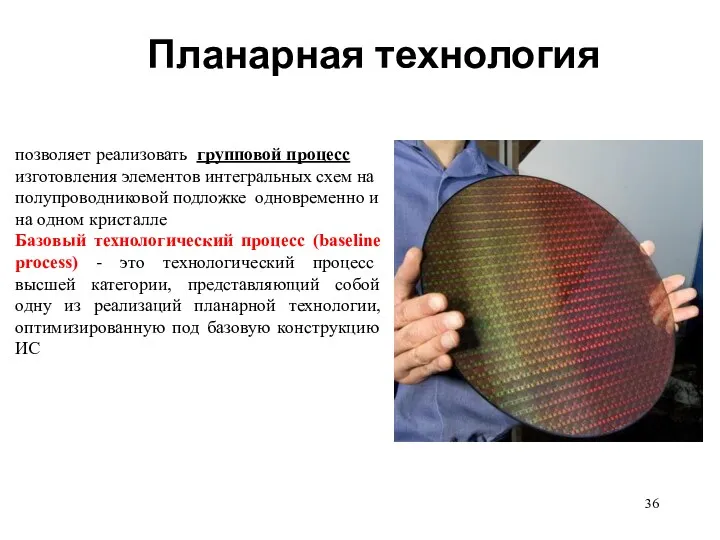

- 36. Планарная технология позволяет реализовать групповой процесс изготовления элементов интегральных схем на полупроводниковой подложке одновременно и на

- 37. Технология, в производственном смысле, - это способы контролируемого преобразования вещества, энергии, информации в процессе изготовления продукции,

- 38. Планарная технология Основным технологическим методом создания современных интегральных микросхем остается разработанная в конце 50-х годов двадцатого

- 39. Планарная технология (от англ. planar, от лат. planus – плоский, ровный), – форма организации технологического процесса

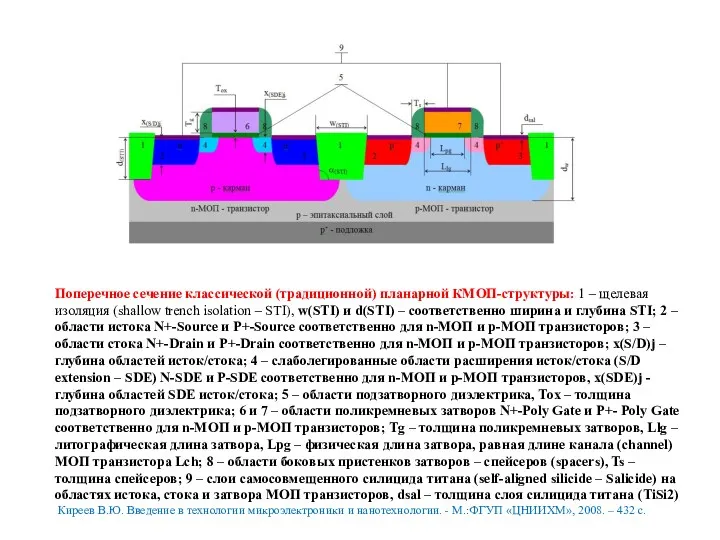

- 40. Поперечное сечение классической (традиционной) планарной КМОП-структуры: 1 – щелевая изоляция (shallow trench isolation – STI), w(STI)

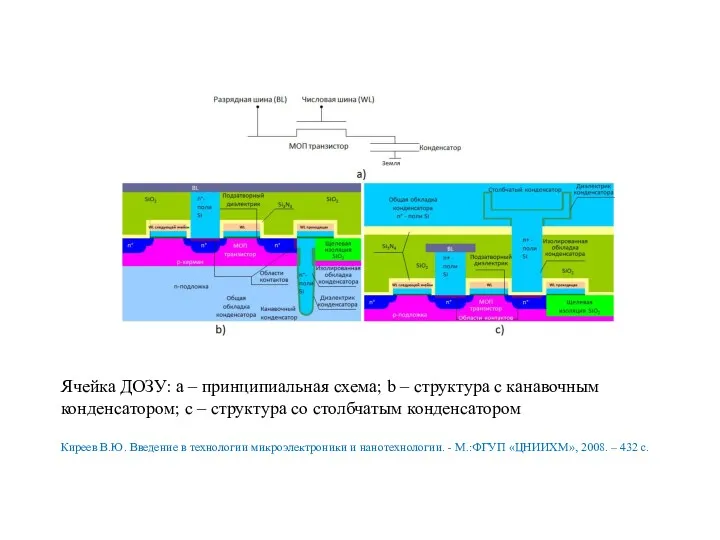

- 41. Ячейка ДОЗУ: a – принципиальная схема; b – структура с канавочным конденсатором; c – структура со

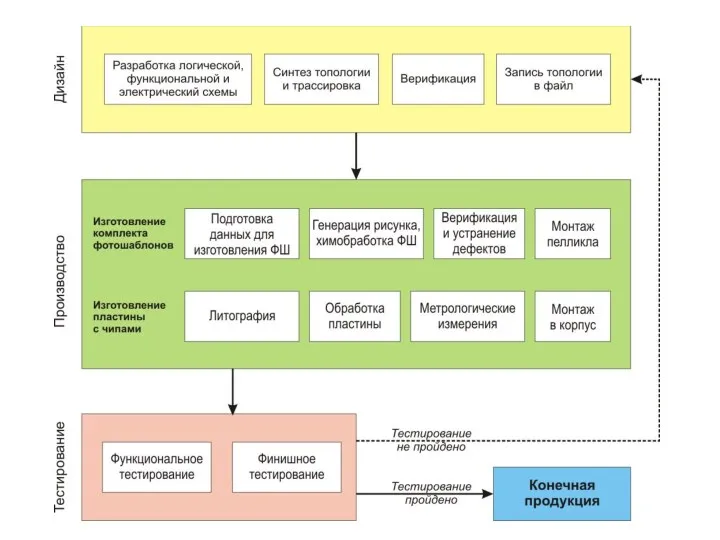

- 42. Стадии технологического маршрута. Технологический процесс (маршрут) изготовления интегральных схем ИС состоит из четырех стадий: Стадия 1.

- 43. Основные операции планарной технологии легирование полупроводника (диффузия примесей в полупроводник и ионная имплантация) окисление кремния травление

- 44. Принципы планарной технологии взаимосвязь конструкции интегральных микросхем и технологии их изготовления совместимость элементов (на одном кристалле)

- 45. Взаимосвязь конструкции интегральных микросхем и технологии их изготовления Проектирование конструкции интегральной микросхемы связано с технологией ее

- 46. Совместимость элементов интегральных микросхем Единый групповой метод изготовления. Основной элемент – самый сложный элемент ИС -

- 47. Локальность технологических обработок Во время технологических операций обрабатывается не вся поверхность пластины. Методы локальных технологий: масочная

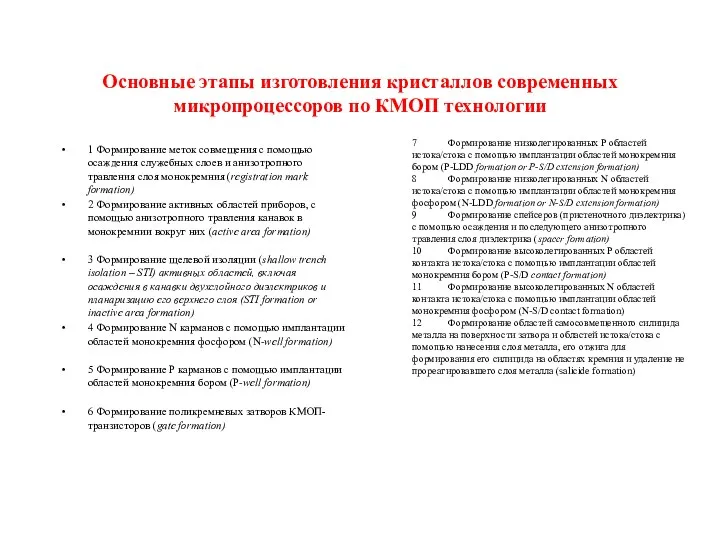

- 49. Основные этапы изготовления кристаллов современных микропроцессоров по КМОП технологии 1 Формирование меток совмещения с помощью осаждения

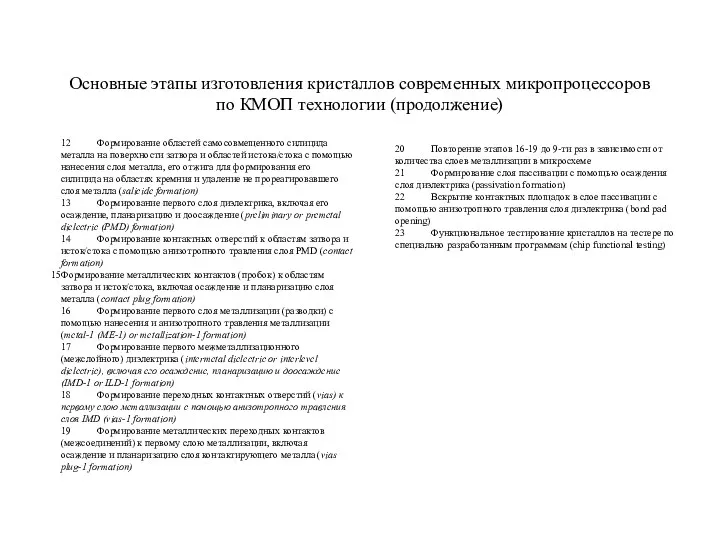

- 50. Основные этапы изготовления кристаллов современных микропроцессоров по КМОП технологии (продолжение) 12 Формирование областей самосовмещенного силицида металла

- 51. Часть технологического маршрута изготовления кристаллов ИС от операции очистки исходной пластины до операции формирования слоя первого

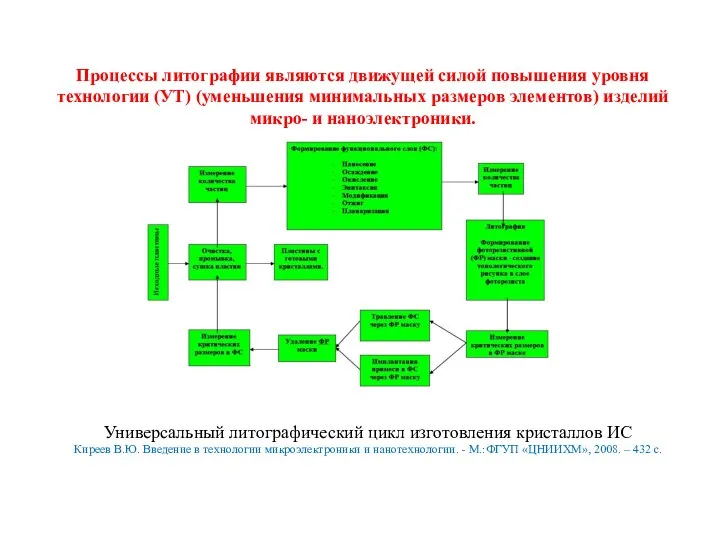

- 52. Универсальный литографический цикл изготовления кристаллов ИС Киреев В.Ю. Введение в технологии микроэлектроники и нанотехнологии. - М.:ФГУП

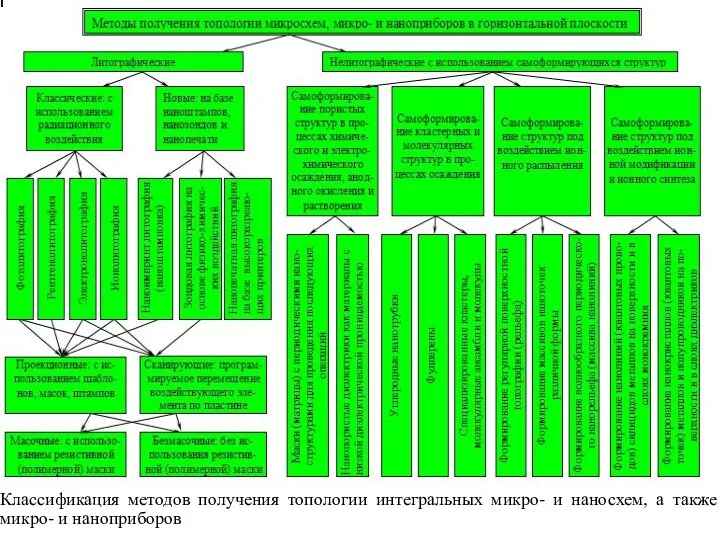

- 53. Классификация методов получения топологии интегральных микро- и наносхем, а также микро- и наноприборов

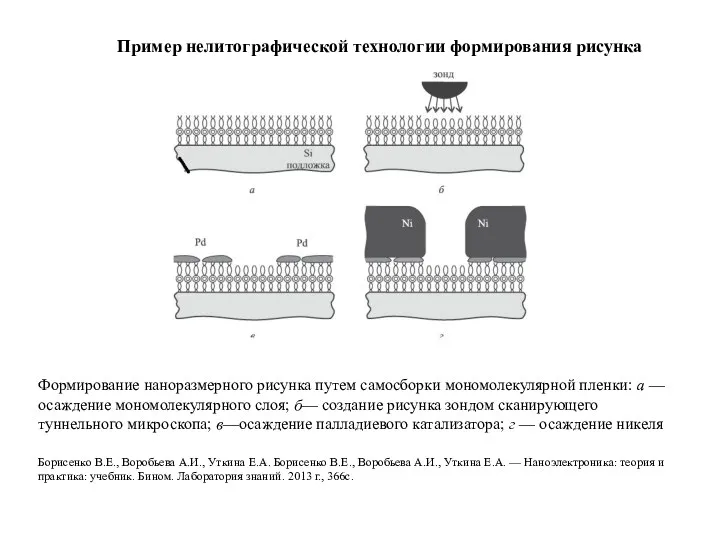

- 54. Формирование наноразмерного рисунка путем самосборки мономолекулярной пленки: а — осаждение мономолекулярного слоя; б— создание рисунка зондом

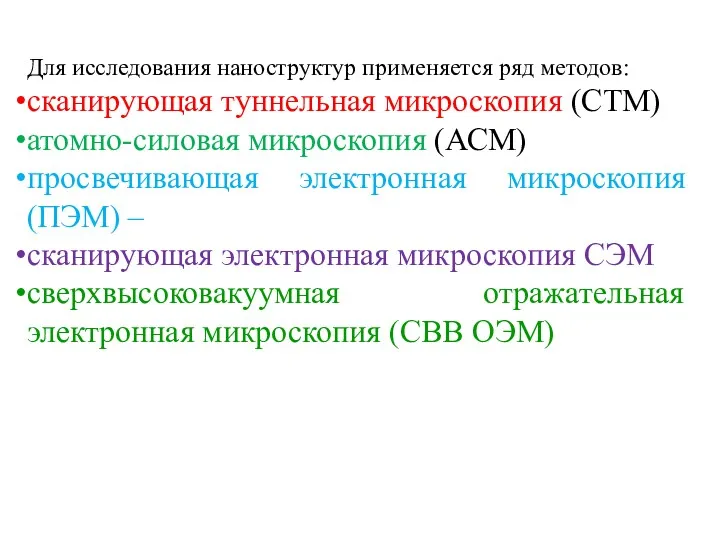

- 55. Методы контроля наноструктур

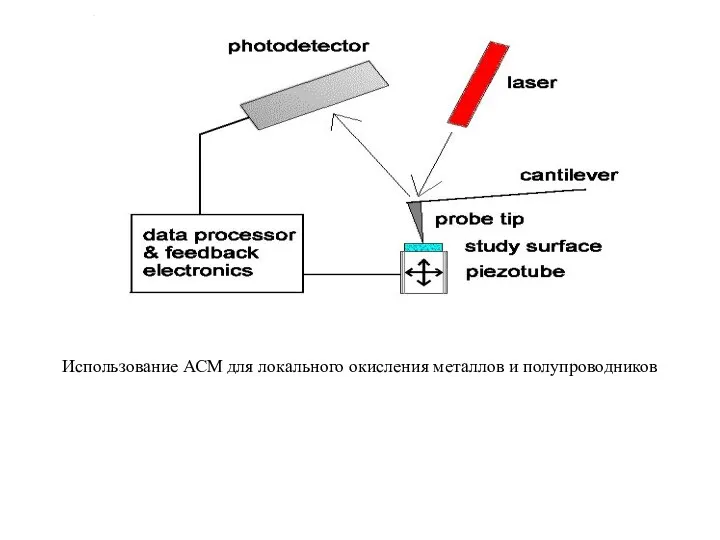

- 56. Для исследования наноструктур применяется ряд методов: сканирующая туннельная микроскопия (СТМ) атомно-силовая микроскопия (АСМ) просвечивающая электронная микроскопия

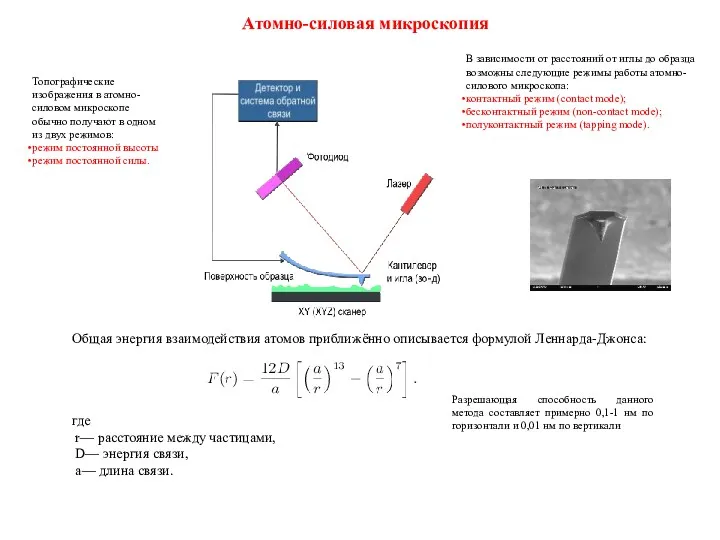

- 57. Сканирование обычно проводят в двух режимах: постоянного тока или постоянного уровня кантилевера (сенсорное устройство, закрепленно на

- 58. Общая энергия взаимодействия атомов приближённо описывается формулой Леннарда-Джонса: где r— расстояние между частицами, D— энергия связи,

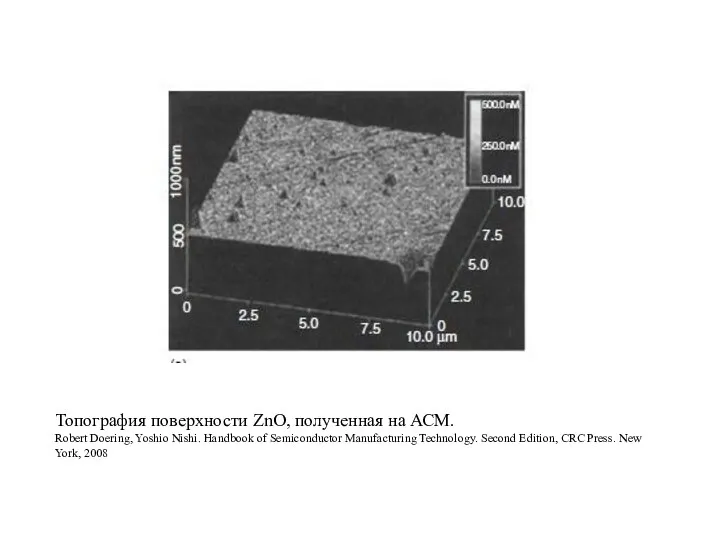

- 59. Топография поверхности ZnO, полученная на АСМ. Robert Doering, Yoshio Nishi. Handbook of Semiconductor Manufacturing Technology. Second

- 60. Просвечивающий электронный микроскоп Метод просвечивающей электронной микроскопии позволяет изучать внутреннюю структуру исследуемых материалов: определять тип и

- 61. При проведении исследований на СЭМ (часто также встречается название «растровый электроный микроскоп» или сокращенно РЭМ) Тонкий

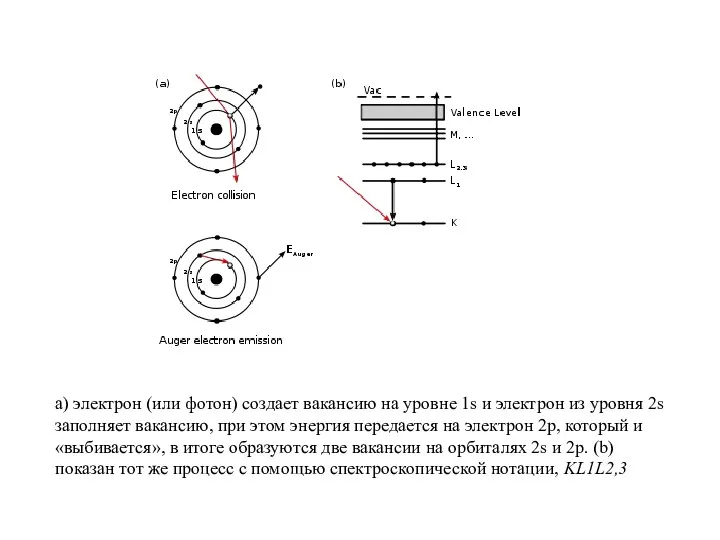

- 62. a) электрон (или фотон) создает вакансию на уровне 1s и электрон из уровня 2s заполняет вакансию,

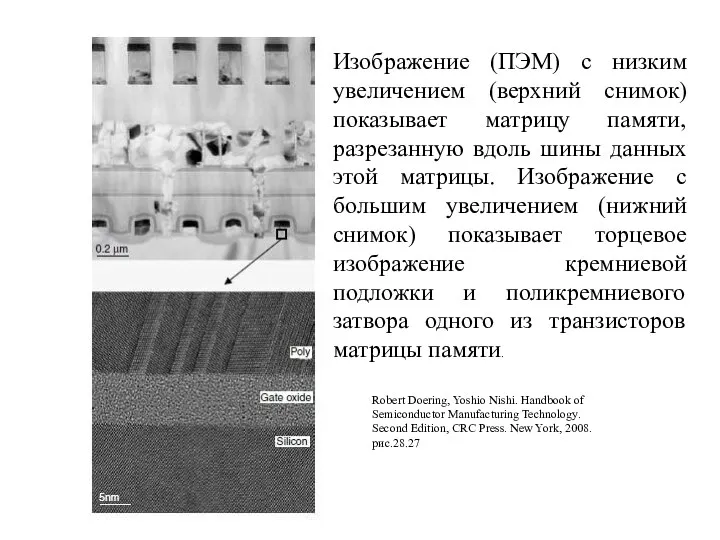

- 63. Robert Doering, Yoshio Nishi. Handbook of Semiconductor Manufacturing Technology. Second Edition, CRC Press. New York, 2008.

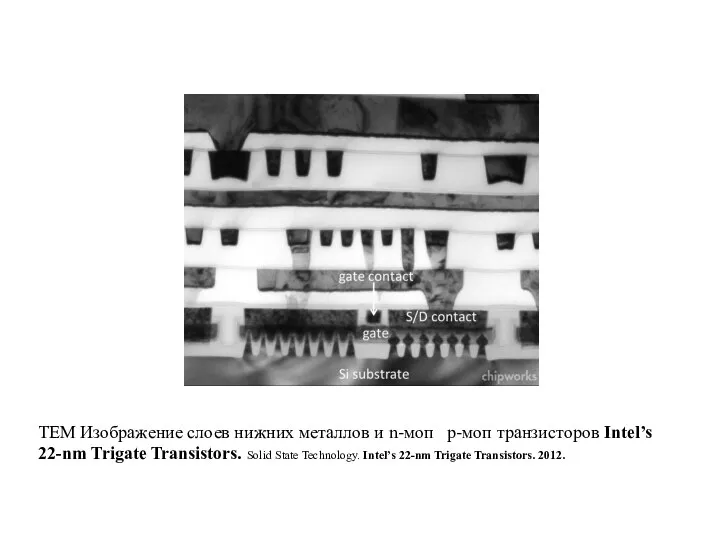

- 64. TEM Изображение слоев нижних металлов и n-моп p-моп транзисторов Intel’s 22-nm Trigate Transistors. Solid State Technology.

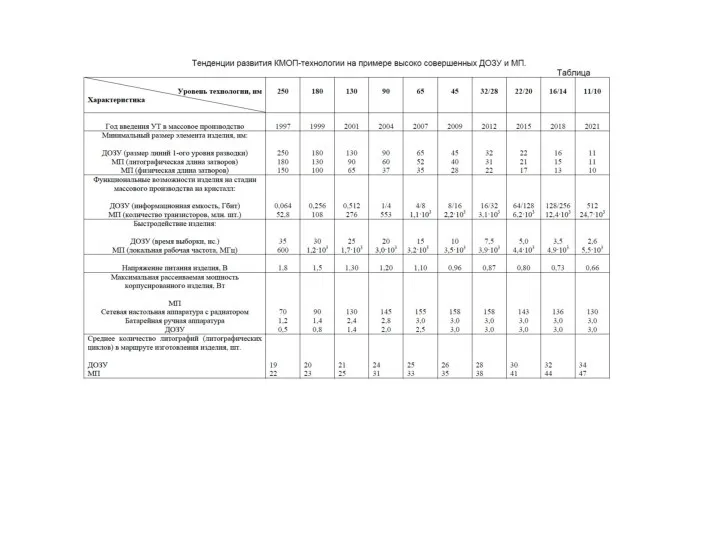

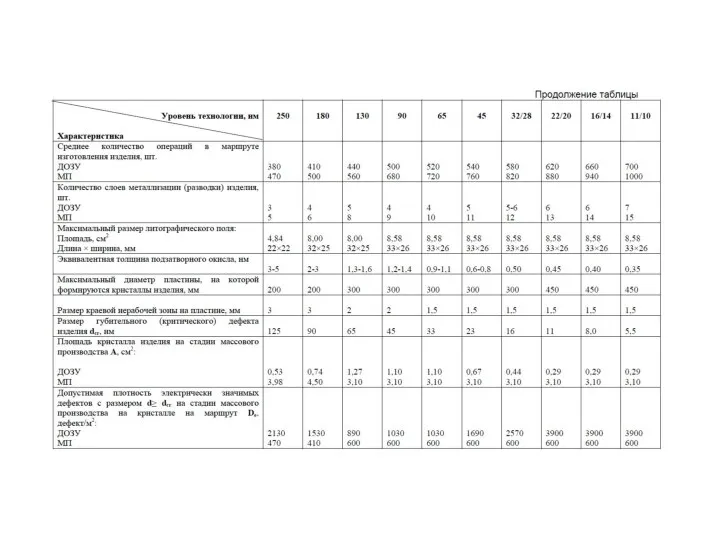

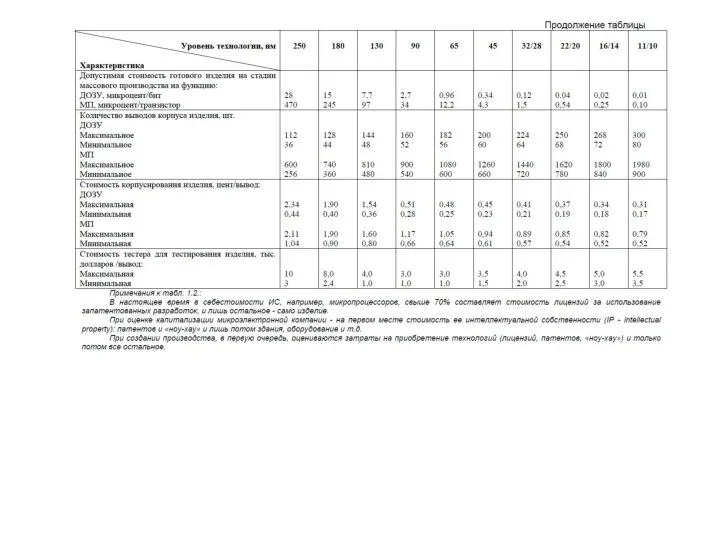

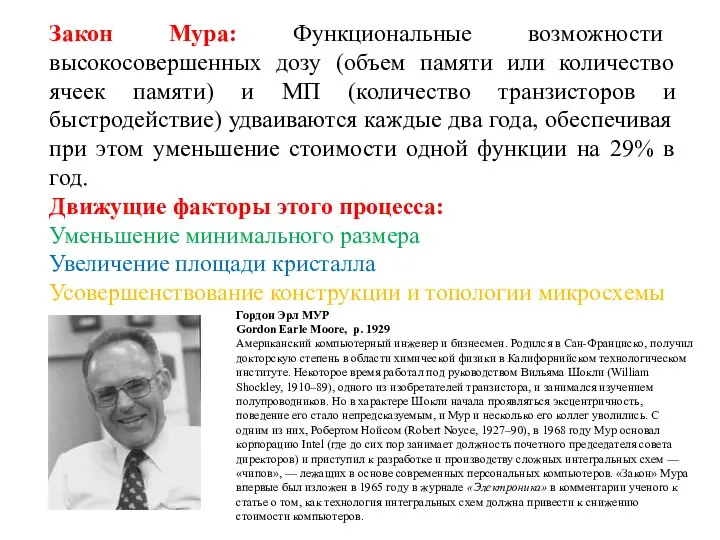

- 65. Закон Мура: Функциональные возможности высокосовершенных дозу (объем памяти или количество ячеек памяти) и МП (количество транзисторов

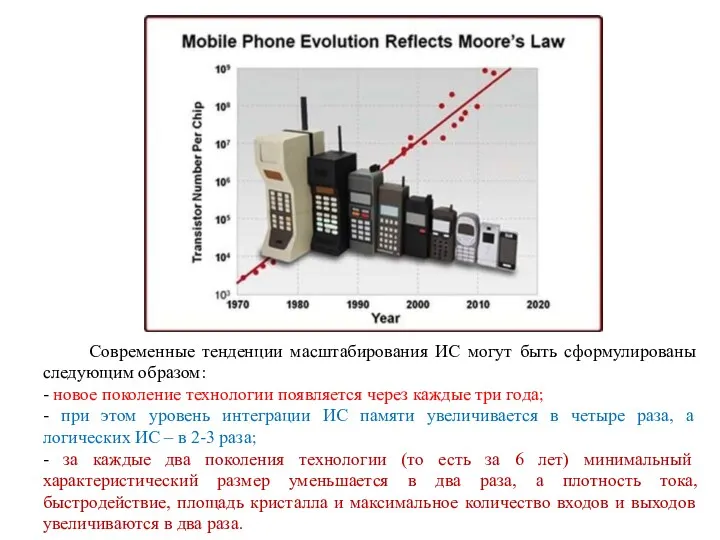

- 66. Современные тенденции масштабирования ИС могут быть сформулированы следующим образом: - новое поколение технологии появляется через каждые

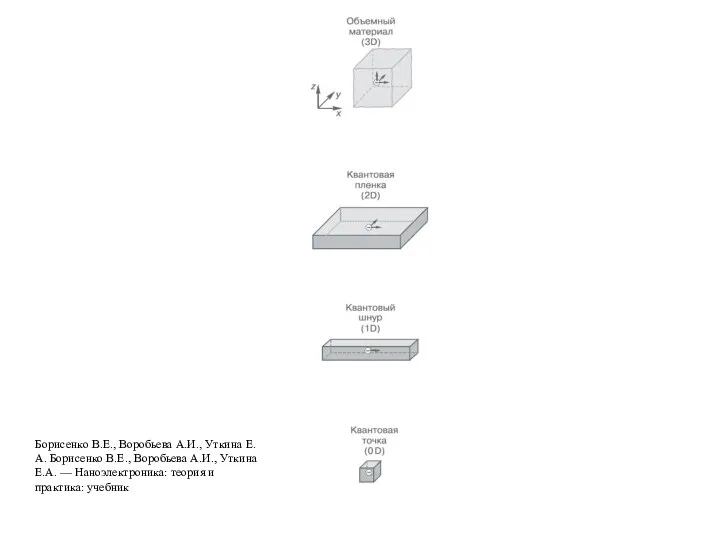

- 67. Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И., Уткина Е.А. — Наноэлектроника: теория и

- 68. Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко В.Е., Воробьева А.И., Уткина Е.А. — Наноэлектроника: теория и

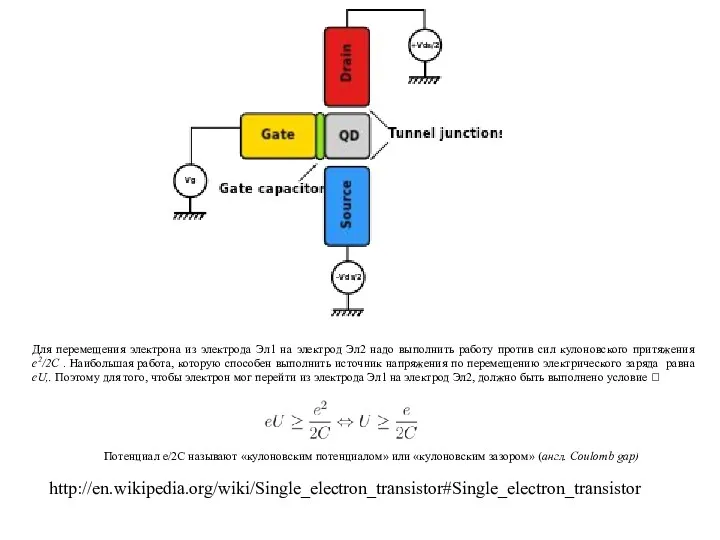

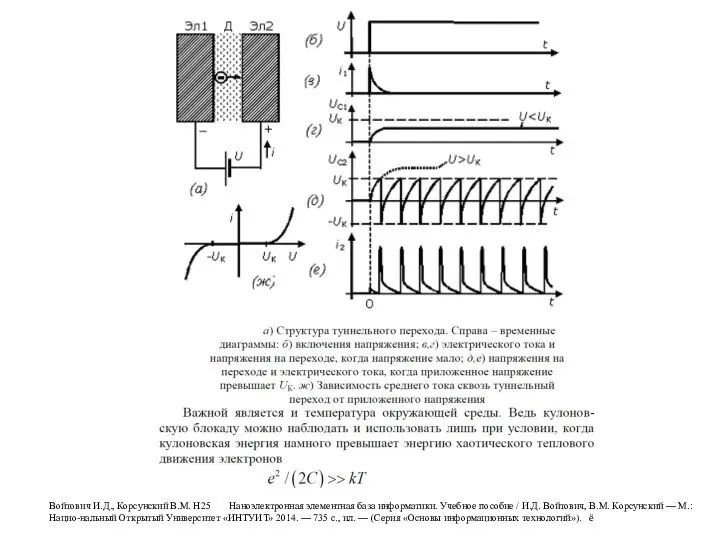

- 69. http://en.wikipedia.org/wiki/Single_electron_transistor#Single_electron_transistor Для перемещения электрона из электрода Эл1 на электрод Эл2 надо выполнить работу против сил кулоновского

- 70. Войтович И.Д., Корсунский В.М. Н25 Наноэлектронная элементная база информатики. Учебное пособие / И.Д. Войтович, В.М. Корсунский

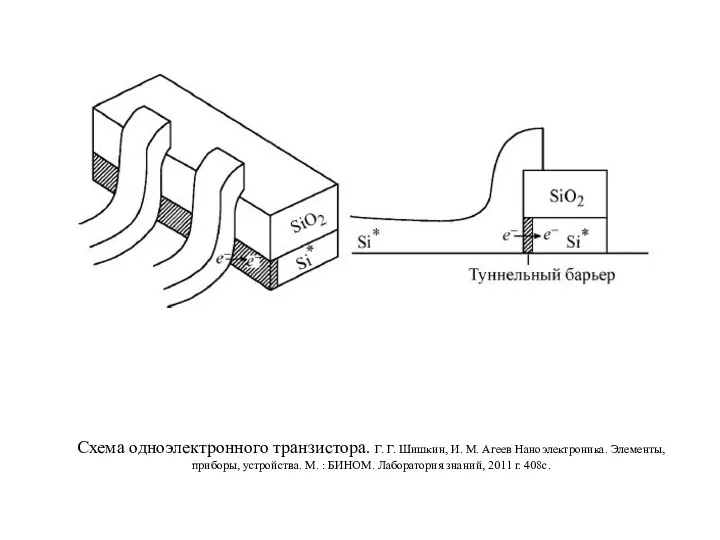

- 71. Схема одноэлектронного транзистора. Г. Г. Шишкин, И. М. Агеев Наноэлектроника. Элементы, приборы, устройства. М. : БИНОМ.

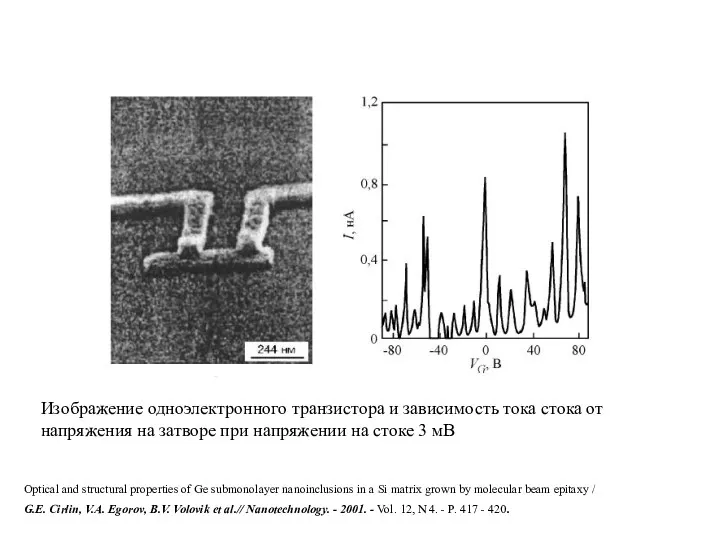

- 72. Изображение одноэлектронного транзистора и зависимость тока стока от напряжения на затворе при напряжении на стоке 3

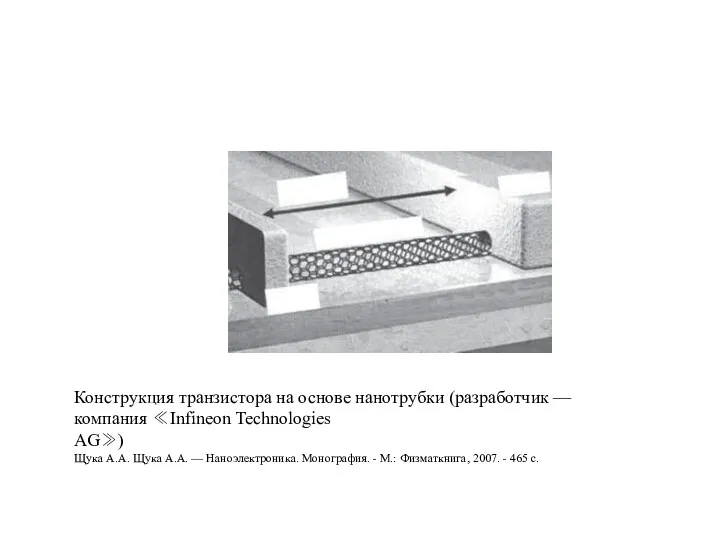

- 73. Конструкция транзистора на основе нанотрубки (разработчик — компания ≪Infineon Technologies AG≫) Щука А.А. Щука А.А. —

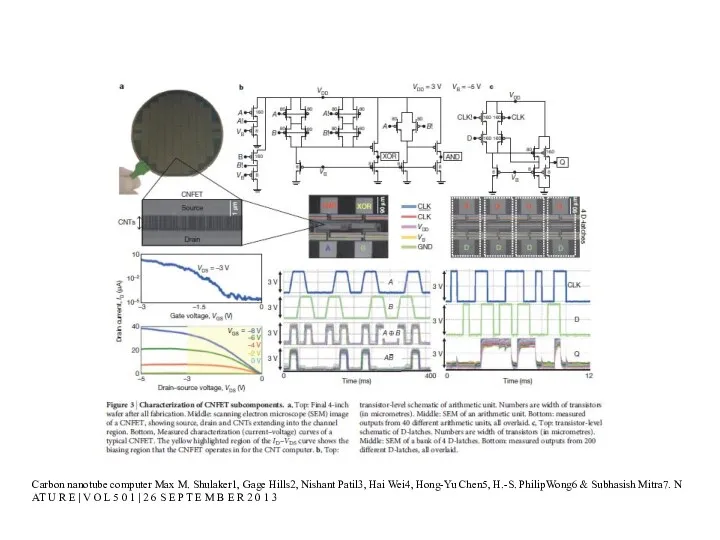

- 74. Carbon nanotube computer Max M. Shulaker1, Gage Hills2, Nishant Patil3, Hai Wei4, Hong-Yu Chen5, H.-S. PhilipWong6

- 75. В нанотехнологиях различают два основных подхода, позволяющих формировать наноструктуры. Это — технологии, реализующие принцип ≪сверху-вниз≫, и

- 76. Использование АСМ для локального окисления металлов и полупроводников

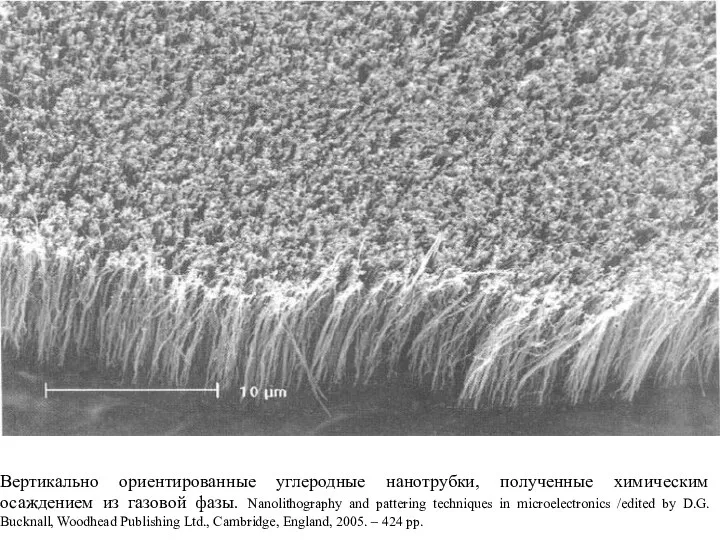

- 77. Вертикально ориентированные углеродные нанотрубки, полученные химическим осаждением из газовой фазы. Nanolithography and pattering techniques in microelectronics

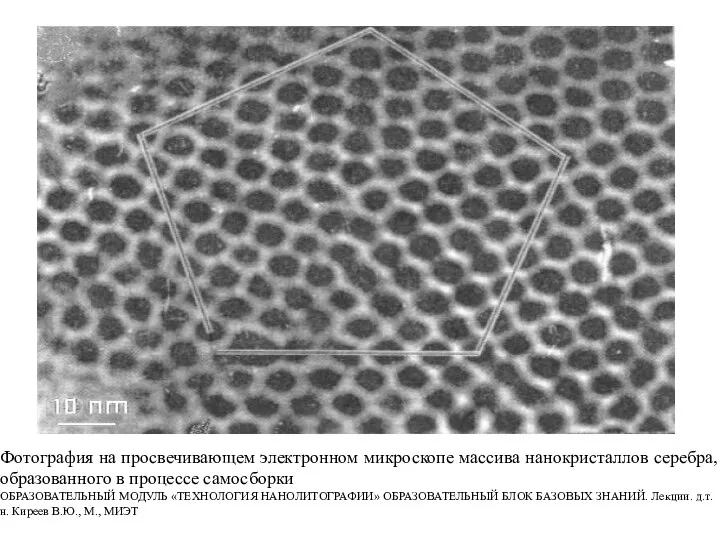

- 78. Фотография на просвечивающем электронном микроскопе массива нанокристаллов серебра, образованного в процессе самосборки ОБРАЗОВАТЕЛЬНЫЙ МОДУЛЬ «ТЕХНОЛОГИЯ НАНОЛИТОГРАФИИ»

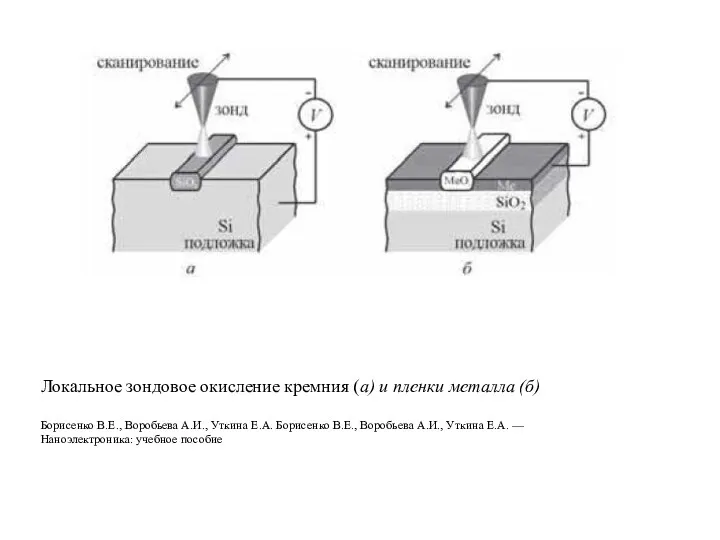

- 79. Локальное зондовое окисление кремния (а) и пленки металла (б) Борисенко В.Е., Воробьева А.И., Уткина Е.А. Борисенко

- 80. Принцип проекционной литографии

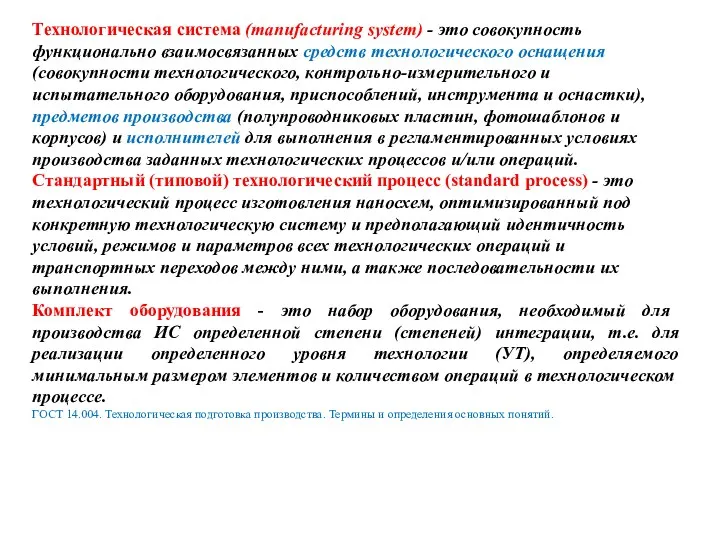

- 81. Технологическая система (manufacturing system) - это совокупность функционально взаимосвязанных средств технологического оснащения (совокупности технологического, контрольно-измерительного и

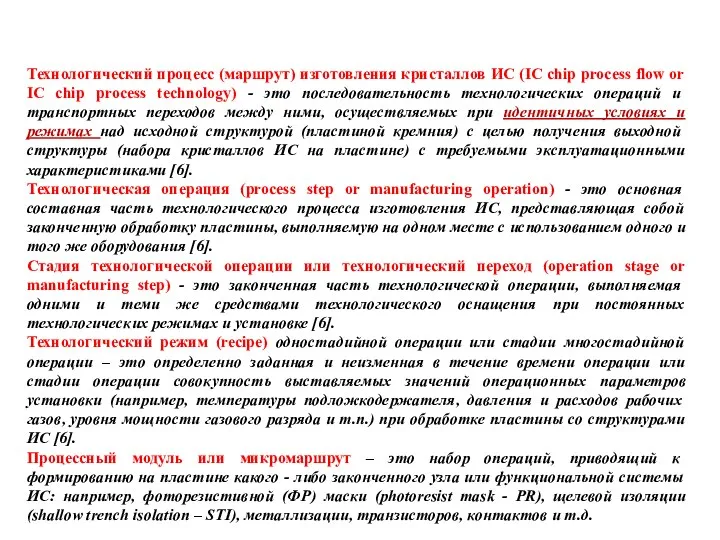

- 82. Технологический процесс (маршрут) изготовления кристаллов ИС (IC chip process flow or IC chip process technology) -

- 84. Скачать презентацию

Твердение ЖБ изделий

Твердение ЖБ изделий Тема учебного проекта: Знакомство с космосом Автор: Ильинская Ольга Владимировна, учитель начальных классов, МОУ лицей№41 г.Костромы 2010-2011 уч. год

Тема учебного проекта: Знакомство с космосом Автор: Ильинская Ольга Владимировна, учитель начальных классов, МОУ лицей№41 г.Костромы 2010-2011 уч. год Жерасты органдары. Тропизмдер

Жерасты органдары. Тропизмдер Презентация для родительского собрания

Презентация для родительского собрания Эксплуатация тракторов МТЗ-80/82

Эксплуатация тракторов МТЗ-80/82 Эколого-благотворительный проект #Добрые крышечки

Эколого-благотворительный проект #Добрые крышечки Исследование спинномозговой жидкости

Исследование спинномозговой жидкости Презентация аналитического отчета художественно-эстетического направления (хореография).

Презентация аналитического отчета художественно-эстетического направления (хореография). Модель обучения в ОАО МЦТ

Модель обучения в ОАО МЦТ Возрастная периодизация развития школьников и её учет в обучении и воспитании

Возрастная периодизация развития школьников и её учет в обучении и воспитании Методический семинар.Концептуальное изложение опыта работы по теме самообразования.

Методический семинар.Концептуальное изложение опыта работы по теме самообразования. Опиливание заготовок из металла и пластмассы

Опиливание заготовок из металла и пластмассы Большие ИМС

Большие ИМС Italy is one of the most beautiful countries in Europe

Italy is one of the most beautiful countries in Europe Игра на 8 марта Угадай мелодию

Игра на 8 марта Угадай мелодию Что родителям нужно знать о ЕГЭ, ОГЭ?

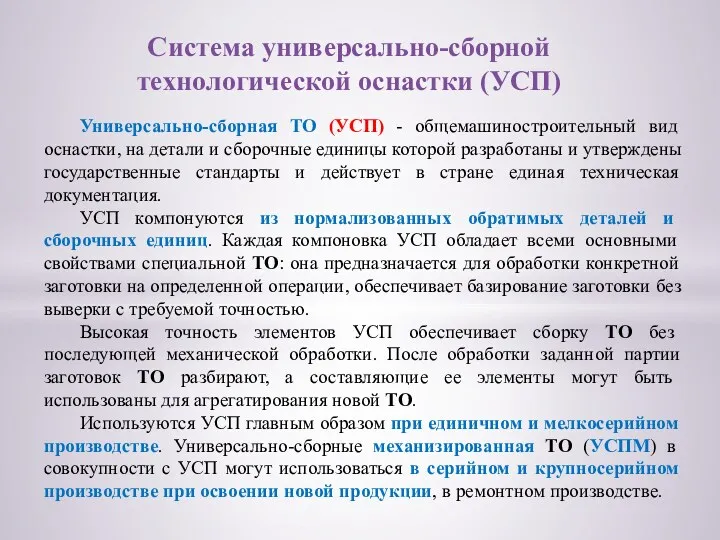

Что родителям нужно знать о ЕГЭ, ОГЭ? Система универсально-сборной технологической оснастки (УСП) станков

Система универсально-сборной технологической оснастки (УСП) станков Речевые нарушения

Речевые нарушения Профессия воспитатель

Профессия воспитатель Презентация Готовимся к аттестации!

Презентация Готовимся к аттестации! крылатые выражения из романа Евгений Онегин

крылатые выражения из романа Евгений Онегин Прогнозування, планування та регулювання діяльності підприємства. Лекція 2

Прогнозування, планування та регулювання діяльності підприємства. Лекція 2 Чинники ризику, стрес і здоров'я людини

Чинники ризику, стрес і здоров'я людини Удивительные растения экваториальных лесов Южной Америки

Удивительные растения экваториальных лесов Южной Америки Якуб Колас

Якуб Колас Машинобудування в Україні

Машинобудування в Україні Презентация к урокам технологии. Работа с пластилином и природными материалами.

Презентация к урокам технологии. Работа с пластилином и природными материалами. Эпоха Просвещения

Эпоха Просвещения