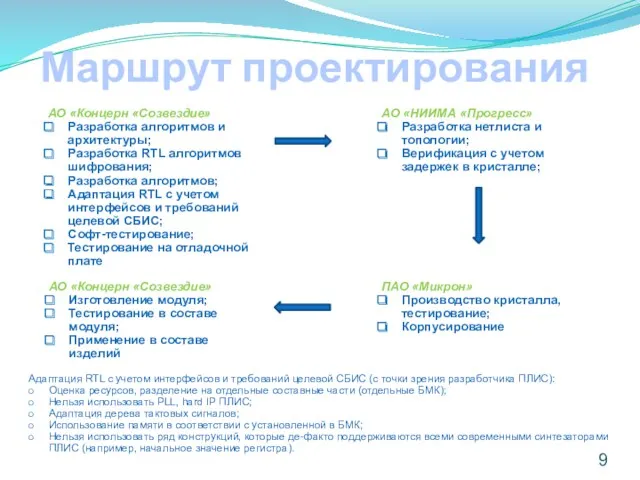

Маршрут проектирования

АО «Концерн «Созвездие»

Разработка алгоритмов и архитектуры;

Разработка RTL алгоритмов шифрования;

Разработка

алгоритмов;

Адаптация RTL с учетом интерфейсов и требований целевой СБИС;

Софт-тестирование;

Тестирование на отладочной плате

АО «НИИМА «Прогресс»

Разработка нетлиста и топологии;

Верификация с учетом задержек в кристалле;

ПАО «Микрон»

Производство кристалла, тестирование;

Корпусирование

АО «Концерн «Созвездие»

Изготовление модуля;

Тестирование в составе модуля;

Применение в составе изделий

Адаптация RTL с учетом интерфейсов и требований целевой СБИС (с точки зрения разработчика ПЛИС):

Оценка ресурсов, разделение на отдельные составные части (отдельные БМК);

Нельзя использовать PLL, hard IP ПЛИС;

Адаптация дерева тактовых сигналов;

Использование памяти в соответствии с установленной в БМК;

Нельзя использовать ряд конструкций, которые де-факто поддерживаются всеми современными синтезаторами ПЛИС (например, начальное значение регистра).

Презентация к уроки технологии в 3 классе Работа с тканью

Презентация к уроки технологии в 3 классе Работа с тканью Отражения. Принцип построения отражений

Отражения. Принцип построения отражений Классный час Мир моих увлечений 2-3 класс

Классный час Мир моих увлечений 2-3 класс Вавилонский царь Хаммурапи и его законы

Вавилонский царь Хаммурапи и его законы Социальное проектирование

Социальное проектирование هوش مصنوعی

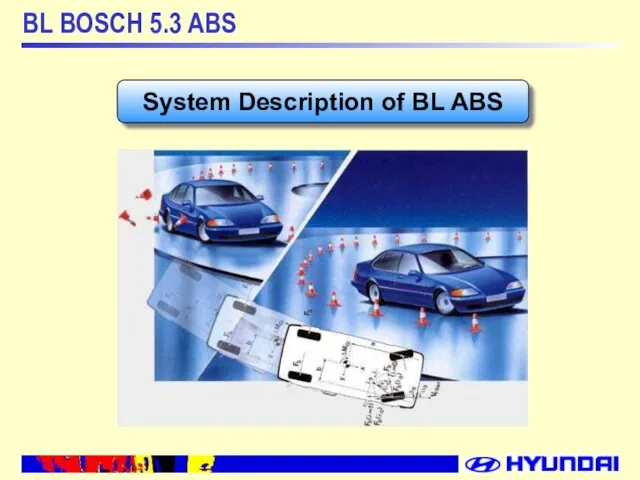

هوش مصنوعی BL BOSCH 5.3 ABS. System Description of BL ABS

BL BOSCH 5.3 ABS. System Description of BL ABS Презентация подвиг во имя жизни

Презентация подвиг во имя жизни Презентация кружка Волшебные краски 2 часть

Презентация кружка Волшебные краски 2 часть Моделирование плечевого изделия с цельнокроеным рукавом. 6 класс

Моделирование плечевого изделия с цельнокроеным рукавом. 6 класс Сказочная страна (ИЗО)

Сказочная страна (ИЗО) Мы за здоровый образ жизни. Познавательный час

Мы за здоровый образ жизни. Познавательный час Создание функций из массива данных. Интерполяция. Регрессия. Прикладные методы расчета и программные комплексы (4)

Создание функций из массива данных. Интерполяция. Регрессия. Прикладные методы расчета и программные комплексы (4) Консультация для воспитателей Развитие фонематического слуха у детей дошкольного возраста

Консультация для воспитателей Развитие фонематического слуха у детей дошкольного возраста Архитектура персонального компьютера

Архитектура персонального компьютера Монтаж установки предварительной очистки ППФ. Монтаж установки очистки пропилена от каталитических ядов

Монтаж установки предварительной очистки ППФ. Монтаж установки очистки пропилена от каталитических ядов Западная Европа в ХI-ХIII веках. Инквизиция и крестовые походы

Западная Европа в ХI-ХIII веках. Инквизиция и крестовые походы Учимся рисовать ракету

Учимся рисовать ракету Многоатомные спирты

Многоатомные спирты Политико-правовые идеи Древней Греции

Политико-правовые идеи Древней Греции Фото

Фото Электротехнические комплексы

Электротехнические комплексы Общественное движение при Александре I

Общественное движение при Александре I Медиаторы нервной системы

Медиаторы нервной системы Нейрон. Его свойства и функции

Нейрон. Его свойства и функции Теоретические основы реструктуризации

Теоретические основы реструктуризации Кто говорит, что на войне не страшно, тот ничего не знает о войне. 9 мая - День Победы

Кто говорит, что на войне не страшно, тот ничего не знает о войне. 9 мая - День Победы Черная металлургия России. Изделия из чугуна и стали

Черная металлургия России. Изделия из чугуна и стали