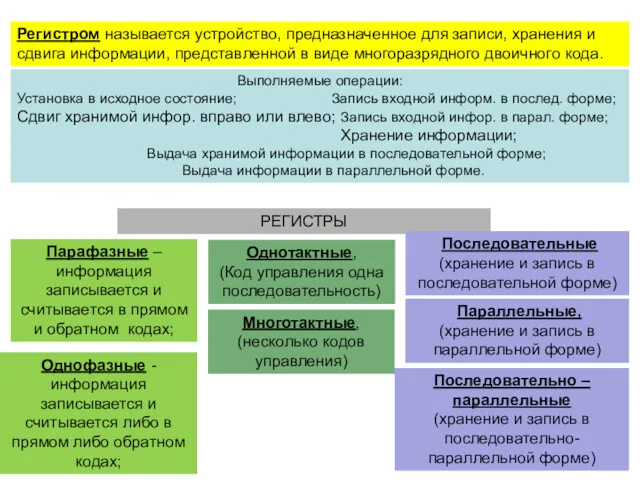

Регистром называется устройство, предназначенное для записи, хранения и сдвига информации, представленной

в виде многоразрядного двоичного кода.

РЕГИСТРЫ

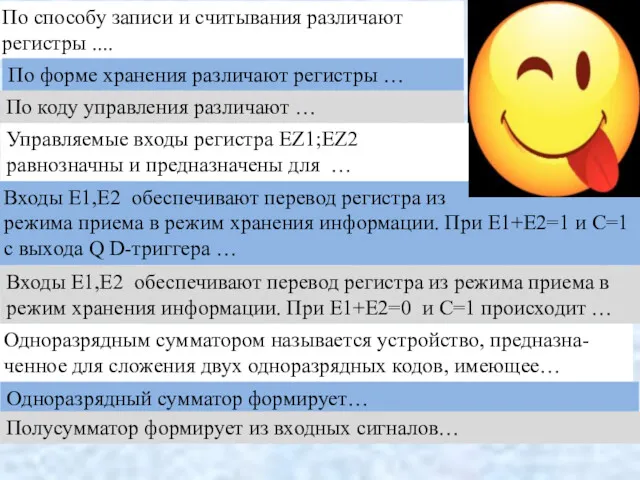

Парафазные – информация записывается и считывается в прямом и обратном кодах;

Однофазные -информация записывается и считывается либо в прямом либо обратном кодах;

Однотактные,

(Код управления одна последовательность)

Многотактные,

(несколько кодов управления)

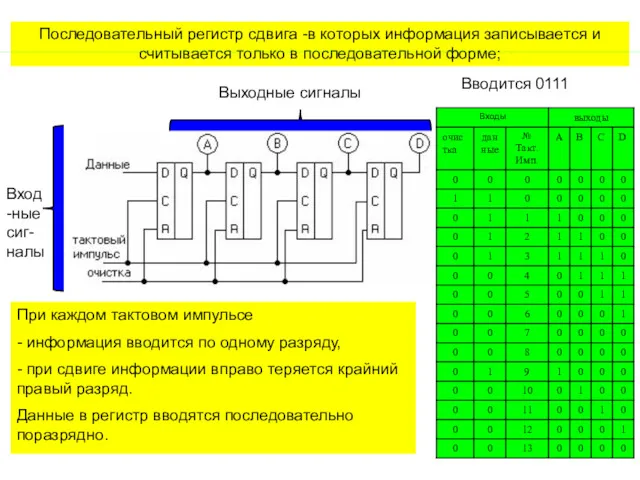

Последовательные (хранение и запись в последовательной форме)

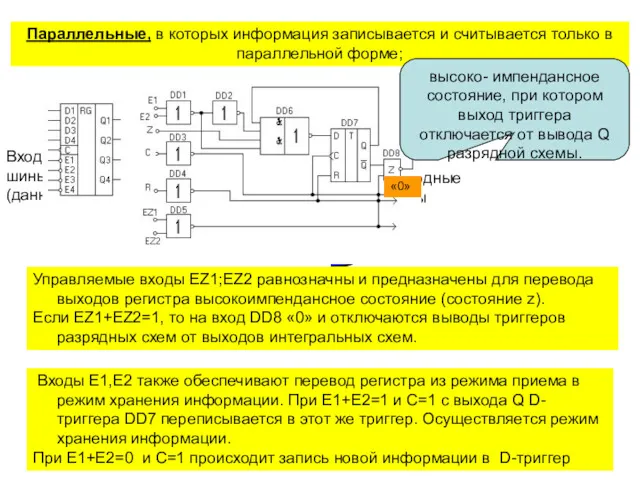

Параллельные,

(хранение и запись в параллельной форме)

Последовательно – параллельные

(хранение и запись в последовательно-параллельной форме)

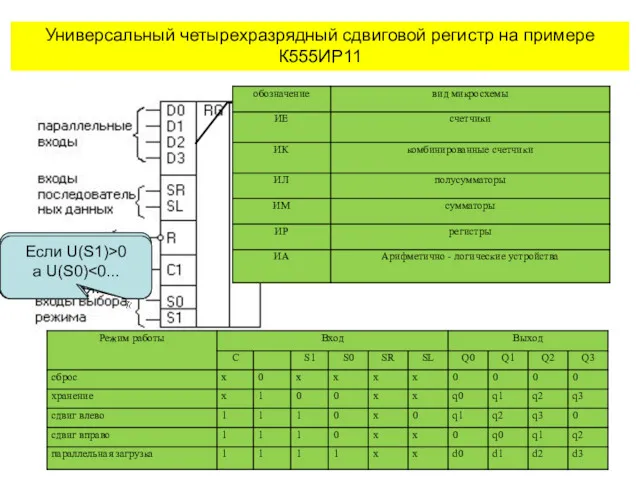

Выполняемые операции:

Установка в исходное состояние; Запись входной информ. в послед. форме;

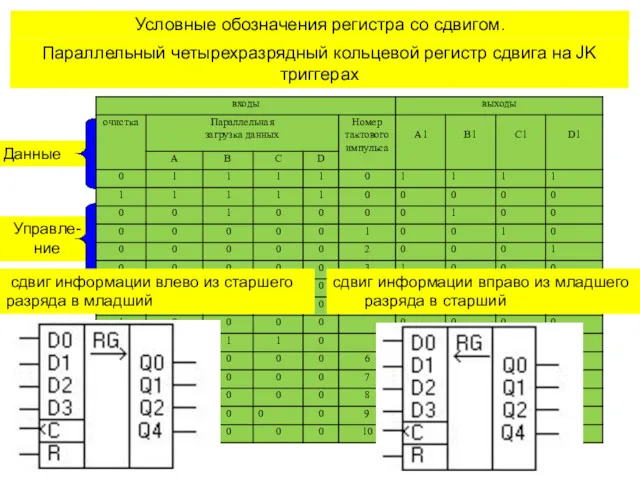

Сдвиг хранимой инфор. вправо или влево; Запись входной инфор. в парал. форме;

Хранение информации;

Выдача хранимой информации в последовательной форме;

Выдача информации в параллельной форме.

в Лекция 6

в Лекция 6 презентация Формирование связной речи у детей с заиканием

презентация Формирование связной речи у детей с заиканием Український модерн

Український модерн Реконструкция и реновация особняков России

Реконструкция и реновация особняков России Конструктивные особенности самоходных опрыскивателей серии SP

Конструктивные особенности самоходных опрыскивателей серии SP Воздух и его состав

Воздух и его состав Принципы построения параллельных вычислительных систем

Принципы построения параллельных вычислительных систем Сочинение-описание по картине Т. Н. Яблонской Утро

Сочинение-описание по картине Т. Н. Яблонской Утро Технология разработки СБИС типа СнК на отечественной платформе по заданным алгоритмам

Технология разработки СБИС типа СнК на отечественной платформе по заданным алгоритмам Конспект урока по математике Решение примеров на нахождение неизвестного слагаемого

Конспект урока по математике Решение примеров на нахождение неизвестного слагаемого Организация торговли на борту ВС. Обучение бортпроводников

Организация торговли на борту ВС. Обучение бортпроводников Организация работы банковской системы в области противодействия легализации (отмыванию) доходов, полученных преступным путем

Организация работы банковской системы в области противодействия легализации (отмыванию) доходов, полученных преступным путем Характеристика карьерных дорог

Характеристика карьерных дорог Европейская и русская культурологическая мысль XIX века

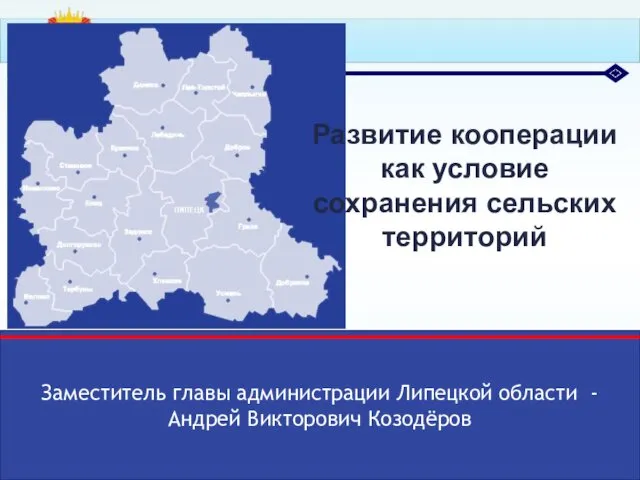

Европейская и русская культурологическая мысль XIX века Развитие кооперации в Липецкой области

Развитие кооперации в Липецкой области РМО учителей географии

РМО учителей географии Компания Петро-Композит. Проект Зеленый город

Компания Петро-Композит. Проект Зеленый город Каждой пичужке кормушка. Краевая Акция Экологический марафон

Каждой пичужке кормушка. Краевая Акция Экологический марафон Веселые старты, посвященные Дню Защитника Отечества. Выше голову будущий солдат

Веселые старты, посвященные Дню Защитника Отечества. Выше голову будущий солдат Скелетная травма

Скелетная травма Проект моя Родина

Проект моя Родина Прекращение трудового договора по инициативе работодателя

Прекращение трудового договора по инициативе работодателя Сортировка в массивах. Методы сортировки

Сортировка в массивах. Методы сортировки Сказка как средство развития эмоциональной сферы у дошкольников

Сказка как средство развития эмоциональной сферы у дошкольников Классный час 2014 год - год культуры России Диск

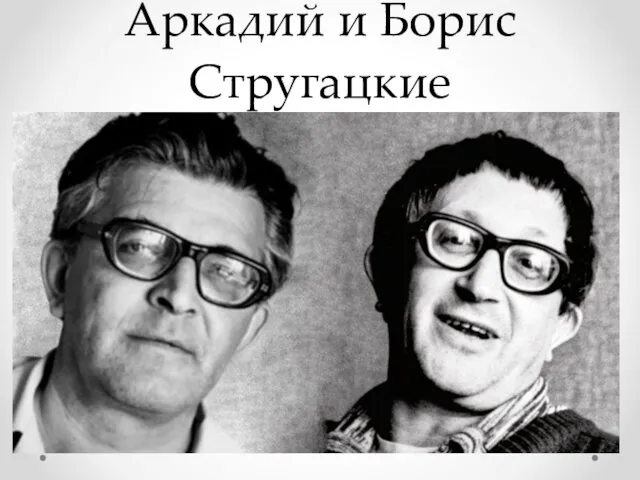

Классный час 2014 год - год культуры России Диск Аркадий и Борис Стругацкие

Аркадий и Борис Стругацкие She/from. He/from

She/from. He/from Презентация к родительскому собранию на тему: Фейерверки и пиротехника. Друзья или враги?

Презентация к родительскому собранию на тему: Фейерверки и пиротехника. Друзья или враги?