Содержание

- 2. Магистраль Устройство компьютера

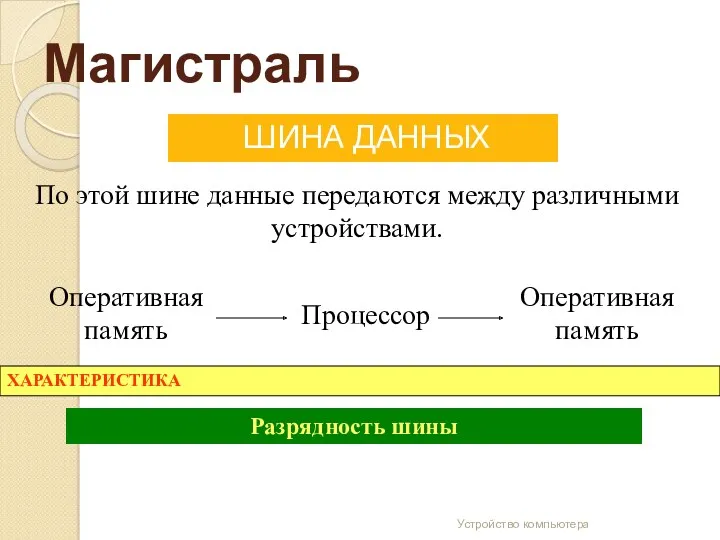

- 3. Магистраль ШИНА ДАННЫХ Устройство компьютера По этой шине данные передаются между различными устройствами. Оперативная память Оперативная

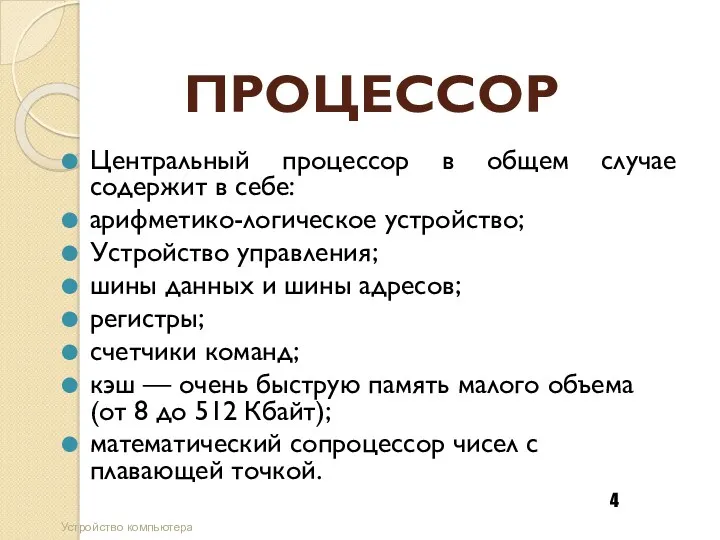

- 4. ПРОЦЕССОР Центральный процессор в общем случае содержит в себе: арифметико-логическое устройство; Устройство управления; шины данных и

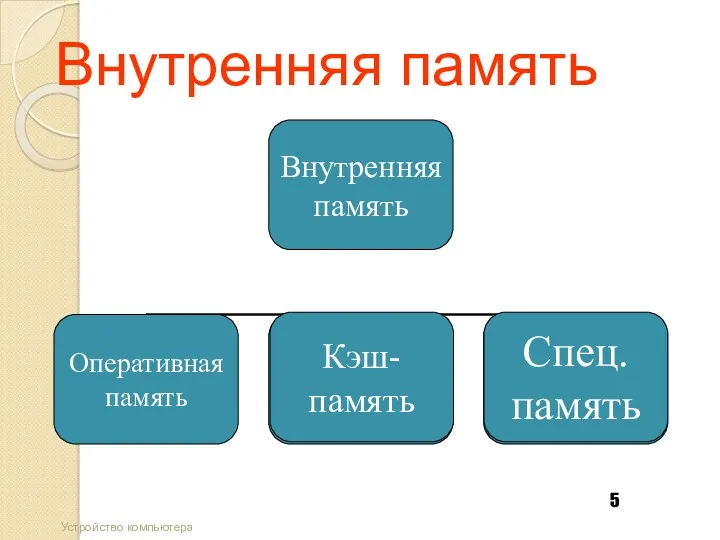

- 5. Внутренняя память Устройство компьютера

- 6. Арифметико-логическое устройство

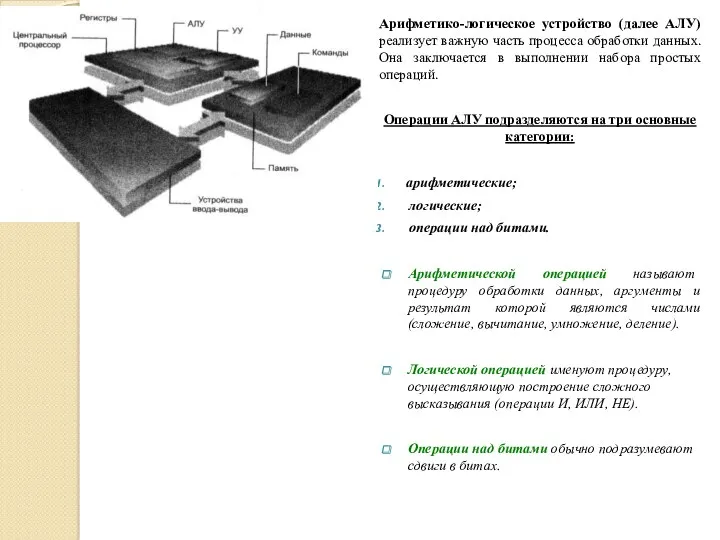

- 7. Арифметико-логическое устройство (далее АЛУ) реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых

- 8. История создания АЛУ Разработчик компьютера ENIAC, Джон фон Нейман, был первым создателем АЛУ. В 1945 году

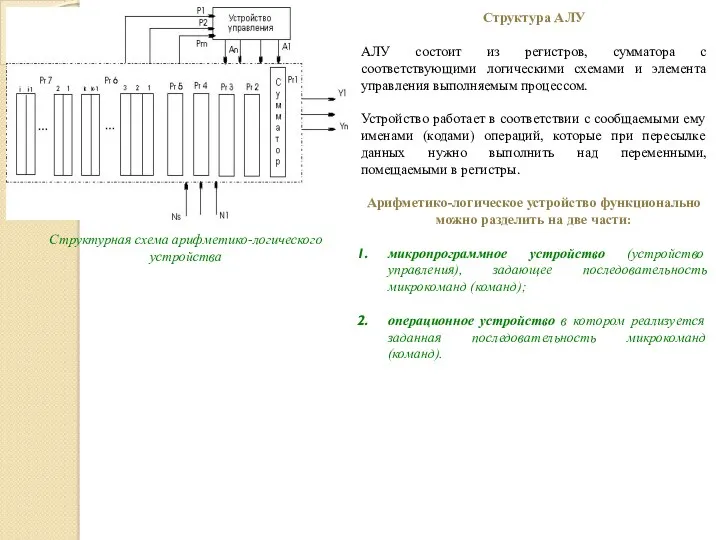

- 9. Структура АЛУ АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом.

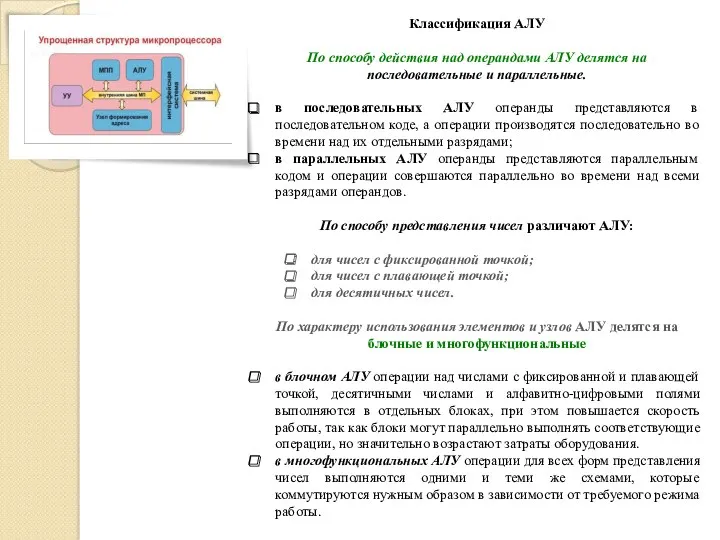

- 10. Классификация АЛУ По способу действия над операндами АЛУ делятся на последовательные и параллельные. в последовательных АЛУ

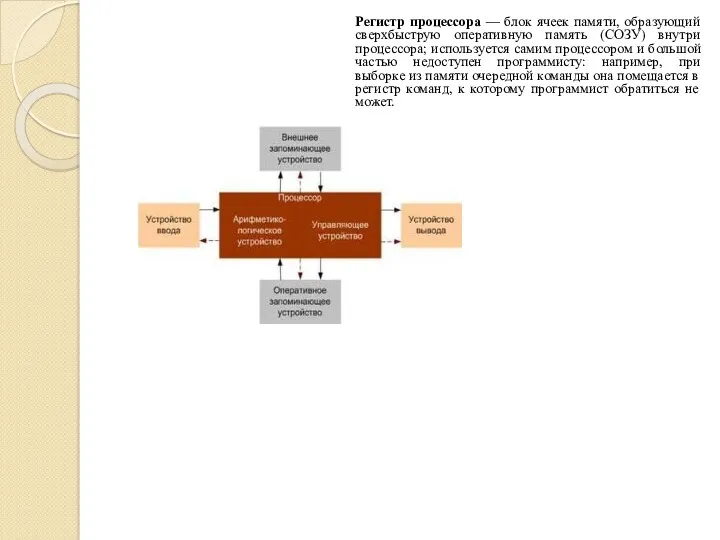

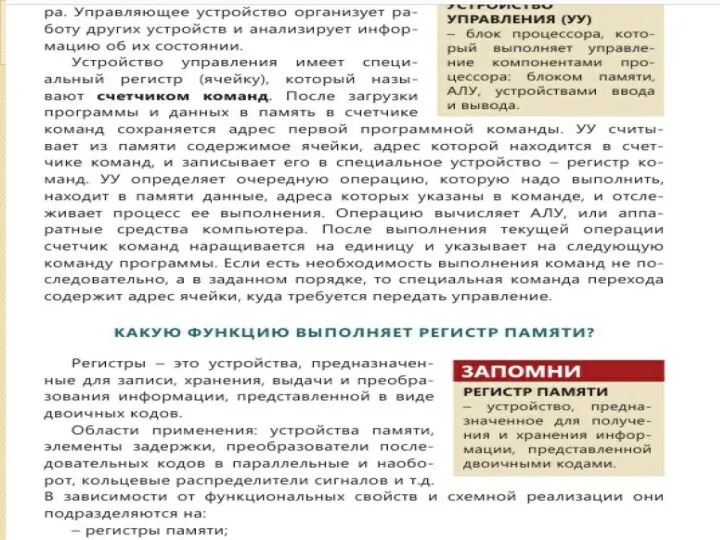

- 11. Регистр процессора — блок ячеек памяти, образующий сверхбыструю оперативную память (СОЗУ) внутри процессора; используется самим процессором

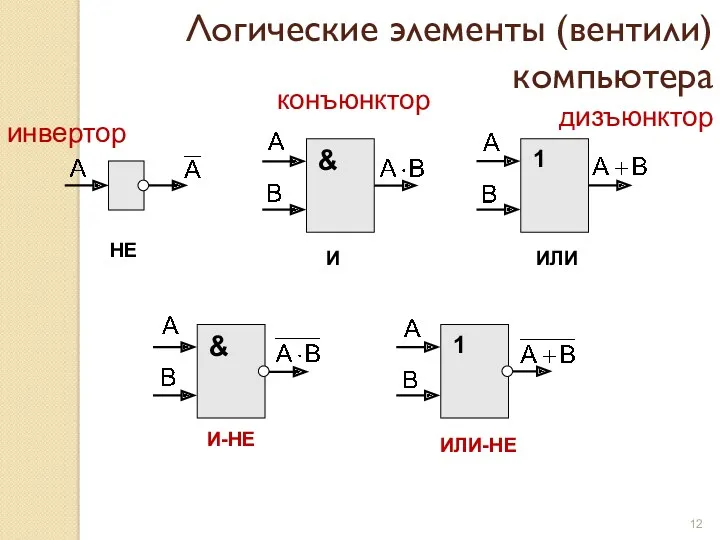

- 12. Логические элементы (вентили) компьютера НЕ И ИЛИ ИЛИ-НЕ И-НЕ инвертор конъюнктор дизъюнктор

- 13. С помощью логических элементов НЕ, И, ИЛИ можно реализовать (собрать как из конструктора) типовые функциональные узлы

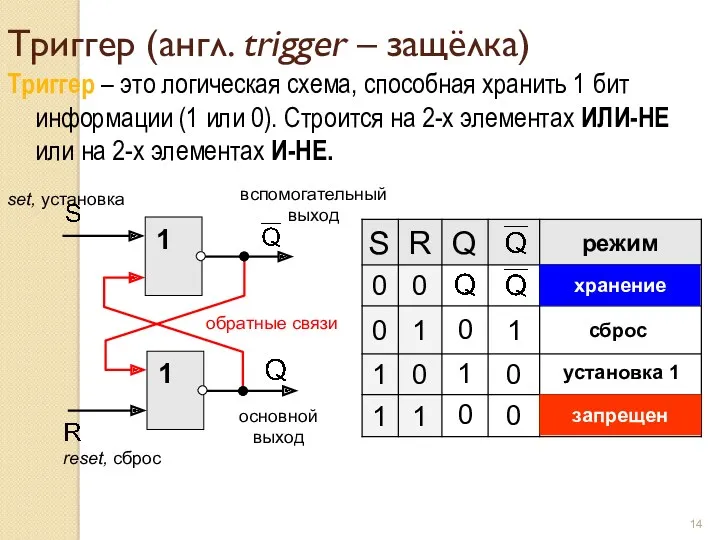

- 14. Триггер (англ. trigger – защёлка) Триггер – это логическая схема, способная хранить 1 бит информации (1

- 15. Полусумматор Полусумматор – это логическая схема, способная складывать два одноразрядных двоичных числа. 0 0 0 1

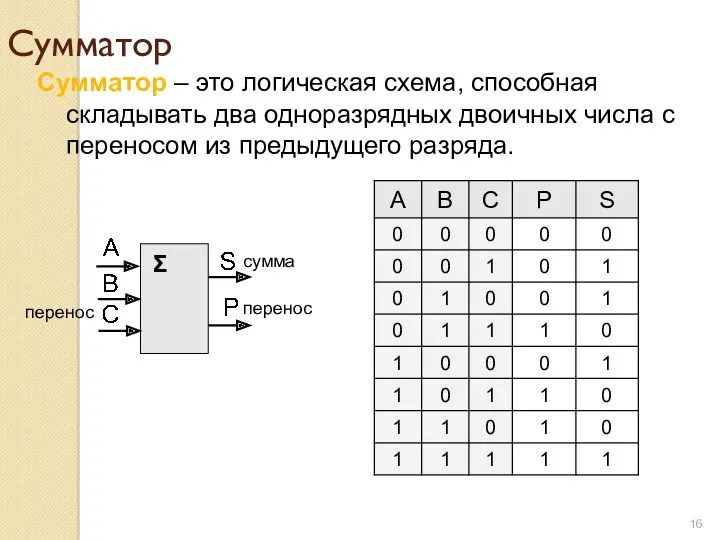

- 16. Сумматор Сумматор – это логическая схема, способная складывать два одноразрядных двоичных числа с переносом из предыдущего

- 19. Скачать презентацию

Дерматомиозит (Полимиозит)

Дерматомиозит (Полимиозит) Математическая мозаика. Задачи на смекалку

Математическая мозаика. Задачи на смекалку Из опыта работы

Из опыта работы Виды орнаментов (1 класс)

Виды орнаментов (1 класс) Респираторно - синцитиальная инфекция

Респираторно - синцитиальная инфекция Принципы, методы и средства обеспечения безопасности

Принципы, методы и средства обеспечения безопасности Геометрические фигуры

Геометрические фигуры Презентация :История нашего детского сада

Презентация :История нашего детского сада Презентация к викторине посвященная дню Победы

Презентация к викторине посвященная дню Победы Особенности учета и аудита товаров в розничной торговли (на примере ООО фирма Холам-М)

Особенности учета и аудита товаров в розничной торговли (на примере ООО фирма Холам-М) Сладкие блюда и напитки. Часть 1

Сладкие блюда и напитки. Часть 1 Культура Руси IX-XII веков

Культура Руси IX-XII веков Философия творчества

Философия творчества Negligence

Negligence Капризная кошка

Капризная кошка КОМПЬЮТЕРНАЯ ПРЕЗЕНТАЦИЯ ПО ГЕОГРАФИИ 11 КЛАСС ФРГ

КОМПЬЮТЕРНАЯ ПРЕЗЕНТАЦИЯ ПО ГЕОГРАФИИ 11 КЛАСС ФРГ Why do you need to learn English

Why do you need to learn English Учимся готовить: десерт Клубничка

Учимся готовить: десерт Клубничка Административное право Японии

Административное право Японии Товарный знак. Сходство до степени смешения

Товарный знак. Сходство до степени смешения досуг 23 февраля Диск

досуг 23 февраля Диск Социальный проект Каменск - город воинской доблести

Социальный проект Каменск - город воинской доблести Лавинно-пролётный диод

Лавинно-пролётный диод Статистические гипотезы и критерии. Этапы принятия статистического решения

Статистические гипотезы и критерии. Этапы принятия статистического решения Новогоднее украшение кабинета. Серебряные узоры

Новогоднее украшение кабинета. Серебряные узоры Тест по теме Теория вероятностей

Тест по теме Теория вероятностей Консультация для родителей Советы от доктора Айболита

Консультация для родителей Советы от доктора Айболита Части речи

Части речи