Содержание

- 2. Многоразрядный параллельный сумматор может быть составлен из одноразрядных полных сумматоров, число которых равно числу разрядов слагаемых.

- 3. Из приведенной формулы видно, что повысить быстродействие параллельного сумматора можно двумя способами. Во-первых, уменьшением времени задержки

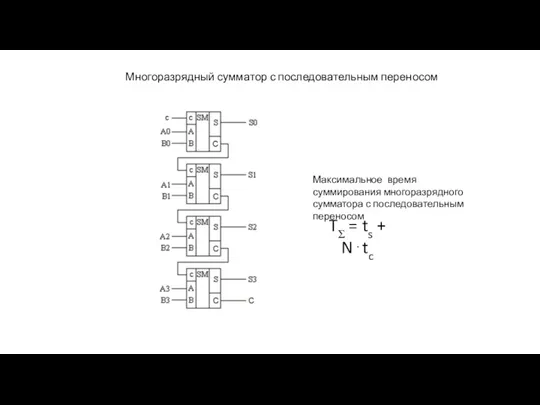

- 4. Многоразрядный сумматор с последовательным переносом TΣ = ts + N⋅tc Максимальное время суммирования многоразрядного сумматора с

- 5. Структура сумматора с цепями параллельного переноса Задержка Т получения суммы сумматора с параллельным переносом слагается из

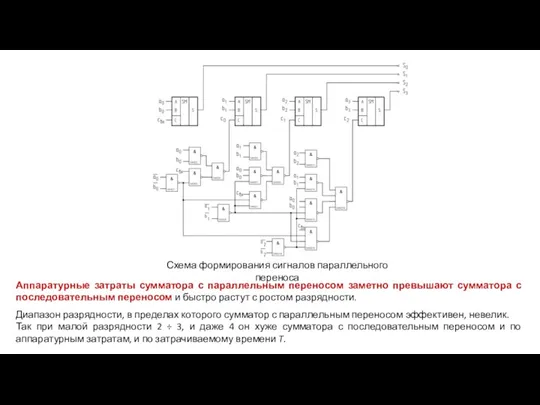

- 6. Схема формирования сигналов параллельного переноса Диапазон разрядности, в пределах которого сумматор с параллельным переносом эффективен, невелик.

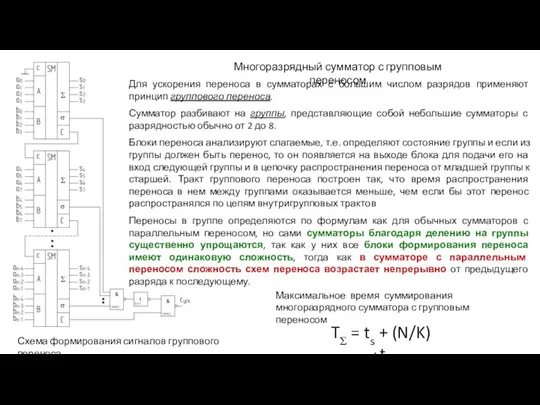

- 7. Схема формирования сигналов группового переноса Для ускорения переноса в сумматорах с большим числом разрядов применяют принцип

- 8. Как и в обычном сумматоре, который можно рассматривать как частный случай сумматора с групповым переносом, когда

- 9. Умножители

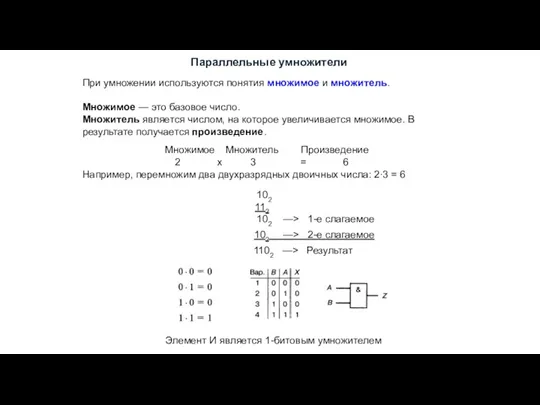

- 10. При умножении используются понятия множимое и множитель. Множимое — это базовое число. Множитель является числом, на

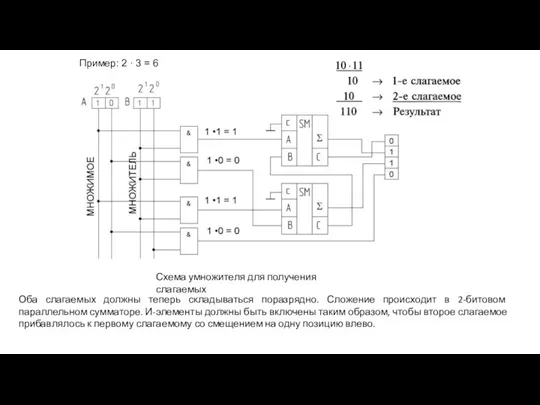

- 11. Схема умножителя для получения слагаемых Оба слагаемых должны теперь складываться поразрядно. Сложение происходит в 2-битовом параллельном

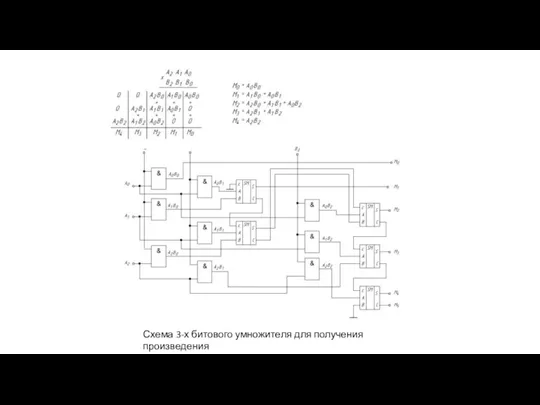

- 12. Схема 3-х битового умножителя для получения произведения

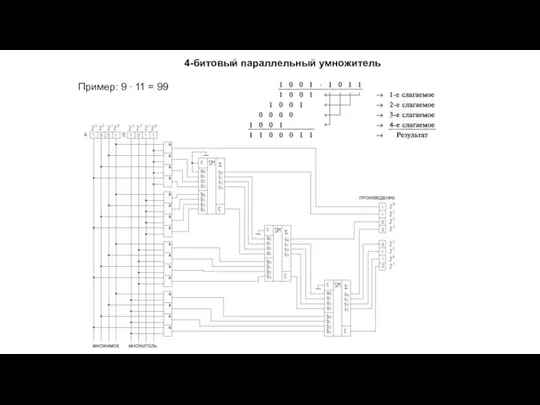

- 13. 4-битовый параллельный умножитель Пример: 9 ∙ 11 = 99

- 14. Арифметико-логические устройства

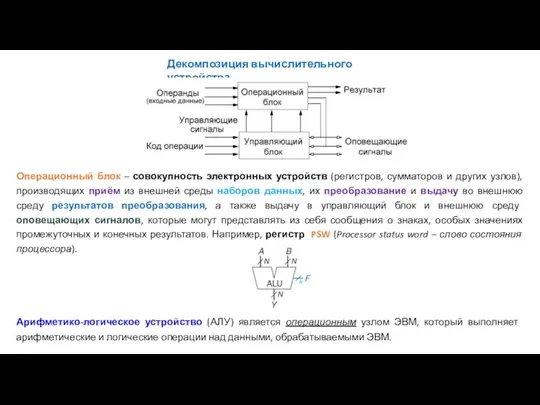

- 15. Декомпозиция вычислительного устройства Операционный блок – совокупность электронных устройств (регистров, сумматоров и других узлов), производящих приём

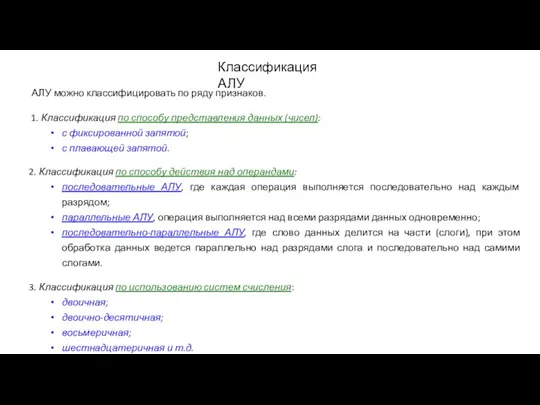

- 16. Классификация АЛУ АЛУ можно классифицировать по ряду признаков. 1. Классификация по способу представления данных (чисел): с

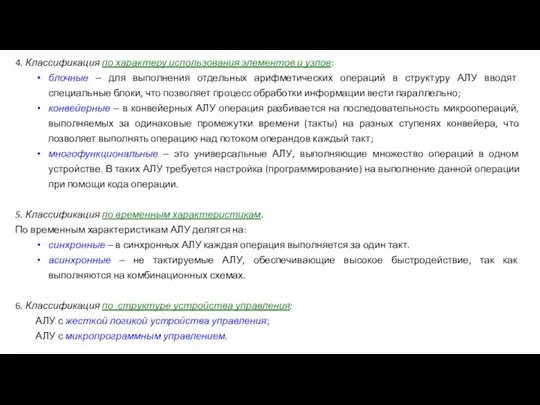

- 17. 4. Классификация по характеру использования элементов и узлов: блочные ‒ для выполнения отдельных арифметических операций в

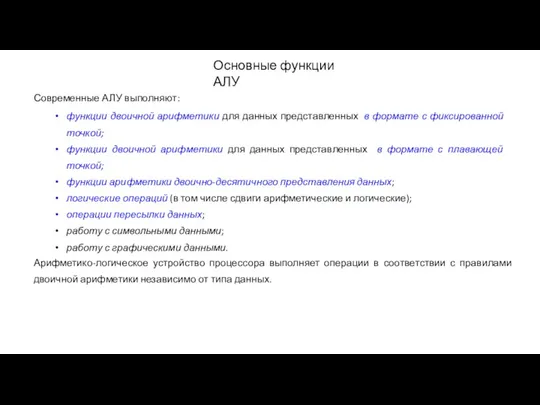

- 18. Современные АЛУ выполняют: функции двоичной арифметики для данных представленных в формате с фиксированной точкой; функции двоичной

- 19. Основные характеристики АЛУ можно разделить на количественные и качественные. Количественные характеристики определяют: скорость выполнения операций, время

- 20. УГО 4-х битного АЛУ К155ИП3 (SN74LS181) Таблица состояний АЛУ

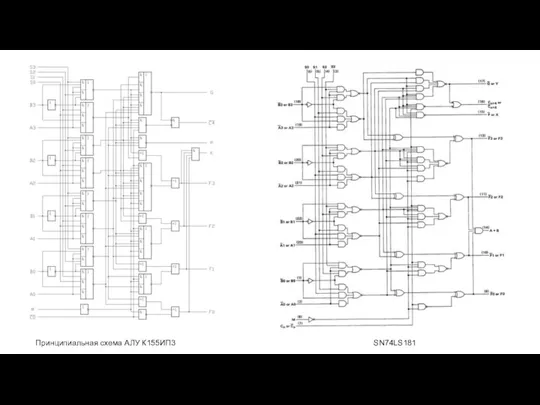

- 21. Принципиальная схема АЛУ К155ИП3 SN74LS181

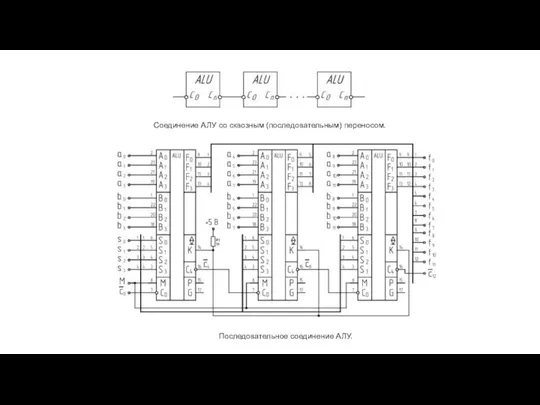

- 22. Соединение АЛУ со сквозным (последовательным) переносом. Последовательное соединение АЛУ.

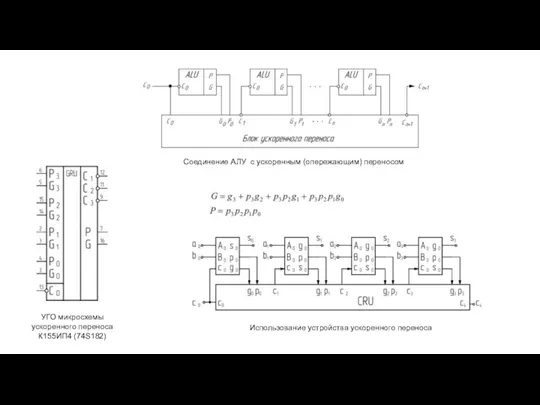

- 23. Соединение АЛУ с ускоренным (опережающим) переносом УГО микросхемы ускоренного переноса К155ИП4 (74S182) Использование устройства ускоренного переноса

- 25. Скачать презентацию

Организация глобальных сетей

Организация глобальных сетей Северный полюс. Кто первый?

Северный полюс. Кто первый? родительское собрание (презентация)

родительское собрание (презентация) Постоянные магниты. Магнитное поле Земли

Постоянные магниты. Магнитное поле Земли Особенности и проблемы информирования в СМИ о воздушно-спортивном эквилибре

Особенности и проблемы информирования в СМИ о воздушно-спортивном эквилибре Документация на строительство скважины. Лекция 19

Документация на строительство скважины. Лекция 19 Классификация грузовых автомобилей. Урок № 3.1

Классификация грузовых автомобилей. Урок № 3.1 Ветер. Общие закономерности

Ветер. Общие закономерности Массивы в Java

Массивы в Java Как помочь детям стать внимательнее

Как помочь детям стать внимательнее Перспективы развития микропроцессоров

Перспективы развития микропроцессоров Инженерные коммуникации в доме

Инженерные коммуникации в доме Родительское собрание для будущих первоклассников.

Родительское собрание для будущих первоклассников. презентация Пустыни Африки

презентация Пустыни Африки метод проектной деятельности в доу

метод проектной деятельности в доу Основы рационального питания.

Основы рационального питания. Методы воспитания. Классификация методов воспитания по Гришину

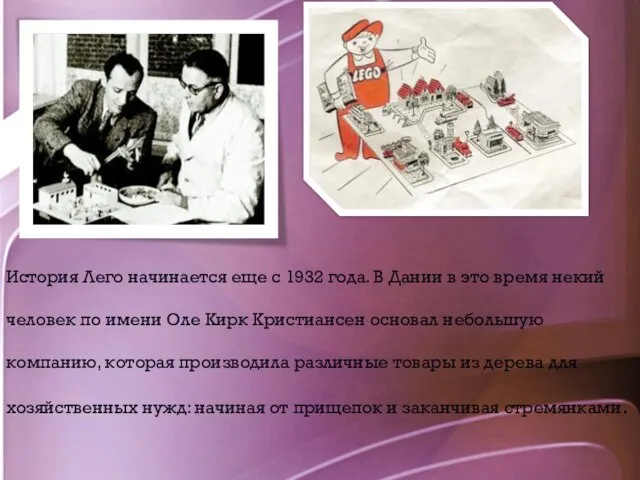

Методы воспитания. Классификация методов воспитания по Гришину Компания Лего

Компания Лего Набір ювелірних каблучок Сонячний вітер

Набір ювелірних каблучок Сонячний вітер تابع الفصل الثالث برنامج العروض التقديمية

تابع الفصل الثالث برنامج العروض التقديمية Компьютерная графика для строителей

Компьютерная графика для строителей Лазеры. (Лекция 7б)

Лазеры. (Лекция 7б) Презентация урока по математике 6 класс по теме: Случайные события. Вероятность случайного события

Презентация урока по математике 6 класс по теме: Случайные события. Вероятность случайного события Презентация к созданию электронного портфолио

Презентация к созданию электронного портфолио Житие преподобного Сергия Радонежского (в стихах)

Житие преподобного Сергия Радонежского (в стихах) Числовые последовательности

Числовые последовательности Документы для внутренней и внешней общественности

Документы для внутренней и внешней общественности Исследовательская работа Картофель - второй хлеб

Исследовательская работа Картофель - второй хлеб