Содержание

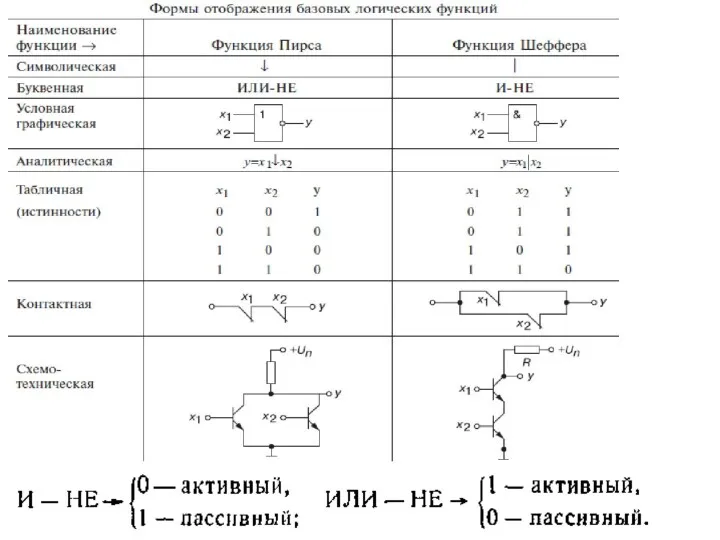

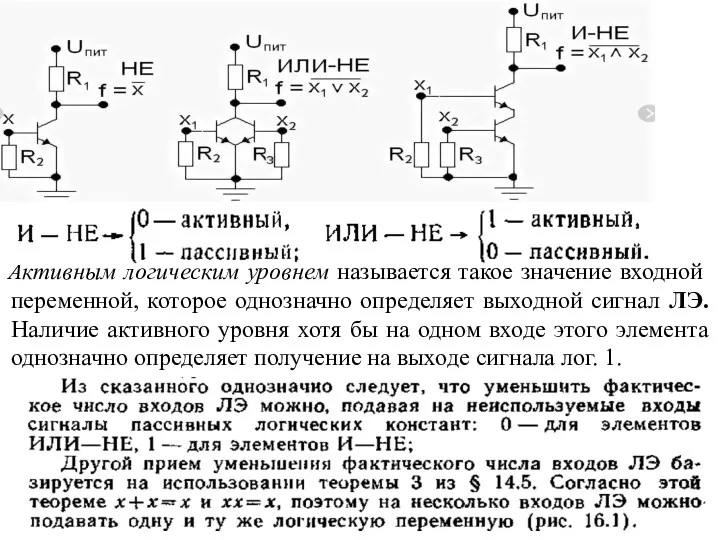

- 3. Активным логическим уровнем называется такое значение входной переменной, которое однозначно определяет выходной сигнал ЛЭ. Наличие активного

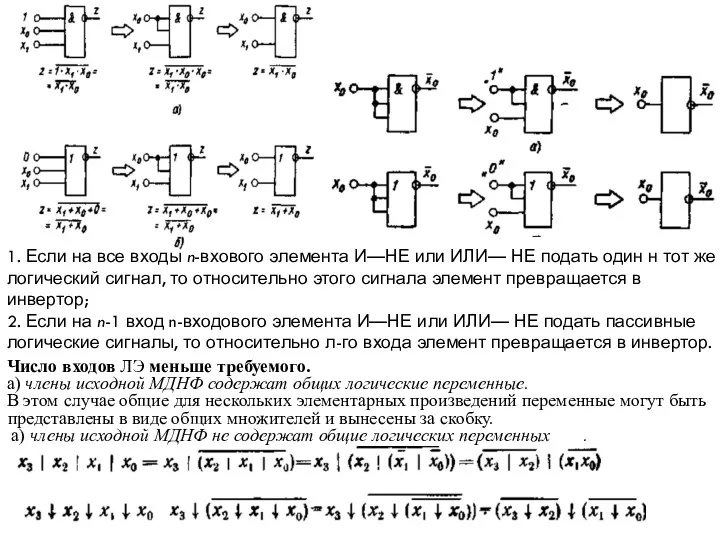

- 4. 1. Если на все входы n-вхового элемента И—НЕ или ИЛИ— НЕ подать один н тот же

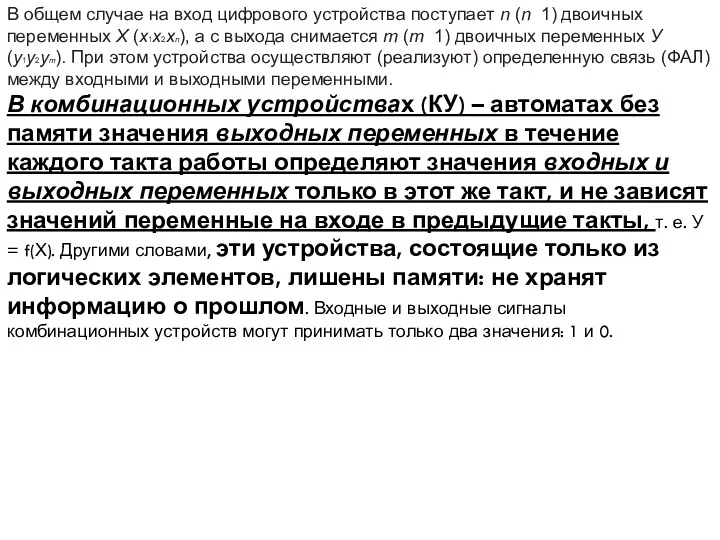

- 5. В общем случае на вход цифрового устройства поступает n (n 1) двоичных переменных Х (х1х2хп), а

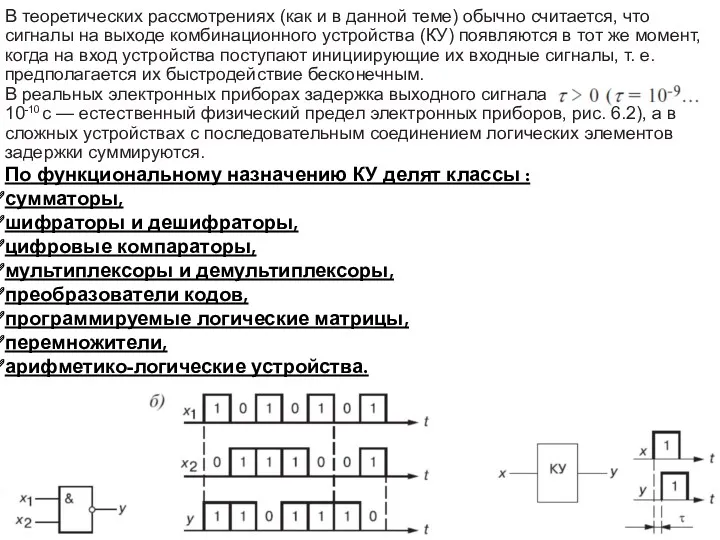

- 6. В теоретических рассмотрениях (как и в данной теме) обычно считается, что сигналы на выходе комбинационного устройства

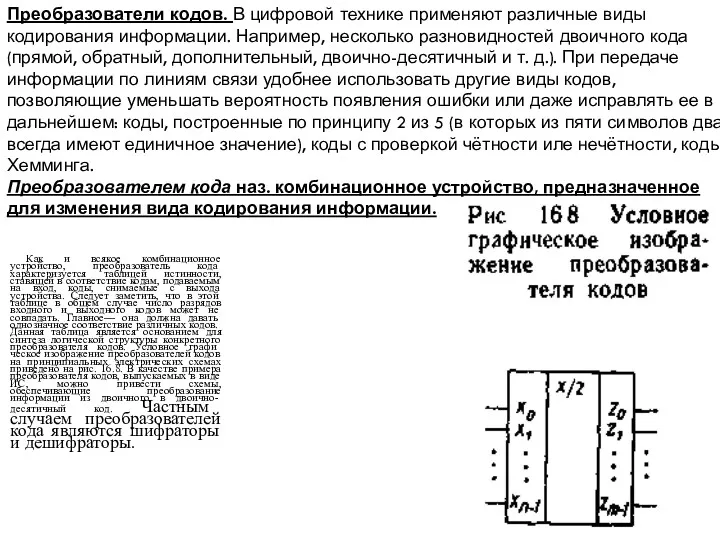

- 7. Преобразователи кодов. В цифровой технике применяют различные виды кодирования информации. Например, несколько разновидностей двоичного кода (прямой,

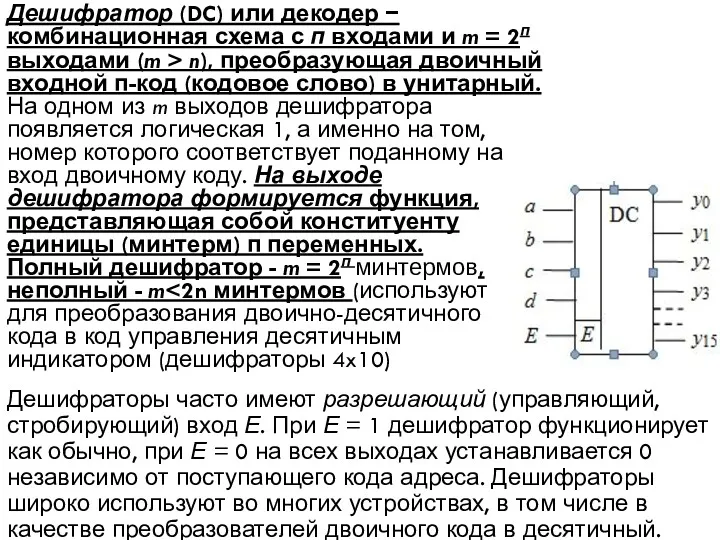

- 8. Дешифратор (DC) или декодер − комбинационная схема с п входами и m = 2п выходами (m

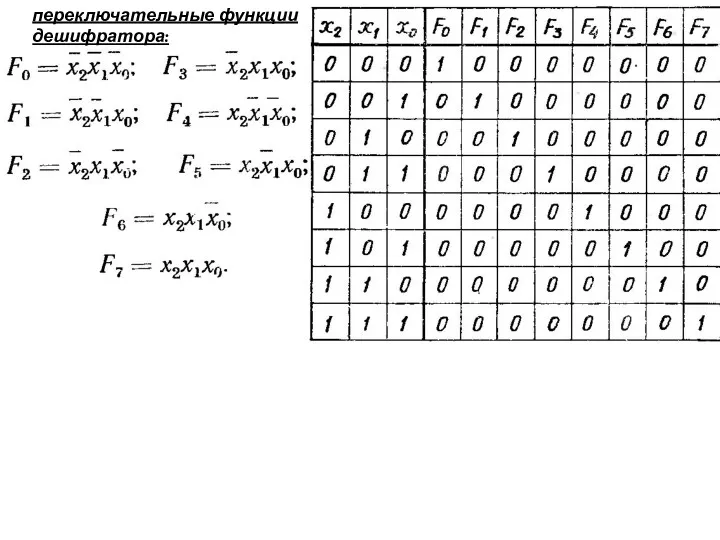

- 9. переключательные функции дешифратора:

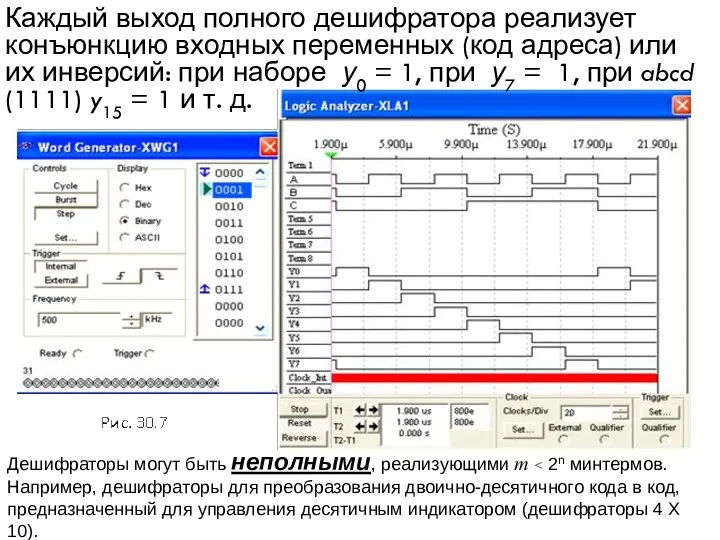

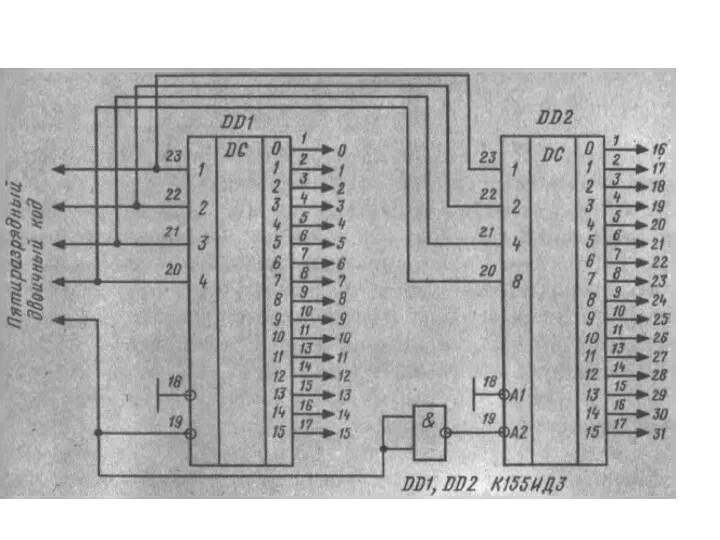

- 10. Каждый выход полного дешифратора реализует конъюнкцию входных переменных (код адреса) или их инверсий: при наборе у0

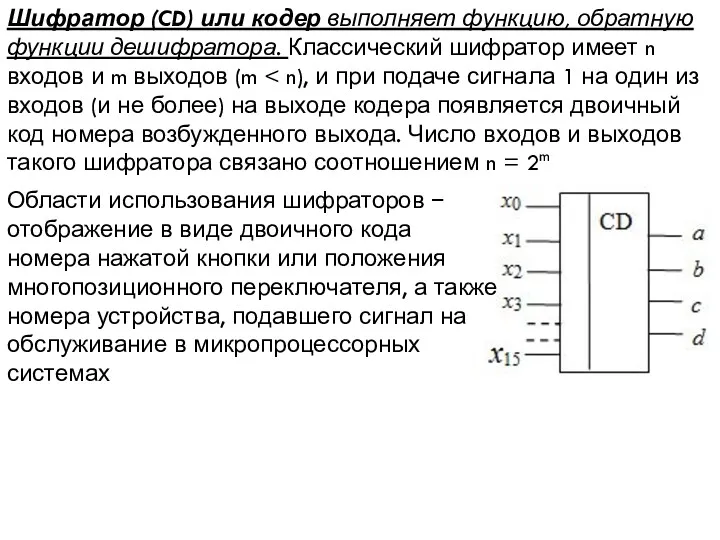

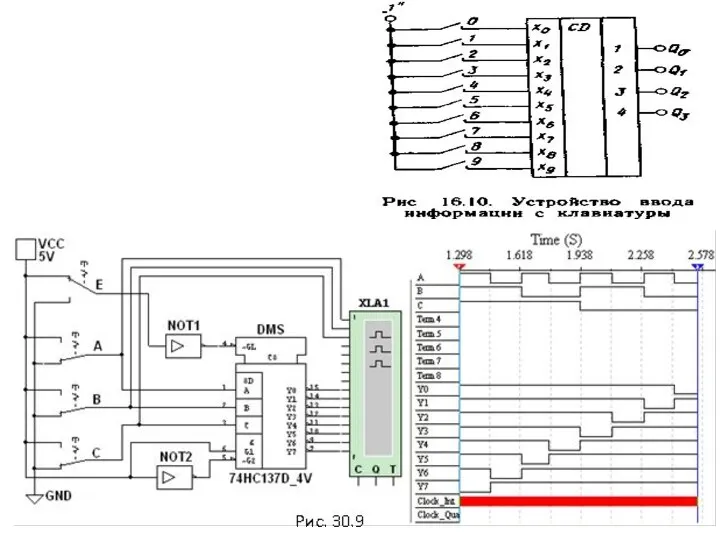

- 12. Шифратор (CD) или кодер выполняет функцию, обратную функции дешифратора. Классический шифратор имеет n входов и m

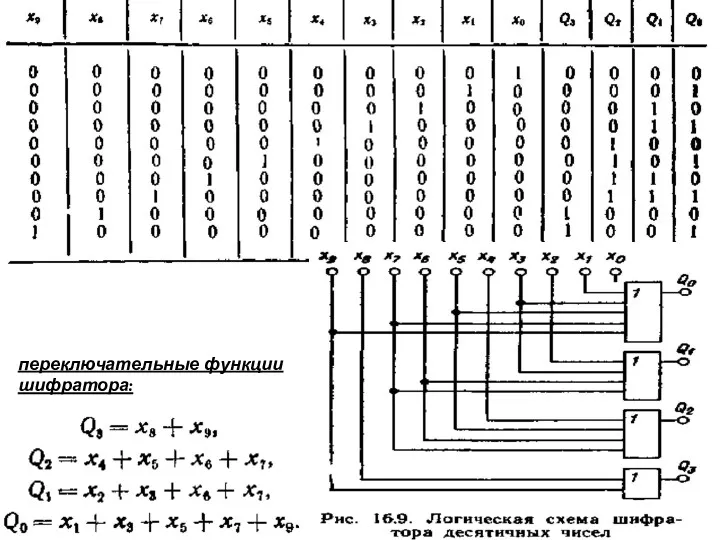

- 13. переключательные функции шифратора:

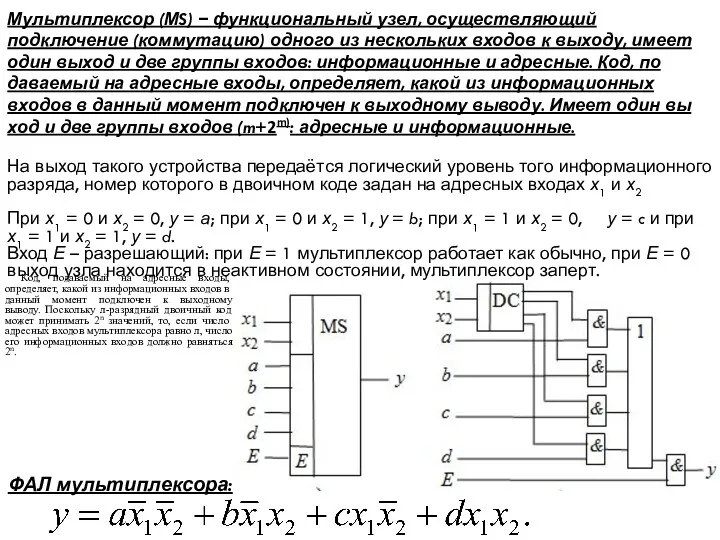

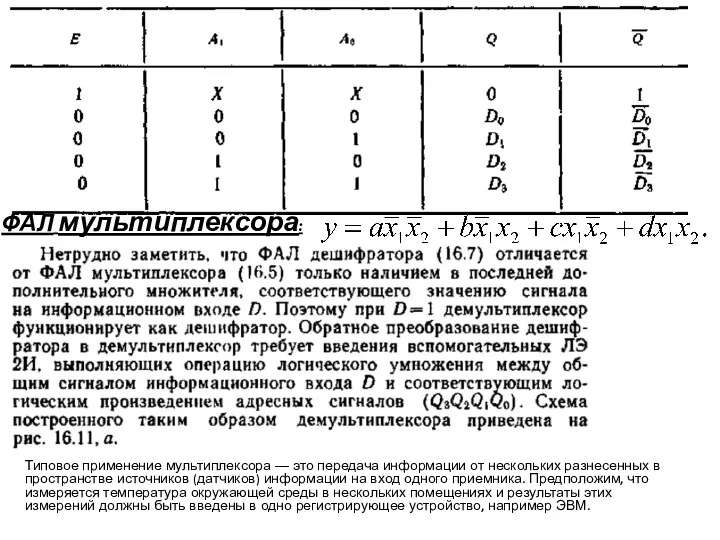

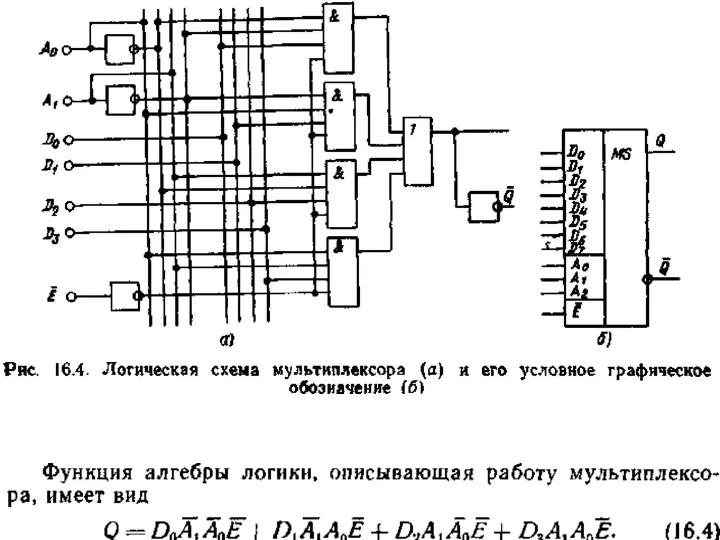

- 15. Мультиплексор (МS) − функциональный узел, осуществляющий подключение (коммутацию) одного из нескольких входов к выходу, имеет один

- 16. ФАЛ мультиплексора: Типовое применение мультиплексора — это передача информации от нескольких разнесенных в пространстве источников (датчиков)

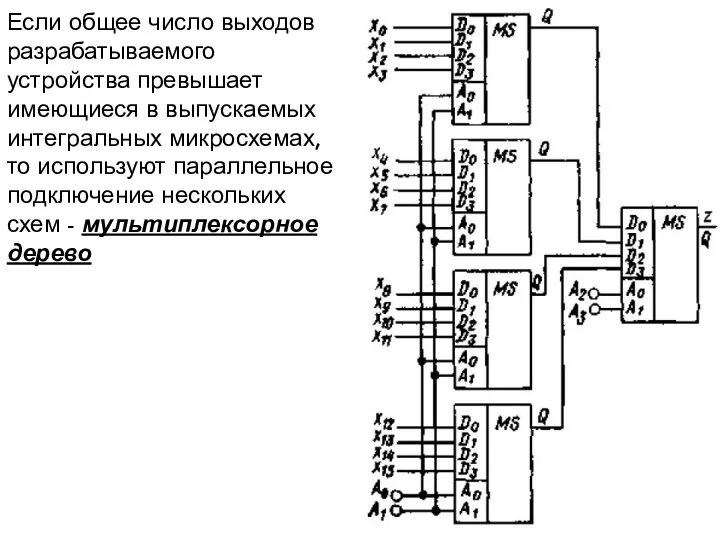

- 18. Если общее число выходов разрабатываемого устройства превышает имеющиеся в выпускаемых интегральных микросхемах, то используют параллельное подключение

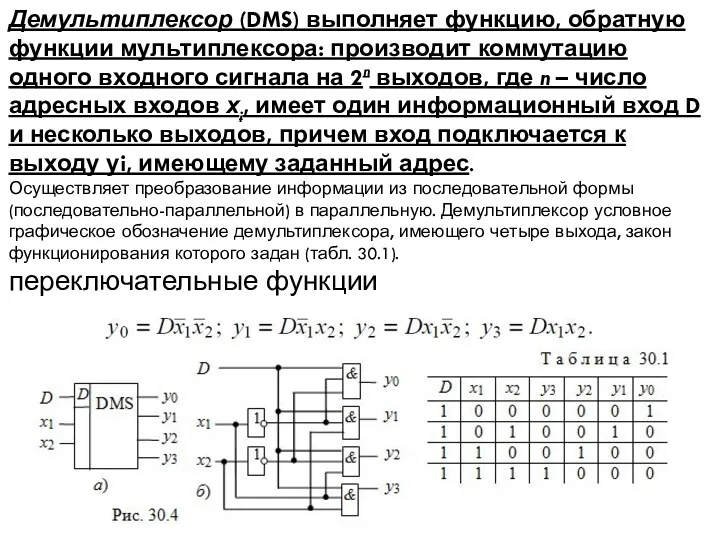

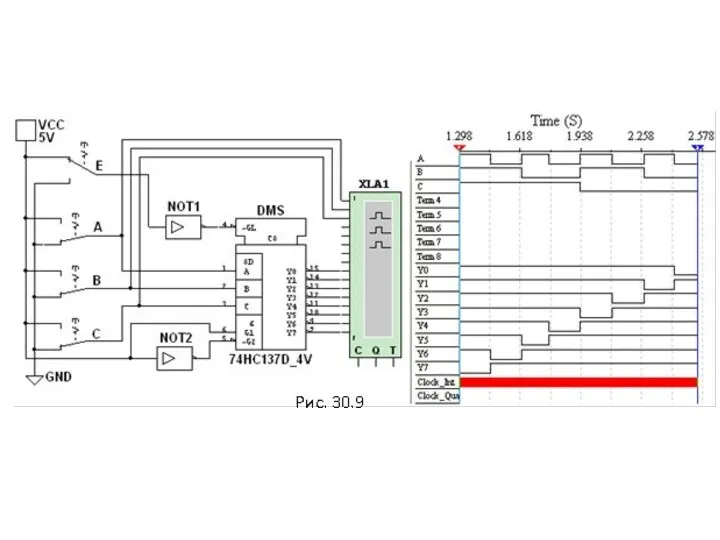

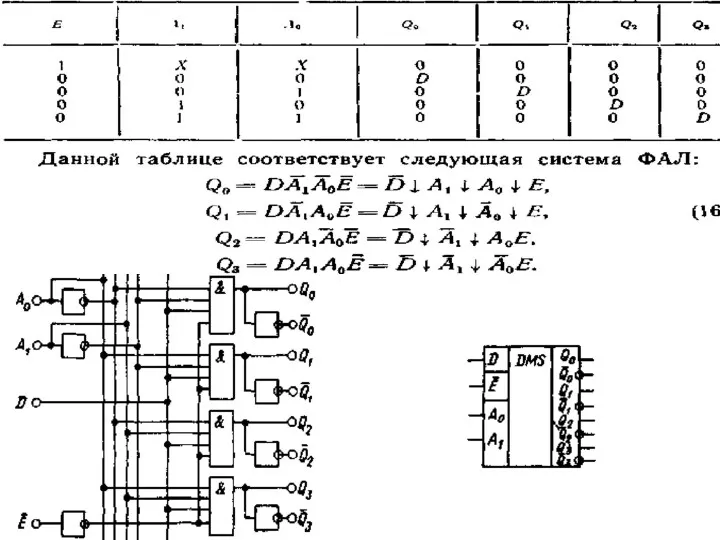

- 19. Демультиплексор (DMS) выполняет функцию, обратную функции мультиплексора: производит коммутацию одного входного сигнала на 2n выходов, где

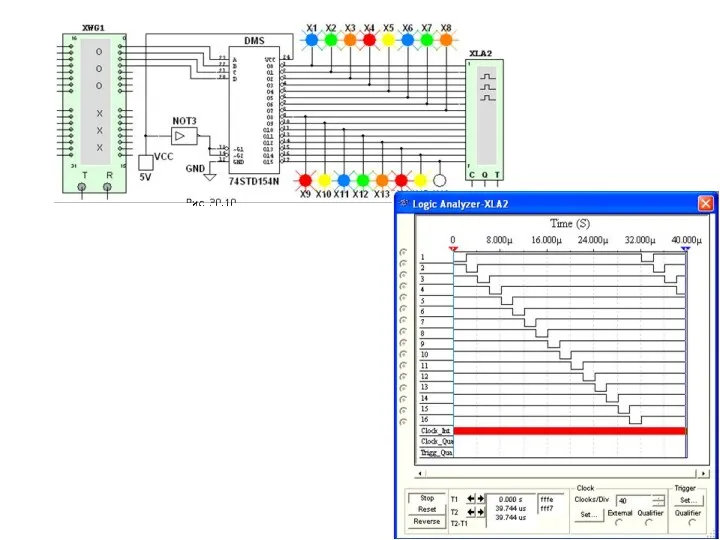

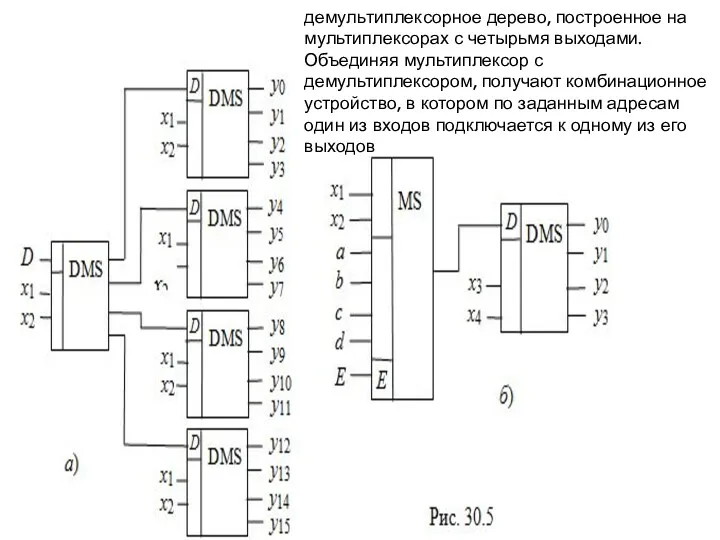

- 23. демультиплексорное дерево, построенное на мультиплексорах с четырьмя выходами. Объединяя мультиплексор с демультиплексором, получают комбинационное устройство, в

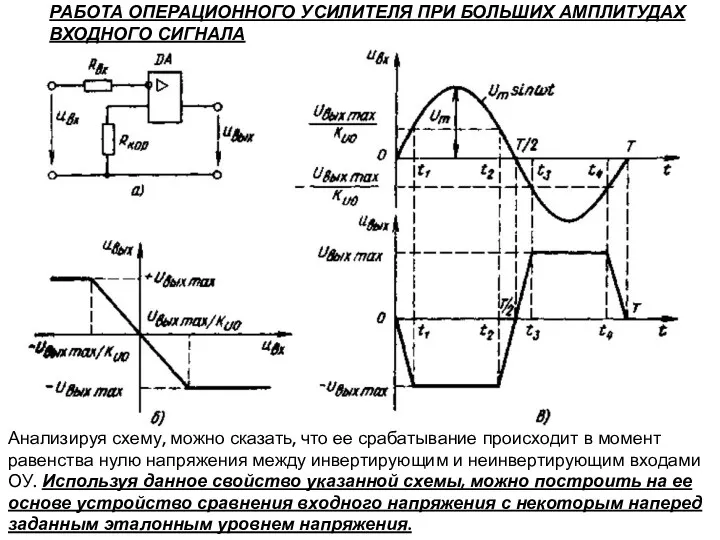

- 24. РАБОТА ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ПРИ БОЛЬШИХ АМПЛИТУДАХ ВХОДНОГО СИГНАЛА Анализируя схему, можно сказать, что ее срабатывание происходит

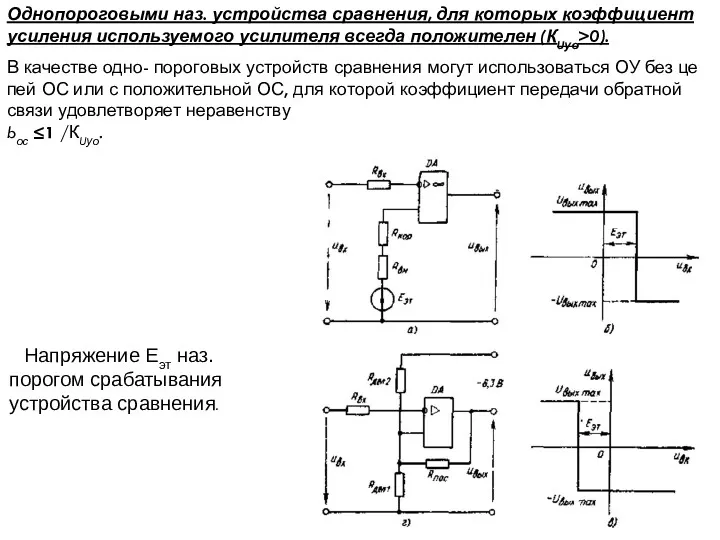

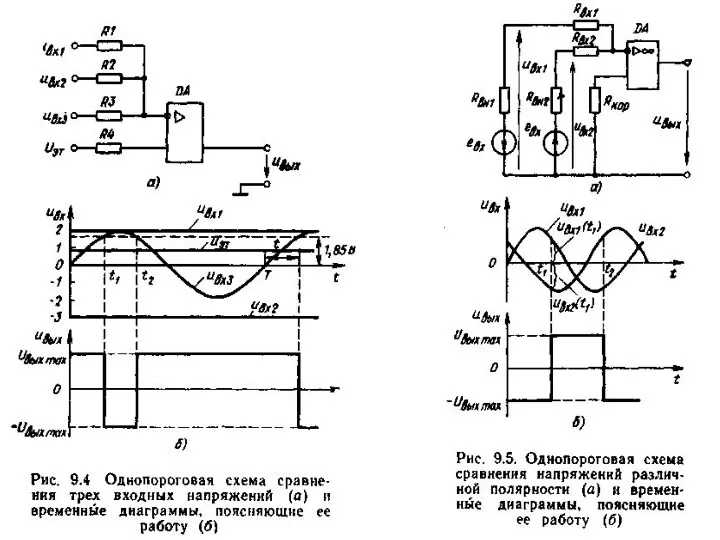

- 25. Однопороговыми наз. устройства сравнения, для которых коэффициент усиления используемого усилителя всегда положителен (КUуо>0). В качестве одно-

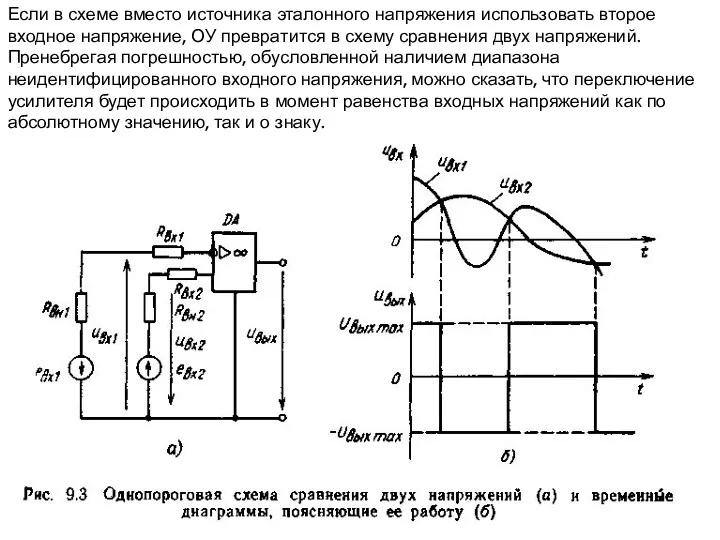

- 26. Если в схеме вместо источника эталонного напряжения использовать второе входное напряжение, ОУ превратится в схему сравнения

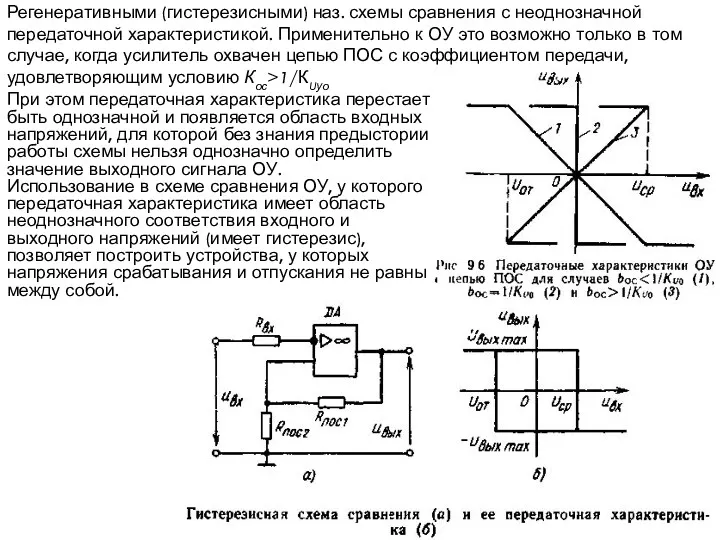

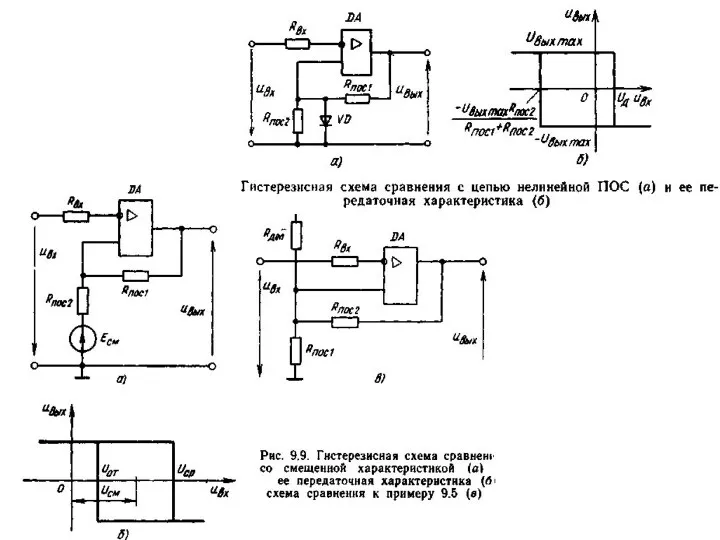

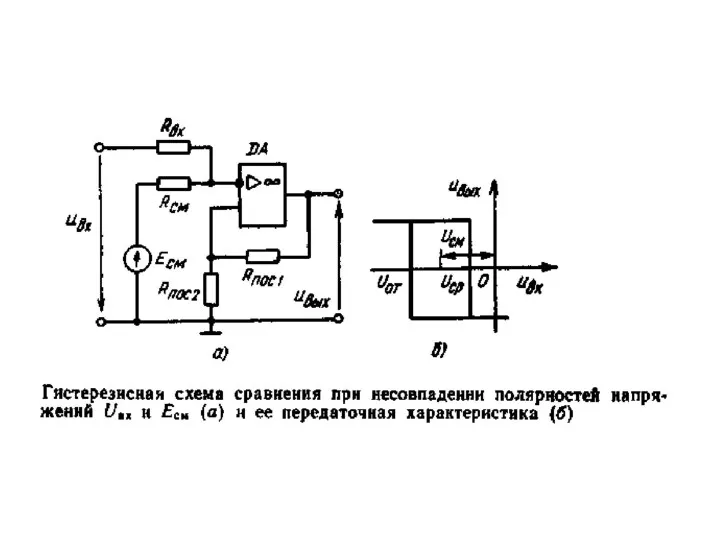

- 28. Регенеративными (гистерезисными) наз. схемы сравнения с неоднозначной передаточной характеристикой. Применительно к ОУ это возможно только в

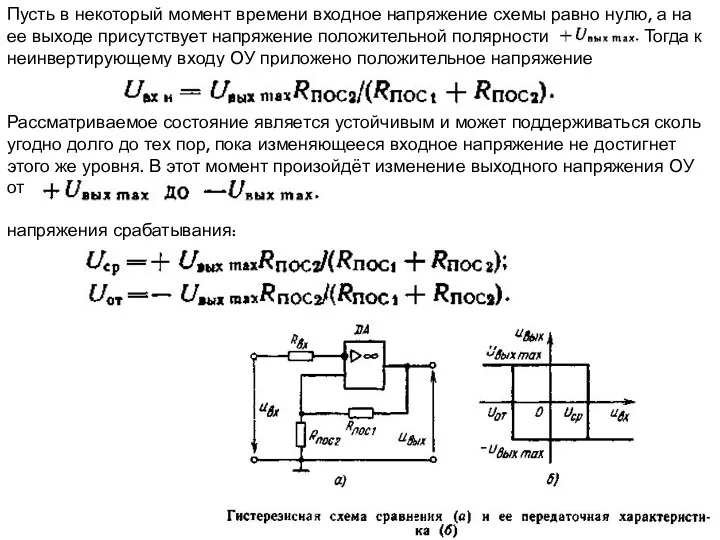

- 29. Пусть в некоторый момент времени входное напряжение схемы равно нулю, а на ее выходе присутствует напряжение

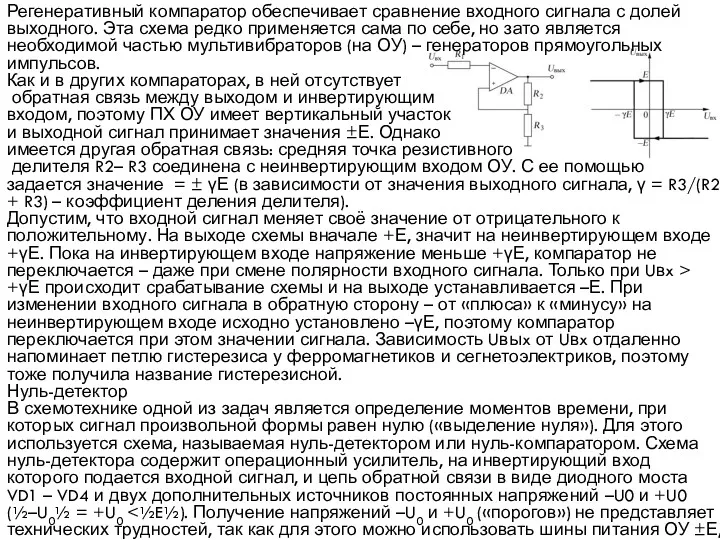

- 32. Регенеративный компаратор обеспечивает сравнение входного сигнала с долей выходного. Эта схема редко применяется сама по себе,

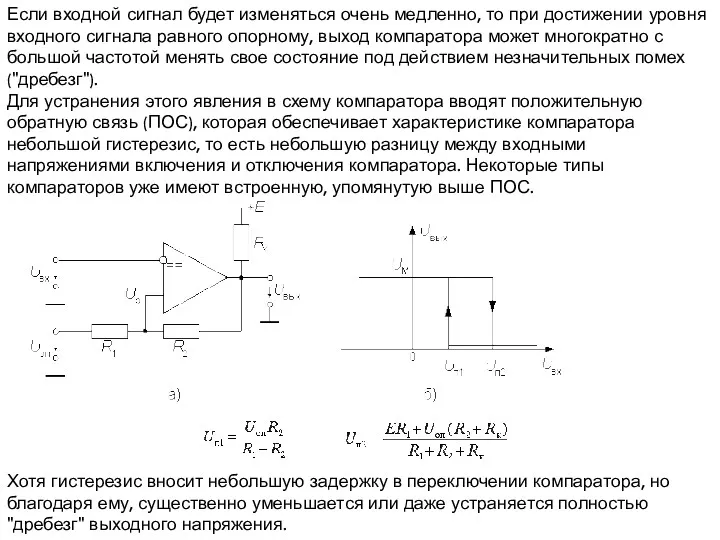

- 33. Если входной сигнал будет изменяться очень медленно, то при достижении уровня входного сигнала равного опорному, выход

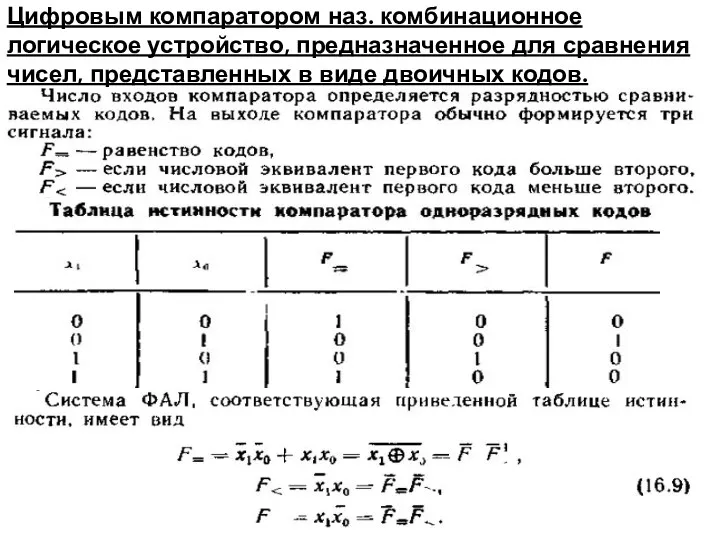

- 34. Цифровым компаратором наз. комбинационное логическое устройство, предназначенное для сравнения чисел, представленных в виде двоичных кодов.

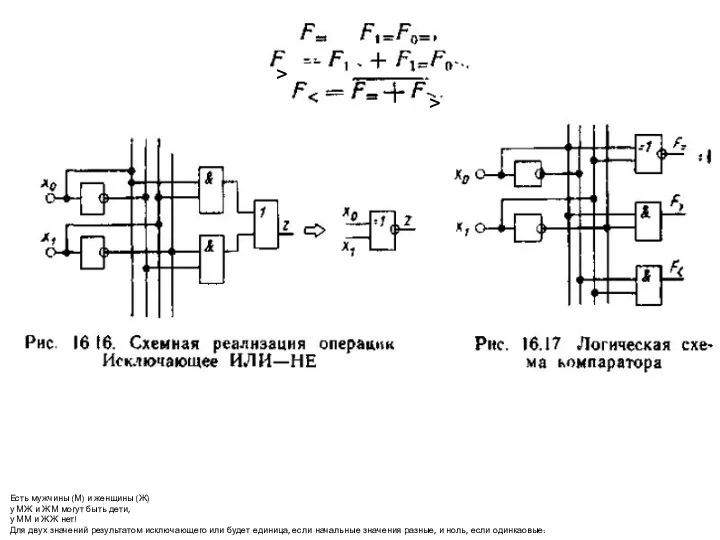

- 35. Есть мужчины (М) и женщины (Ж) у МЖ и ЖМ могут быть дети, у ММ и

- 36. Компараторы (устройства сравнения) определяют отношения между двумя словами. Основными отношениями, через которые можно выразить остальные, можно

- 37. Условное обозначение компаратора с тремя выходами

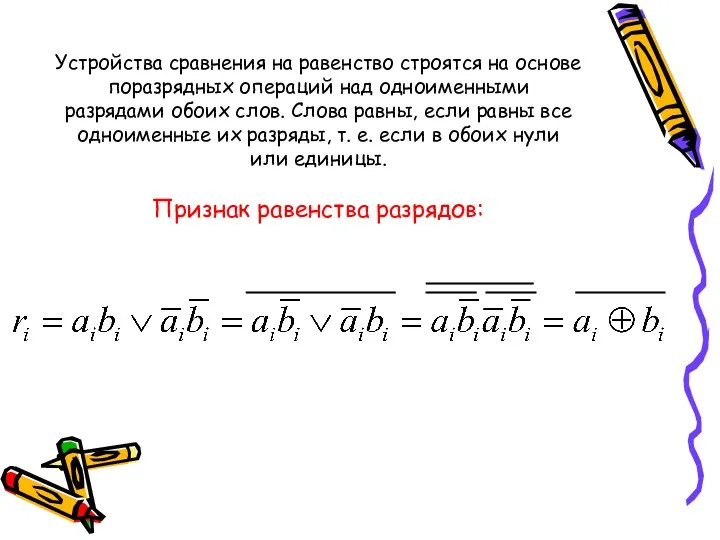

- 38. Устройства сравнения на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов. Слова равны,

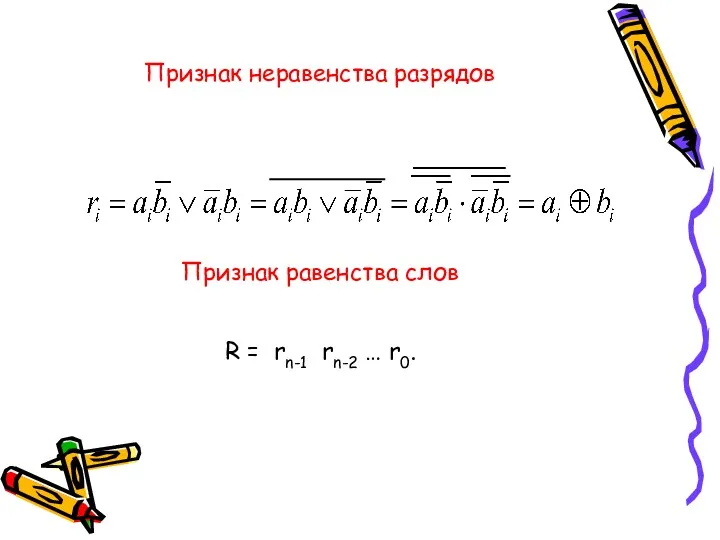

- 39. Признак неравенства разрядов Признак равенства слов R = rn-1 rn-2 … r0.

- 40. Рисунок 8.5 Схема компаратора на равенство в базисе И-НЕ Рисунок 8.6 Схема без парафазных входов Схема

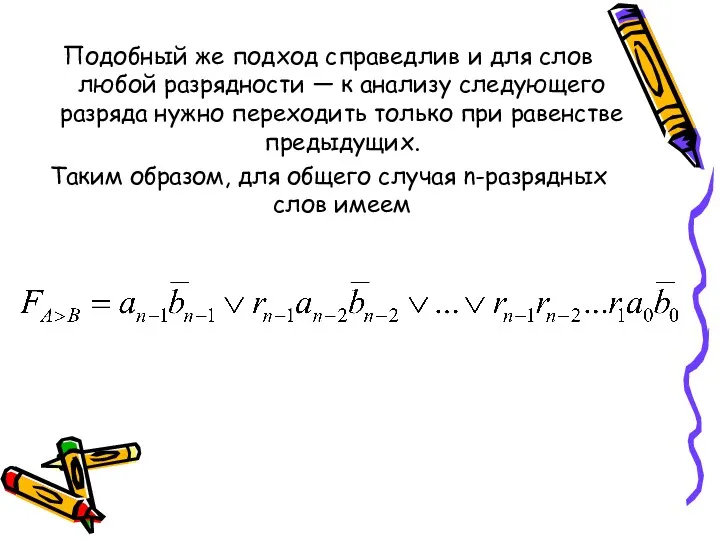

- 41. Подобный же подход справедлив и для слов любой разрядности — к анализу следующего разряда нужно переходить

- 42. Сумматоры и полусумматоры

- 43. Сумматоры Сумматор – устройство, осуществляющее операцию сложения двоичных кодов по правилам: 0+0 = 0, 0+1 =

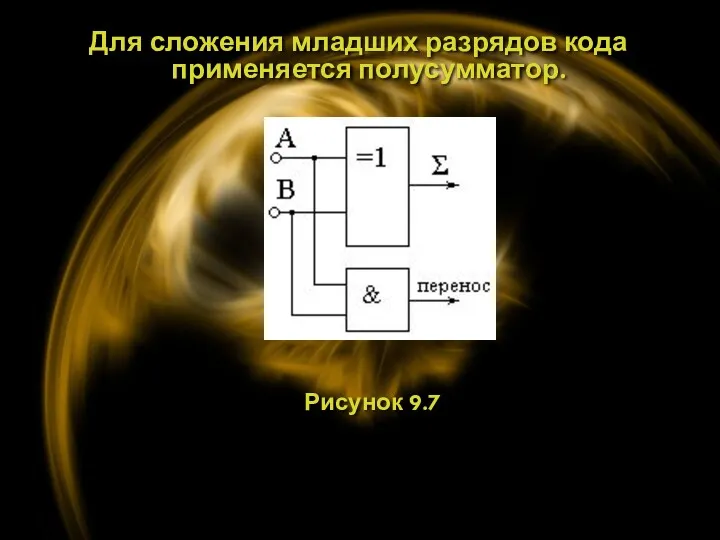

- 44. Для сложения младших разрядов кода применяется полусумматор. Рисунок 9.7

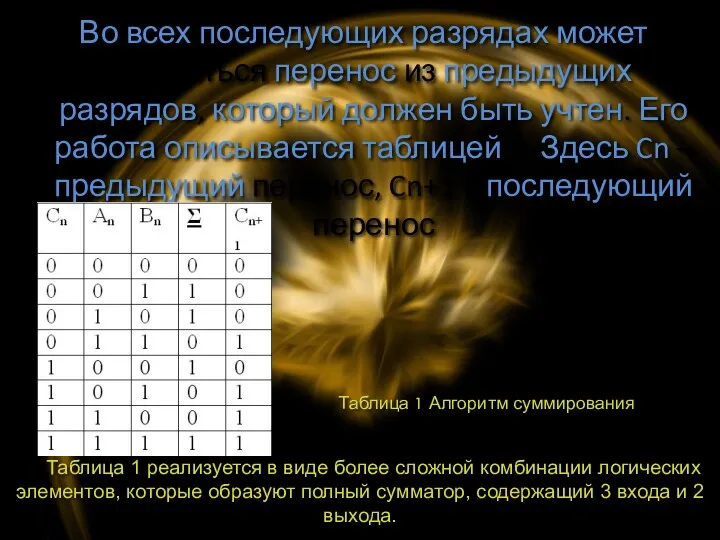

- 45. Во всех последующих разрядах может появиться перенос из предыдущих разрядов, который должен быть учтен. Его работа

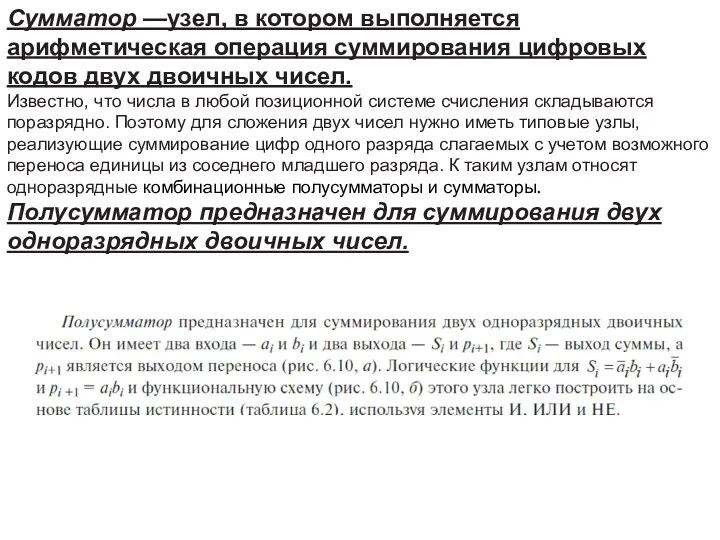

- 46. Сумматор —узел, в котором выполняется арифметическая операция суммирования цифровых кодов двух двоичных чисел. Известно, что числа

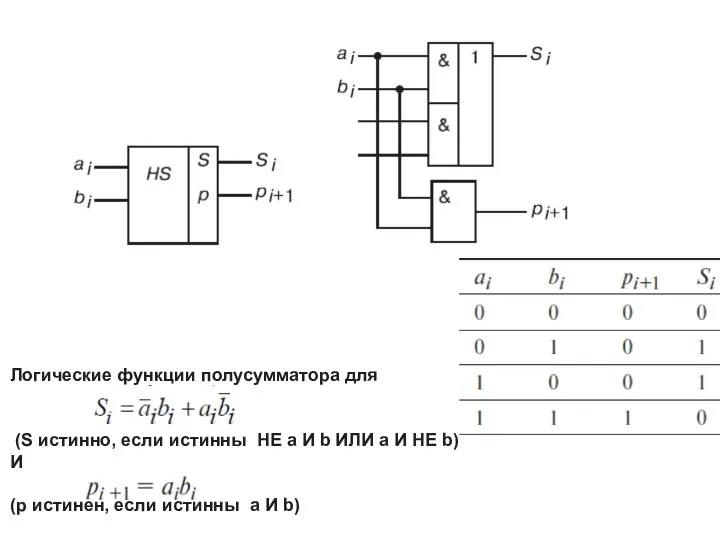

- 47. Логические функции полусумматора для (S истинно, если истинны НЕ a И b ИЛИ a И НЕ

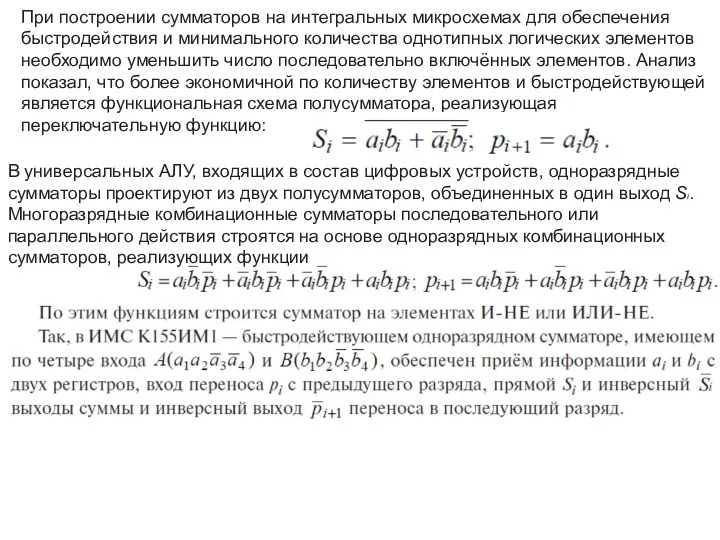

- 48. При построении сумматоров на интегральных микросхемах для обеспечения быстродействия и минимального количества однотипных логических элементов необходимо

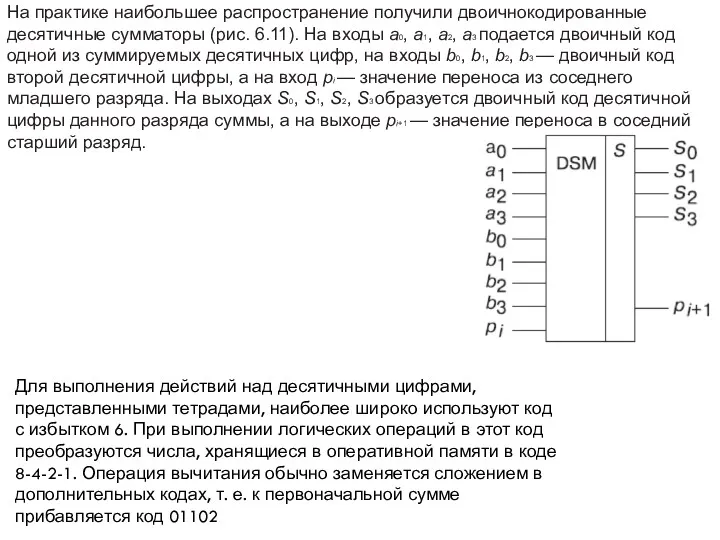

- 49. На практике наибольшее распространение получили двоичнокодированные десятичные сумматоры (рис. 6.11). На входы а0, а1, а2, а3

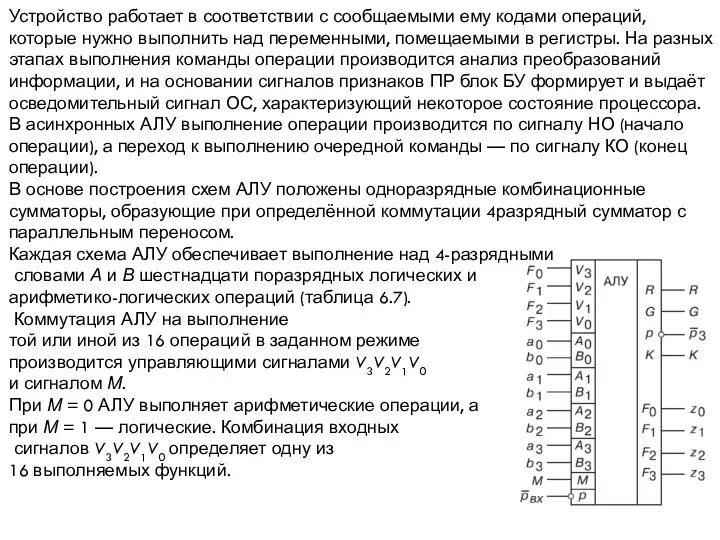

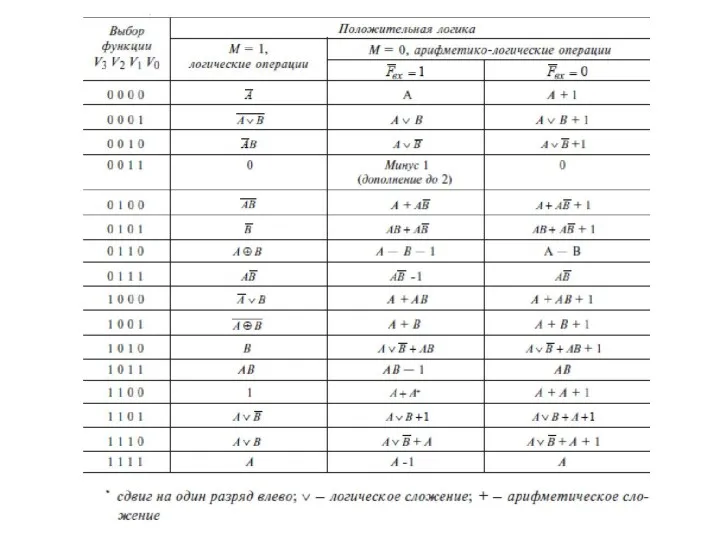

- 50. Арифметико-логическое устройство (АЛУ) — часть центрального процессора, формирующая функции двух входных переменных и порождающая одну выходную

- 51. По способу действия над операндами АЛУ подразделяют на параллельного и последовательного действия. По способу представления чисел

- 52. блок регистров БРег, предназначенный для приёма и размещения операндов и результата операции; блок арифметико-логических операций БАЛО,

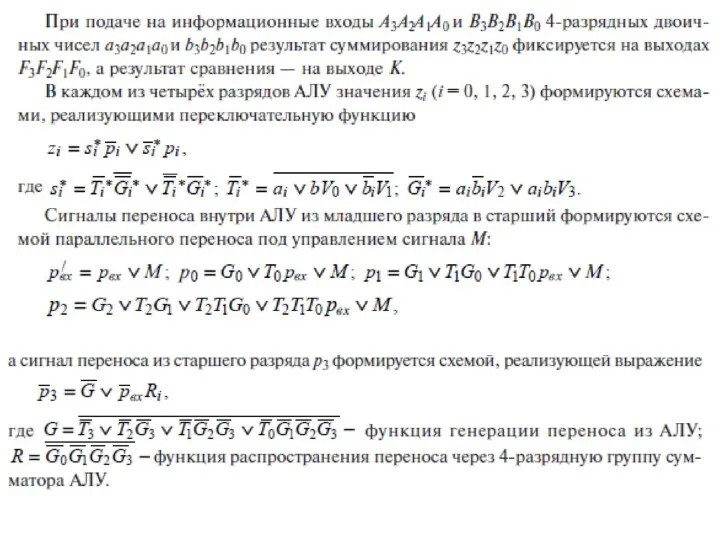

- 53. Устройство работает в соответствии с сообщаемыми ему кодами операций, которые нужно выполнить над переменными, помещаемыми в

- 58. Скачать презентацию

Кавказский биосферный заповедник

Кавказский биосферный заповедник Здания и сооружения. Основные конструктивные элементы зданий

Здания и сооружения. Основные конструктивные элементы зданий Петрофизика и геофизические исследования скважин (ГИС)

Петрофизика и геофизические исследования скважин (ГИС) Закрепление

Закрепление Совет депутатов городского поселения Раменское

Совет депутатов городского поселения Раменское Признаки равенства треугольников

Признаки равенства треугольников Строим загородный дом. Как уменьшить риски

Строим загородный дом. Как уменьшить риски Организация кормления высокопродуктивных коров в условиях ООО Агрофирма Заря Богородского района

Организация кормления высокопродуктивных коров в условиях ООО Агрофирма Заря Богородского района Аппаратное обеспечение ПК

Аппаратное обеспечение ПК Язык программирования Pascal

Язык программирования Pascal Многообразие и происхождение культурных растений

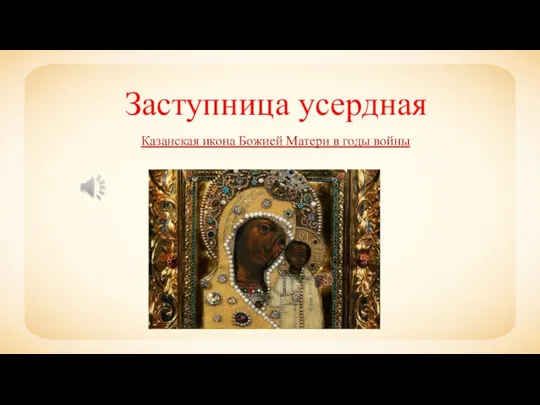

Многообразие и происхождение культурных растений Заступница усердная Казанская икона Божией Матери в годы войны

Заступница усердная Казанская икона Божией Матери в годы войны Самолёт АН-225 Мрия

Самолёт АН-225 Мрия Теорема косинусов

Теорема косинусов Экстренные оперативные службы обеспечения безопасности граждан. (Тема 2.4)

Экстренные оперативные службы обеспечения безопасности граждан. (Тема 2.4) Урок милосердия

Урок милосердия Создание 3D модели на основе операций твердотельного моделирования

Создание 3D модели на основе операций твердотельного моделирования Подготовка к работе по конструированию. Снятие мерок

Подготовка к работе по конструированию. Снятие мерок Природоохранная акция в ДОУ Знаки сделаем мы дружно и расставим там, где нужно, чтобы людям показать, как природу охранять

Природоохранная акция в ДОУ Знаки сделаем мы дружно и расставим там, где нужно, чтобы людям показать, как природу охранять День защиты детей

День защиты детей Электромагнитное реле

Электромагнитное реле Цветные металлы и сплавы на их основе

Цветные металлы и сплавы на их основе Заболевания кожи у детей и их профилактика

Заболевания кожи у детей и их профилактика Игра-презентация Веселое путешествие

Игра-презентация Веселое путешествие Главные заповеди родителей.

Главные заповеди родителей. XII Всероссийский медиафестиваль для детей, юношества и семьи - Моряна 2019

XII Всероссийский медиафестиваль для детей, юношества и семьи - Моряна 2019 Презентация Работа с планшетными компьютерами и электронными учебниками

Презентация Работа с планшетными компьютерами и электронными учебниками Структурно-функциональная организация дыхательной системы. Этапы дыхания. Регуляция дыхания

Структурно-функциональная организация дыхательной системы. Этапы дыхания. Регуляция дыхания