Содержание

- 2. Упрощённая структура микропроцессора

- 3. Структура микропроцессора

- 4. Арифметическо-логическое устройство состоит из: двоичного сумматора со схемами ускоренного переноса, сдвигающего регистра регистров для временного хранения

- 5. Структурная схема АЛУ

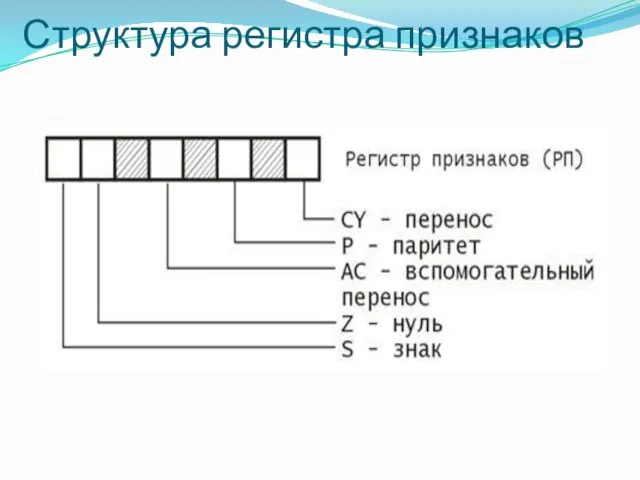

- 6. Структура регистра признаков

- 7. Устройство управления состоит из двух относительно независимых частей: первичного автомата, управляющего процессами внутри МП; схемы, обрабатывающей

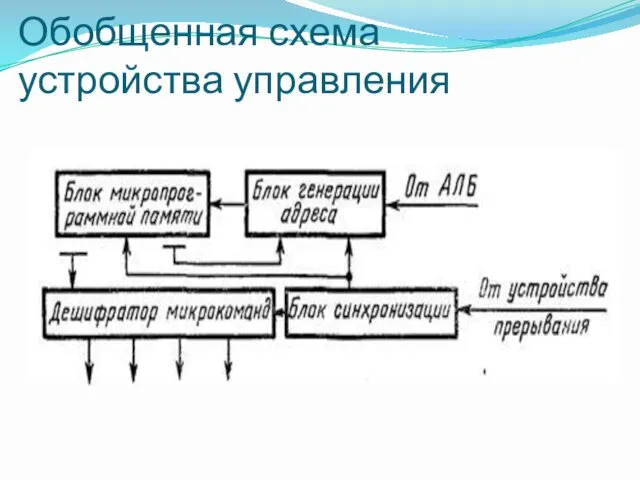

- 8. Обобщенная схема устройства управления

- 9. Блок внутренних регистров БВР расширяет возможности АЛУ, служит внутренней памятью МП и используется для временного хранения

- 10. Специальные регистры Регистр – аккумулятор (“накопитель”), предназначен для временного хранения операнда или промежуточного результата действий производимой

- 11. Регистры общего назначения Их функция – хранение операндов. Могут выполнять также и роль регистров Число может

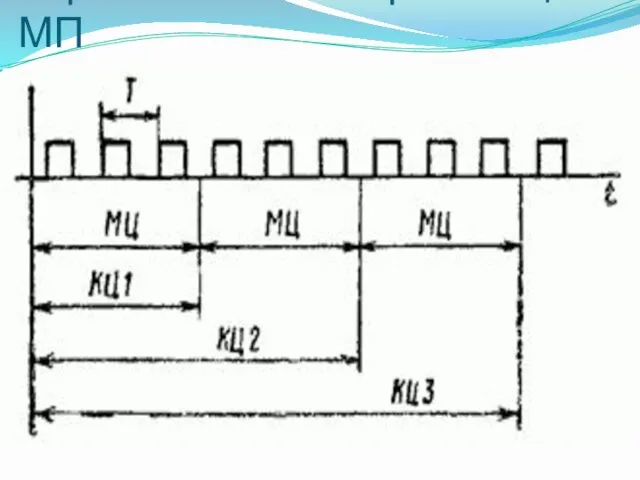

- 12. Управление и синхронизация МП Машинный такт (Т) — это период синхросигналов. Его длительность может быть установлена

- 13. Управление и синхронизация МП

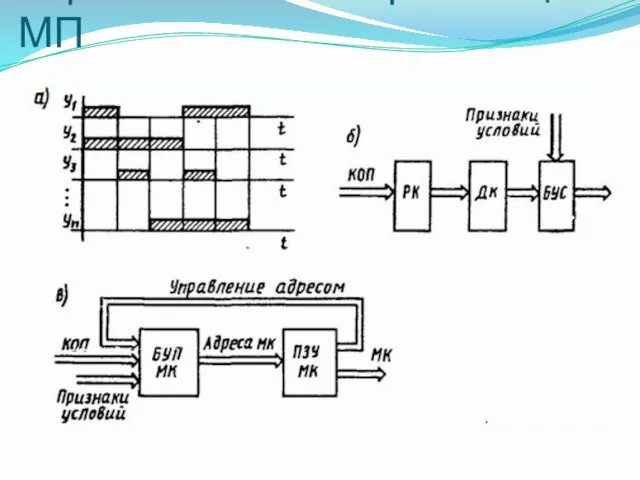

- 14. Управление и синхронизация МП Элементарную функциональную операцию (или их некоторую комбинацию), выполняемую за один тактовый интервал

- 15. Управление и синхронизация МП

- 16. Управление и синхронизация МП Схемный, жесткий или аппаратный способ управления используется в однокристальных МП. Он характеризуется

- 18. Скачать презентацию

Шаблон. Конкурс молодежных проектов

Шаблон. Конкурс молодежных проектов Создание СССР. Роль Ленина и Сталина,2 проекта: автономизация и федерация

Создание СССР. Роль Ленина и Сталина,2 проекта: автономизация и федерация Статистические таблицы и графики

Статистические таблицы и графики Деятельность Совета молодых специалистов медицинских организаций Республики Бурятия

Деятельность Совета молодых специалистов медицинских организаций Республики Бурятия Автоматизация биохимических исследований

Автоматизация биохимических исследований Профессиональный уход за кожей на дому

Профессиональный уход за кожей на дому Распределение четырех сил. Горизонтальный полет

Распределение четырех сил. Горизонтальный полет Зарубежная Азия 11 класс

Зарубежная Азия 11 класс Чей голос?

Чей голос? Система продаж дополнительных услуг в фитнес и велнес клубе

Система продаж дополнительных услуг в фитнес и велнес клубе Құландар. Отрядына жататын жабайы жылқы

Құландар. Отрядына жататын жабайы жылқы Электрические машины постоянного тока (продолжение)

Электрические машины постоянного тока (продолжение) Грибы-паразиты

Грибы-паразиты Буддизм

Буддизм Дифракция и интерференция волн

Дифракция и интерференция волн Автомобили для гоночной серии 3градуса-Спектурум

Автомобили для гоночной серии 3градуса-Спектурум Презентация по химии Витамины

Презентация по химии Витамины Проектная деятельность Я-исследователь

Проектная деятельность Я-исследователь Экскурсия для детей по детскому саду

Экскурсия для детей по детскому саду Ревматизм. Приобретенные пороки сердца

Ревматизм. Приобретенные пороки сердца Штамповка на высокоскоростных молотах

Штамповка на высокоскоростных молотах Система охлаждения ДВС

Система охлаждения ДВС Клетки и ткани человека

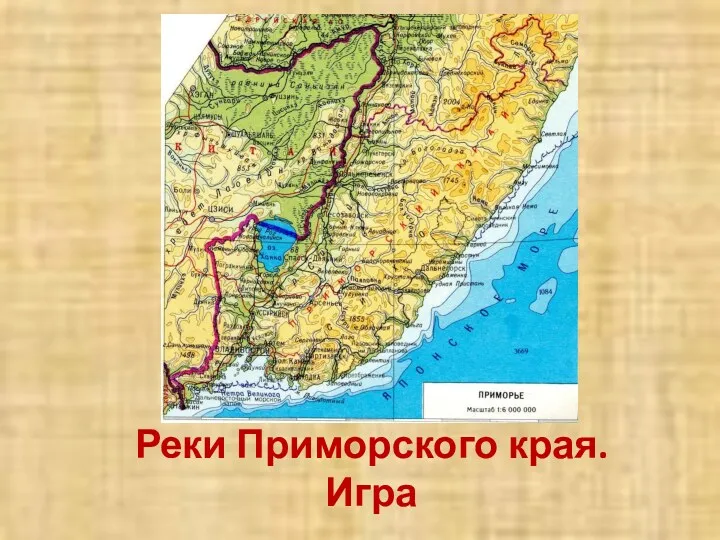

Клетки и ткани человека Реки Приморского края. Анимированная игра

Реки Приморского края. Анимированная игра Test turlari

Test turlari Правила техники безопасности в химической лаборатории

Правила техники безопасности в химической лаборатории Neural Networks

Neural Networks Психологическая служба МЧС России при оказании экстренной помощи пострадавшим (ЭПП) в режиме чрезвычайной ситуации

Психологическая служба МЧС России при оказании экстренной помощи пострадавшим (ЭПП) в режиме чрезвычайной ситуации