Содержание

- 2. Экономическая целесообразность использования микроконтроллеров STM32 Современный уровень развития технологии обеспечил возможность создания микроконтроллеров с 32- битной

- 3. Компания STMicroelectronics разрабатывала 32 -битные микроконтроллеры на основе ядер ARM7 и ARM9 Новое поколение 32- битных

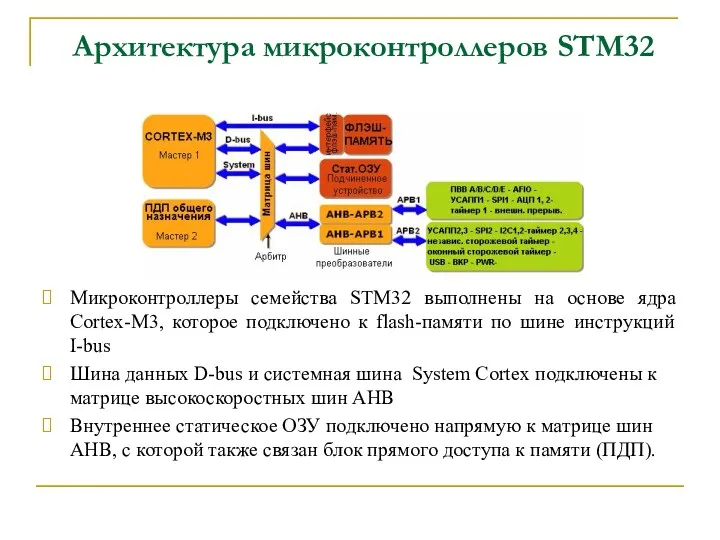

- 4. Архитектура микроконтроллеров STM32 Микроконтроллеры семейства STM32 выполнены на основе ядра Cortex-M3, которое подключено к flash-памяти по

- 5. Обзор платформы STM32 Микроконтроллеры STM32 изначально выпускались в 14 различных вариантах, разделенные на две группы: Performance

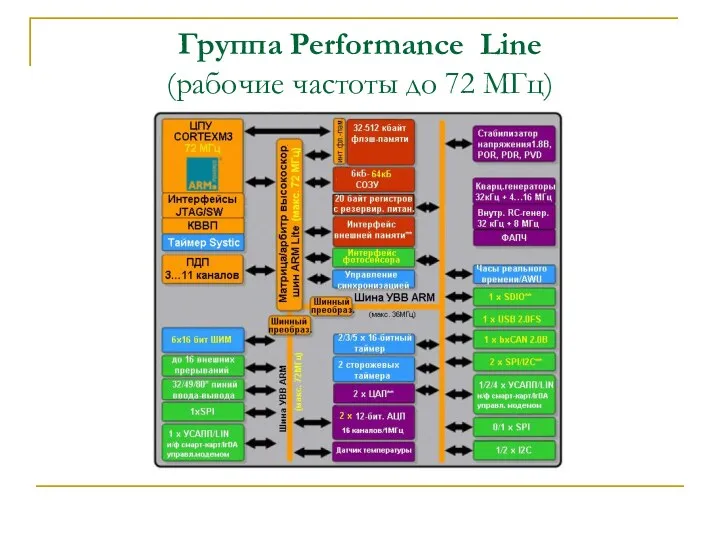

- 6. Группа Performance Line (рабочие частоты до 72 МГц)

- 7. Группа Aссess Line (тактовая частота до 36 МГц)

- 8. Микроконтроллеры работают от 2В-ого источника питания на тактовой частоте 72МГц и потребляют с учетом нахождения в

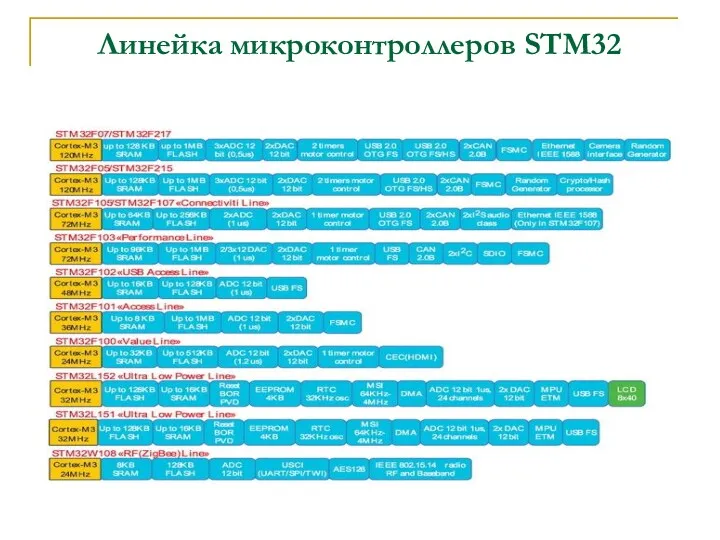

- 9. Линейка микроконтроллеров STM32

- 10. АРХИТЕКТУРА

- 11. NVIC – неотъемлемая часть процессора Cortex-M3. Модуль NVIC в процессоре Cortex-M3 осуществляет обработку прерываний аппаратными средствами.

- 12. Шинная матрица (Bus matrix) Шинная матрица — это развитие идеи простого контроллера шины: здесь шины соединены

- 13. Ядро Cortex-M3 Выполняет инструкции, производит вычисления в своём арифметико-логическом устройстве (АЛУ) Его Гарвардская архитектура позволяет одновременно

- 14. СИСТЕМНОЕ ПРОГРАММИРОВАНИЕ

- 15. Библиотека поддержки ядра Ядро ARM Cortex-M3 выходит за рамки обычного понятия ядра микроконтроллера и представляет собой

- 16. Структура CMSIS CMSIS состоит из трех файлов: core_m3.h - вспомогательные функции доступа к регистрам ядра; startup_stm32f10x_xx.s

- 17. Стандартная библиотека STM32 Стандартная библиотека для работы с периферийными модулями написана в соответствии со стандартом ANSI

- 18. Модификация библиотек Библиотека содержит три файла, доступные для модификации пользователем: файл конфигурации библиотеки stm32f10x_conf.h файлы обработчиков

- 19. ПРОГРАММНО-ИНСТРУМЕНТАЛЬНАЯ СРЕДА

- 20. Выбор программного инструментария под ARM-архитектуру

- 21. ОСВОЕНИЕ ПЛАТФОРМЫ

- 22. Отладочная плата STM32VLDiscovery Плата реализована на микроконтроллере линейки «Value Line» STM32F100RBT6 Имеет программатор-отладчик ST-Link с выведенным

- 24. Скачать презентацию

Теоретическая грамматика английского языка

Теоретическая грамматика английского языка Игра Собери портфель

Игра Собери портфель Сеть фитнес клубов My Fit

Сеть фитнес клубов My Fit Общие сведения о радиоматериалах

Общие сведения о радиоматериалах Организация профессиональной деятельности повара с разработкой технологии приготовления и оформления блюда утка фаршированная

Организация профессиональной деятельности повара с разработкой технологии приготовления и оформления блюда утка фаршированная Сенім дегеніміз не? Евр 11:1-2

Сенім дегеніміз не? Евр 11:1-2 презентация проекта Большая книга сказок

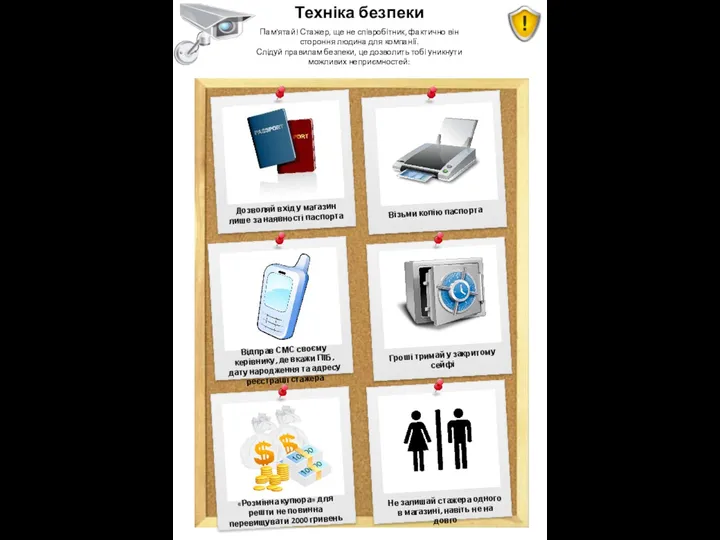

презентация проекта Большая книга сказок Программа обучения стажера

Программа обучения стажера Внеклассное мероприятие В гостях у сказки

Внеклассное мероприятие В гостях у сказки Сложные эфиры. Жиры. Мыла

Сложные эфиры. Жиры. Мыла HAICTC el planeta es para nuestros hijos. BIOMASA primera fuente de energías renovables

HAICTC el planeta es para nuestros hijos. BIOMASA primera fuente de energías renovables воспитательный час счастлив тот, кто счастлив у себя дома

воспитательный час счастлив тот, кто счастлив у себя дома Проектирование участков цехов ДСтП

Проектирование участков цехов ДСтП Электр жетектердегі өтпелі процестер

Электр жетектердегі өтпелі процестер Русский народный праздник Ефремов день

Русский народный праздник Ефремов день Часть речи существительное

Часть речи существительное Безработица, её причины и последствия

Безработица, её причины и последствия Презентация НИР

Презентация НИР Презентация по теме Предельные углеводороды 10 класс УМК О.С.Габриелян

Презентация по теме Предельные углеводороды 10 класс УМК О.С.Габриелян Дидактическая игра Что лишнее?

Дидактическая игра Что лишнее? Презентация к методической разработке: Покормите птиц зимой

Презентация к методической разработке: Покормите птиц зимой Презентация к уроку Бабочка (бисер)

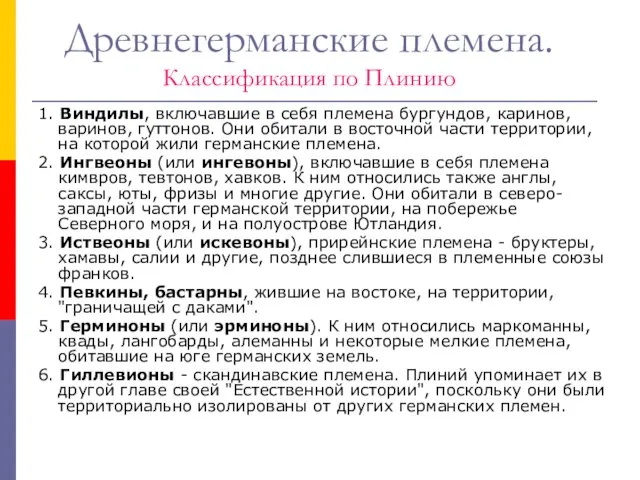

Презентация к уроку Бабочка (бисер) Древнегерманские племена. Классификация по Плинию

Древнегерманские племена. Классификация по Плинию Tele2 зажигает свет мобильных перемен

Tele2 зажигает свет мобильных перемен Vspomogatelnoe_oborudovanie_teplovoza

Vspomogatelnoe_oborudovanie_teplovoza Проектная деятельность, как средство реализации ФГОС

Проектная деятельность, как средство реализации ФГОС Психологические особенности подросткового возраста и роль родительских установок на формирование личности.

Психологические особенности подросткового возраста и роль родительских установок на формирование личности. La France. Французский язык

La France. Французский язык