Содержание

- 2. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. ОСНОВНЫЕ ПОНЯТИЯ, ХАРАКТЕРИСТИКА И КЛАССИФИКАЦИЯ ЗУ Запоминающие устройства

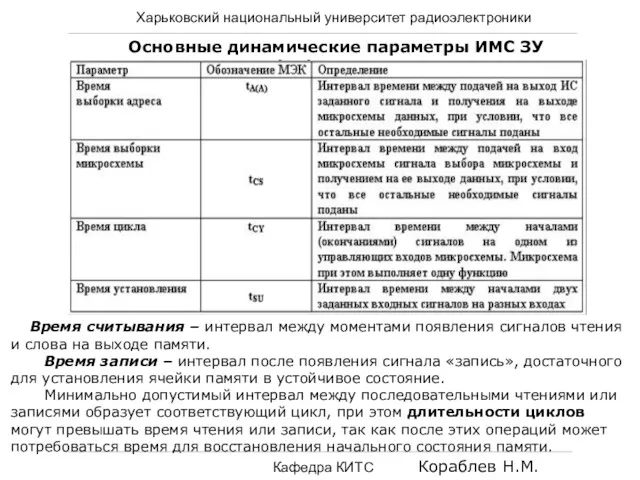

- 3. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Основные динамические параметры ИМС ЗУ Время считывания –

- 4. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Концепция многоуровневой памяти Важнейшие параметры ЗУ находятся в

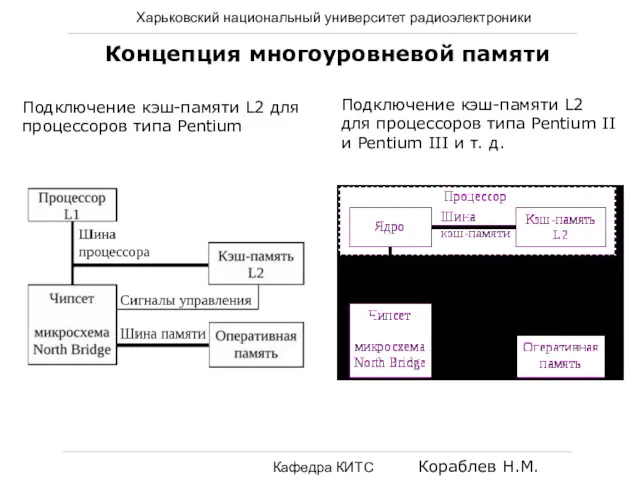

- 5. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Подключение кэш-памяти L2 для процессоров типа Pentium II

- 6. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Концепция многоуровневой памяти По мере продвижения по структуре

- 7. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Классификация ЗУ

- 8. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Классификация ЗУ Важным признаком классификации памяти является доступ

- 9. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Классификация ЗУ По логике организации DRAM-память может быть

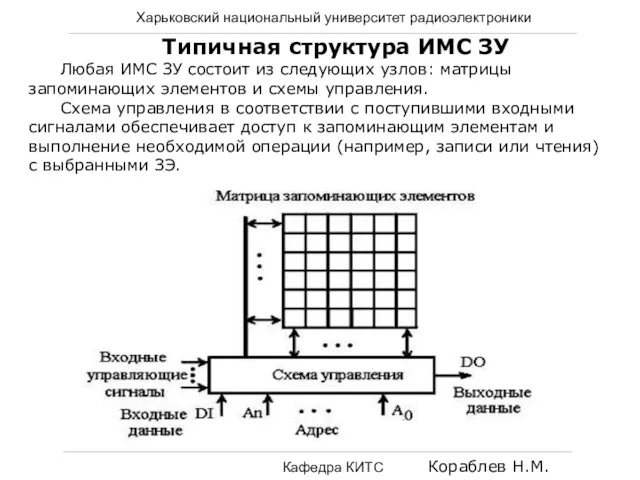

- 10. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Типичная структура ИМС ЗУ Любая ИМС ЗУ состоит

- 11. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Виды ROM ROM (однократно программируемая память изготовителем), PROM

- 12. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. ОСНОВНЫЕ СТРУКТУРЫ АДРЕСНЫХ ЗУ Адресные ЗУ представлены статическими

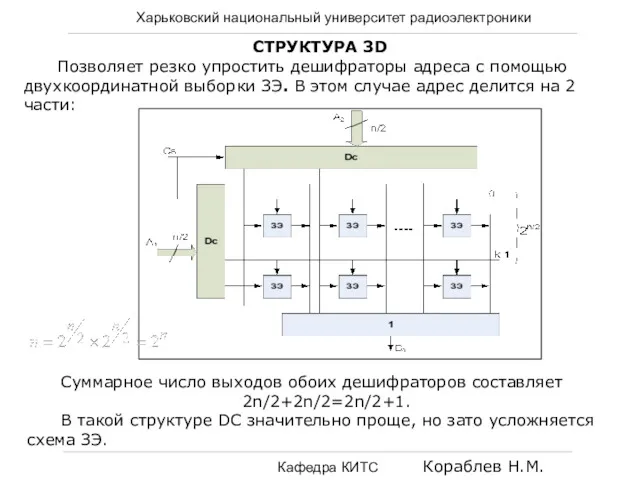

- 13. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. СТРУКТУРА 3D Позволяет резко упростить дешифраторы адреса с

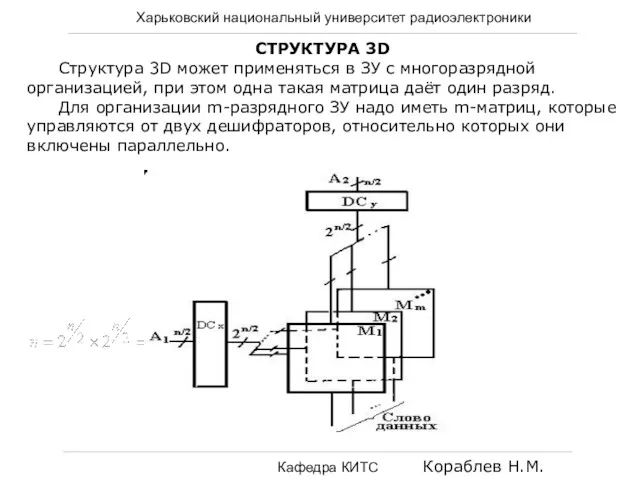

- 14. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. СТРУКТУРА 3D Структура 3D может применяться в ЗУ

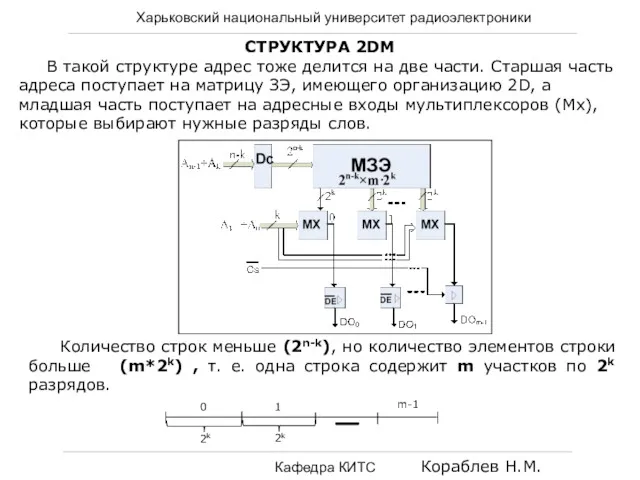

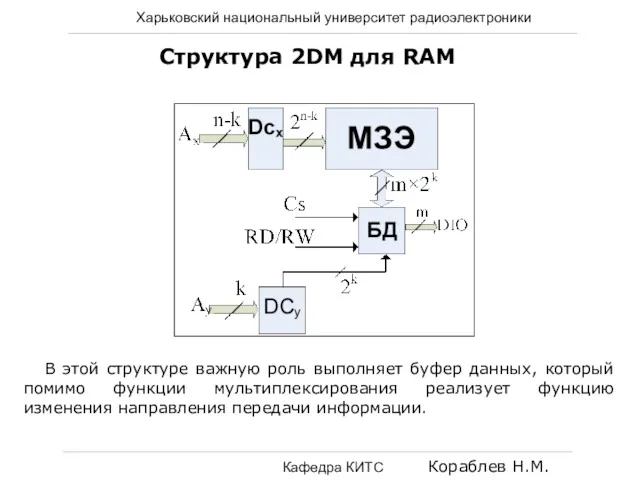

- 15. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. СТРУКТУРА 2DM В такой структуре адрес тоже делится

- 16. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Cтруктура 2DM для RAM В этой структуре важную

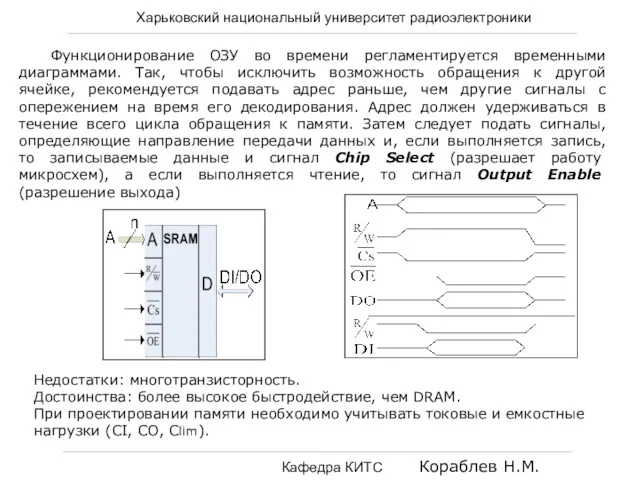

- 17. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. СТАТИЧЕСКИЕ ОЗУ (SRAM) Статические запоминающие устройства имеют структуру

- 18. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Функционирование ОЗУ во времени регламентируется временными диаграммами. Так,

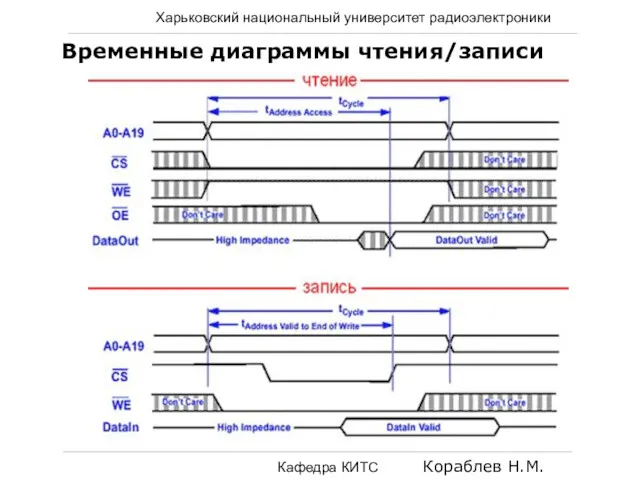

- 19. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Временные диаграммы чтения/записи

- 20. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Устройство типовой микросхемы SRAM-памяти

- 22. Скачать презентацию

Дом. Мебель

Дом. Мебель Диагностика и лечение синкопальных состояний

Диагностика и лечение синкопальных состояний Часть речи глагол. Повторение

Часть речи глагол. Повторение Подготовка к ГИА (часть В). Умение оценивать количественные параметры информационных объектов

Подготовка к ГИА (часть В). Умение оценивать количественные параметры информационных объектов Обеспечение целостности БД

Обеспечение целостности БД Food

Food Источники энергии и пути ее превращений в организме

Источники энергии и пути ее превращений в организме презентация на тему Древнерусская литература

презентация на тему Древнерусская литература Этапы ухода за кожей

Этапы ухода за кожей НОД Познание -Писатели детям

НОД Познание -Писатели детям Фотоальбом дефектов сварных соединений по визуальному и измерительному контролю

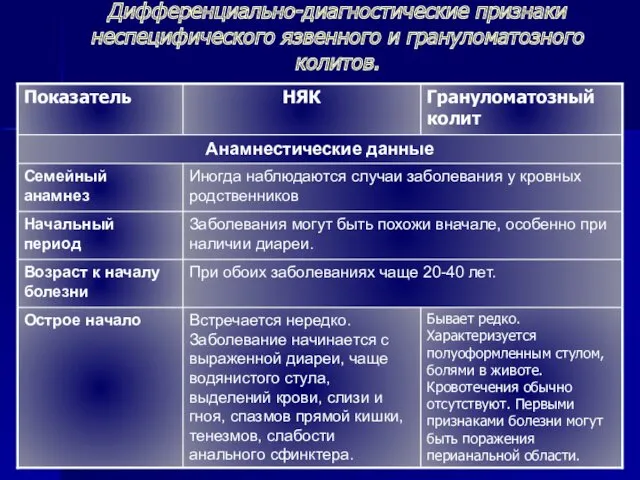

Фотоальбом дефектов сварных соединений по визуальному и измерительному контролю Дифференциально-диагностические признаки неспецифического язвенного и грануломатозного колитов

Дифференциально-диагностические признаки неспецифического язвенного и грануломатозного колитов Брендинг

Брендинг Клеточная теория. Типы клеточной организации

Клеточная теория. Типы клеточной организации Презентация Теоретический семинар Подготовка обучающихся к участию в олимпиадах

Презентация Теоретический семинар Подготовка обучающихся к участию в олимпиадах Технологии бурения наклонно-направленных скважин

Технологии бурения наклонно-направленных скважин Факторы стратификации в современной России

Факторы стратификации в современной России Первый член Символа веры. Вера

Первый член Символа веры. Вера Бурятская сказка

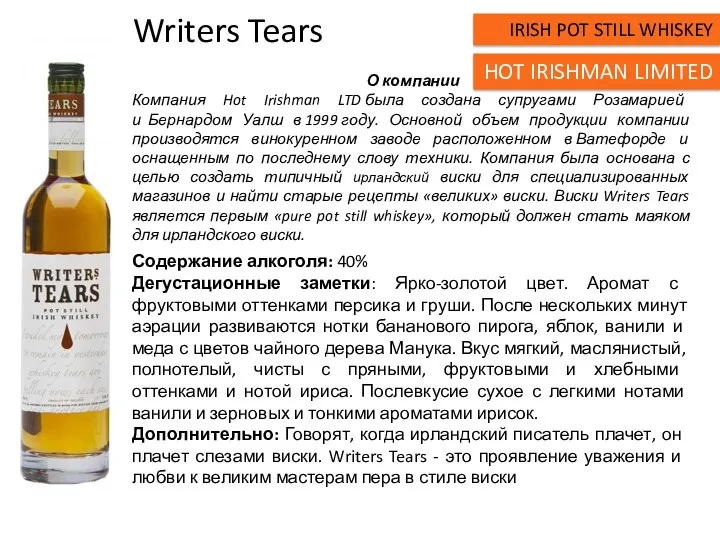

Бурятская сказка Крепкий алкоголь

Крепкий алкоголь Skanners & printers

Skanners & printers Презентация За избирателем-будущее России!

Презентация За избирателем-будущее России! Б.Ф. Шахов нима коми культура шӧрин

Б.Ф. Шахов нима коми культура шӧрин Объект, предмет, функции и принципы педагогики досуга

Объект, предмет, функции и принципы педагогики досуга презентация Болотов-педагог

презентация Болотов-педагог Наука о природе лесных пожаров и их последствий

Наука о природе лесных пожаров и их последствий О поощрении и наказании

О поощрении и наказании Опытно-эксперементальная деятельность по теме: Вода

Опытно-эксперементальная деятельность по теме: Вода