Содержание

- 2. Уровни абстракции

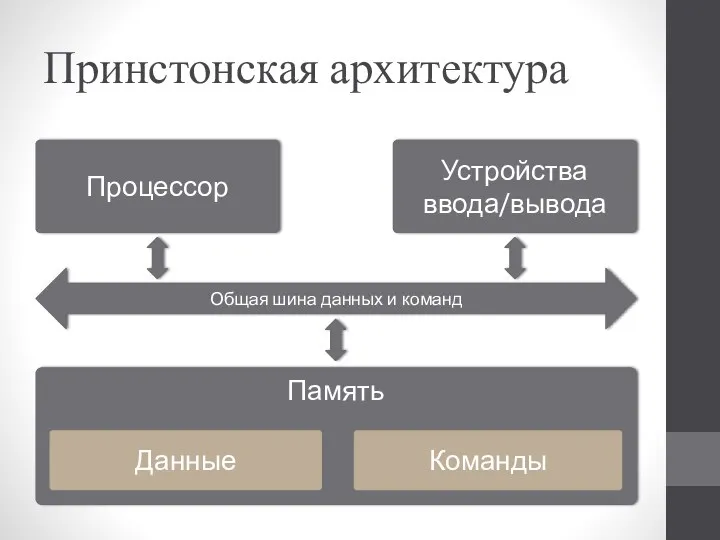

- 3. Принстонская архитектура

- 4. Гарвардская архитектура

- 5. Архитектуры CISC и RISC

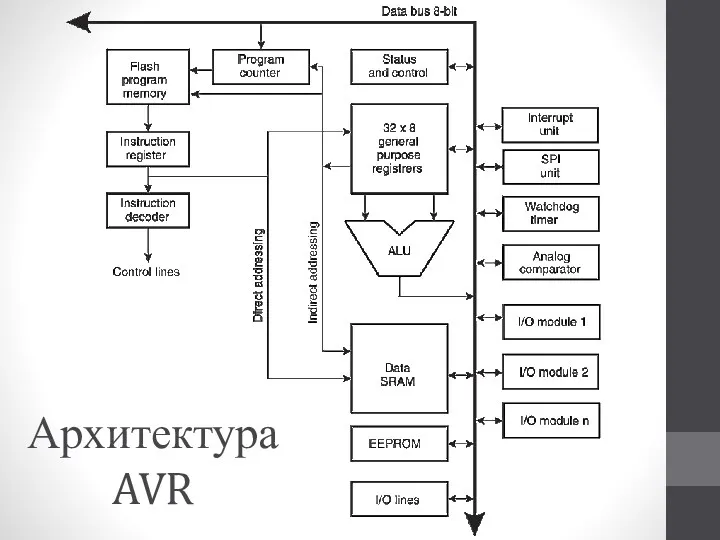

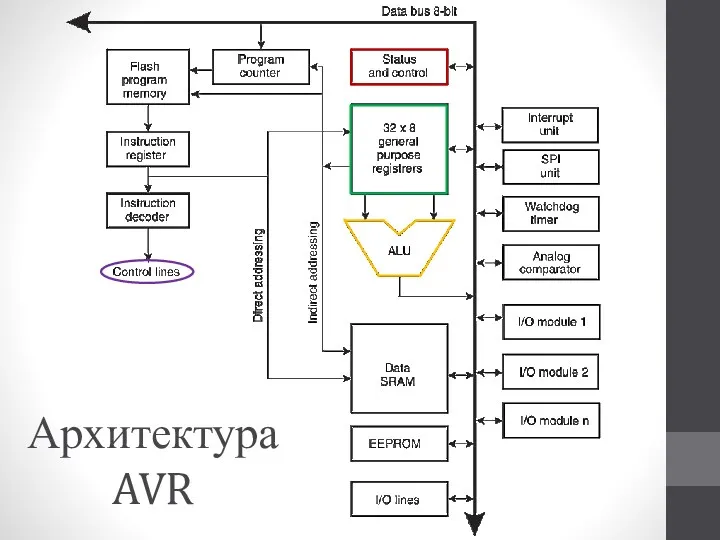

- 6. Архитектура AVR

- 7. Транзистор – всему голова База Эмиттер Коллектор Транзистор – это кнопка, которая нажимается не пальцем, а

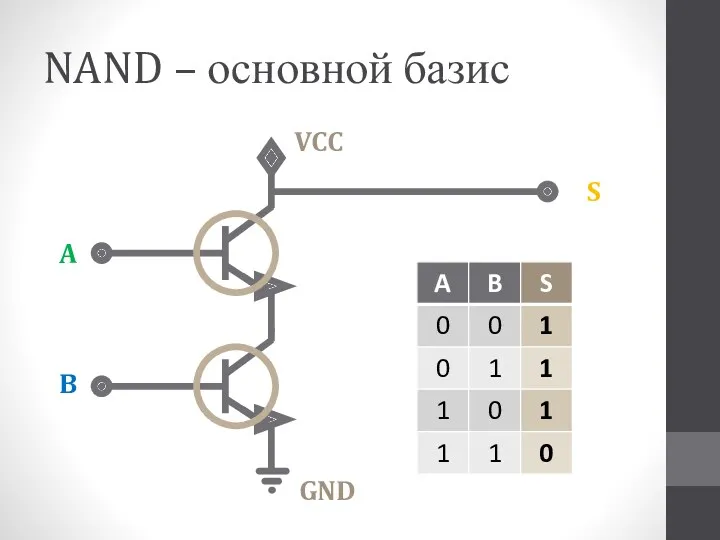

- 8. NAND – основной базис GND VCC A B S

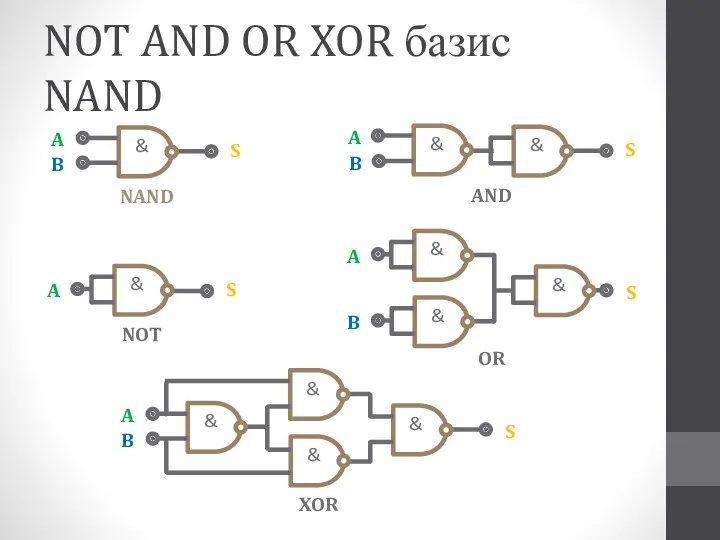

- 9. NOT AND OR XOR базис NAND

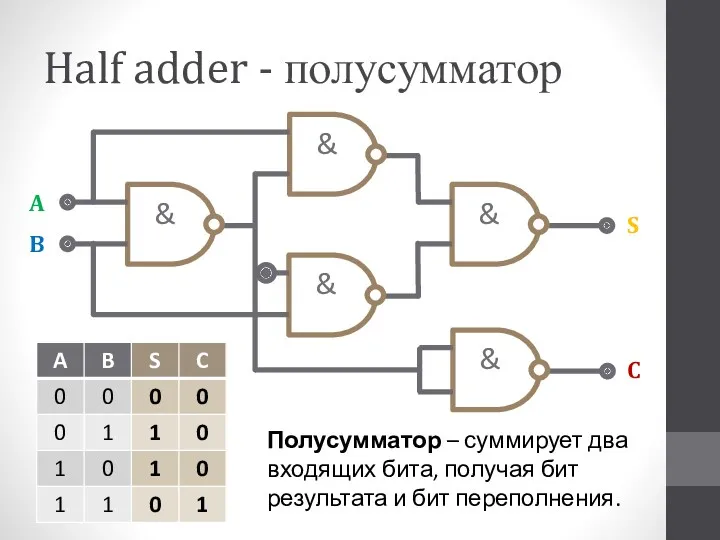

- 10. Half adder - полусумматор Полусумматор – суммирует два входящих бита, получая бит результата и бит переполнения.

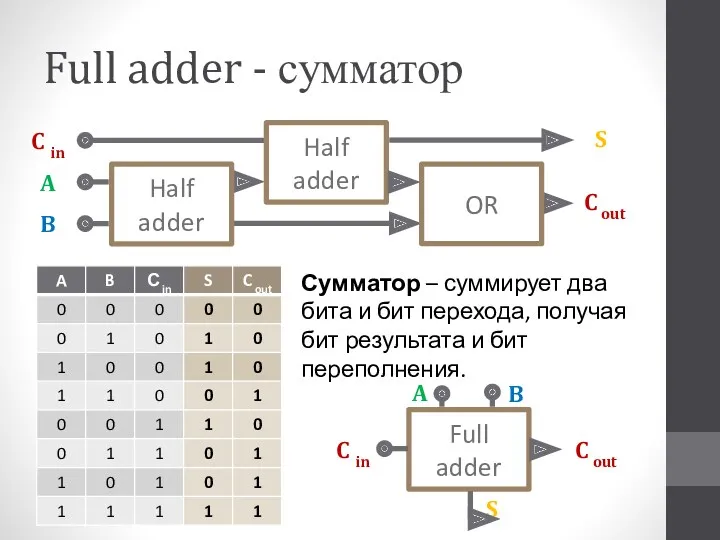

- 11. Full adder - сумматор A B S Half adder S C out Half adder OR Сумматор

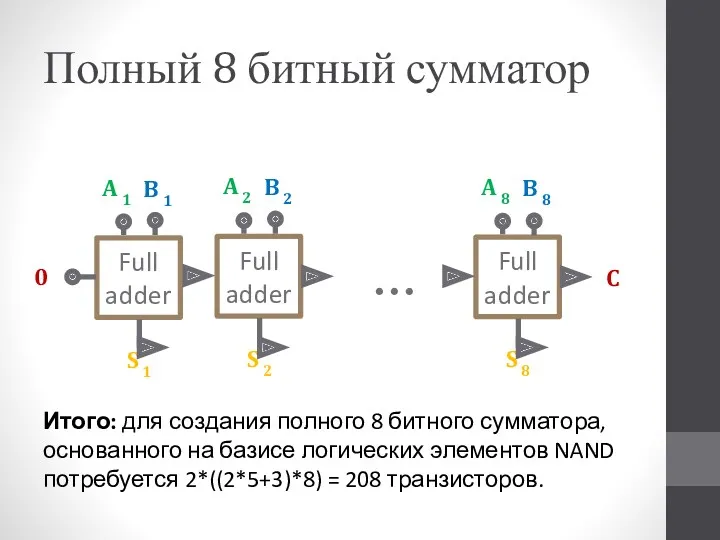

- 12. Полный 8 битный сумматор Итого: для создания полного 8 битного сумматора, основанного на базисе логических элементов

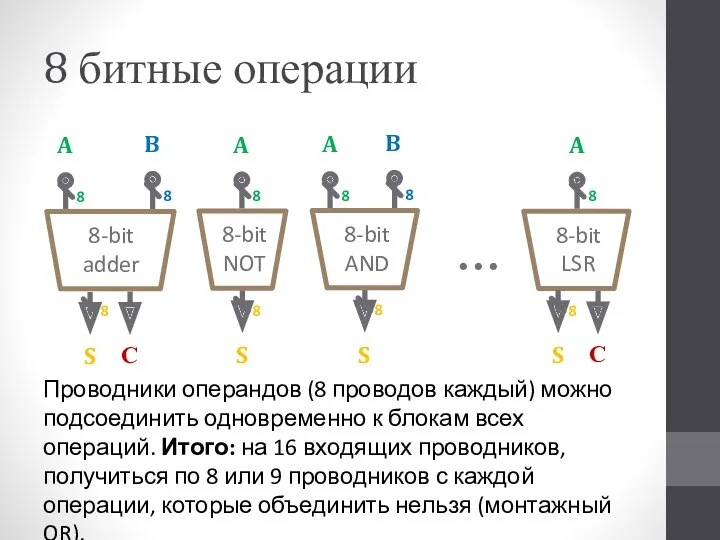

- 13. 8 битные операции Проводники операндов (8 проводов каждый) можно подсоединить одновременно к блокам всех операций. Итого:

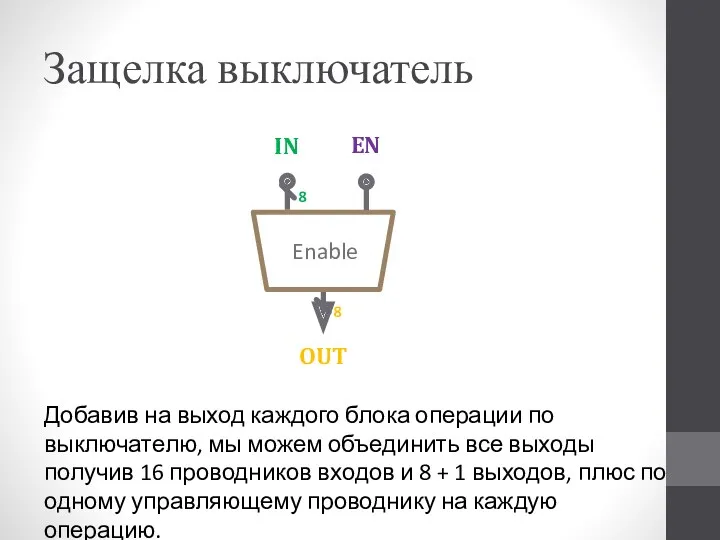

- 14. Защелка выключатель Добавив на выход каждого блока операции по выключателю, мы можем объединить все выходы получив

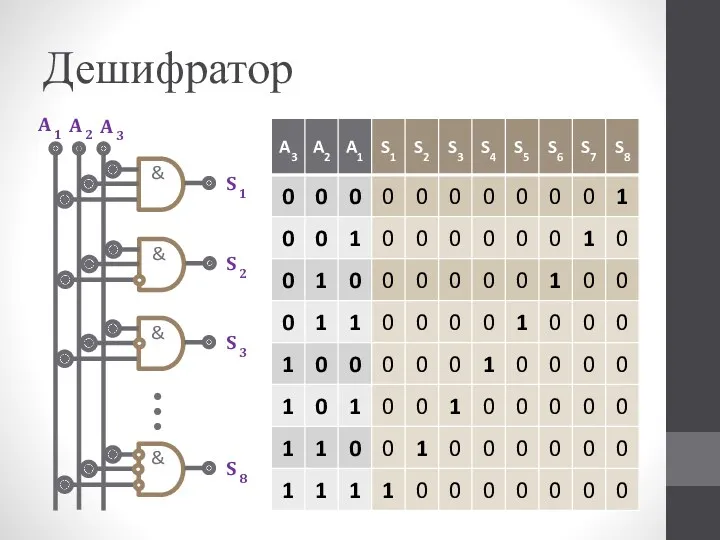

- 15. Дешифратор

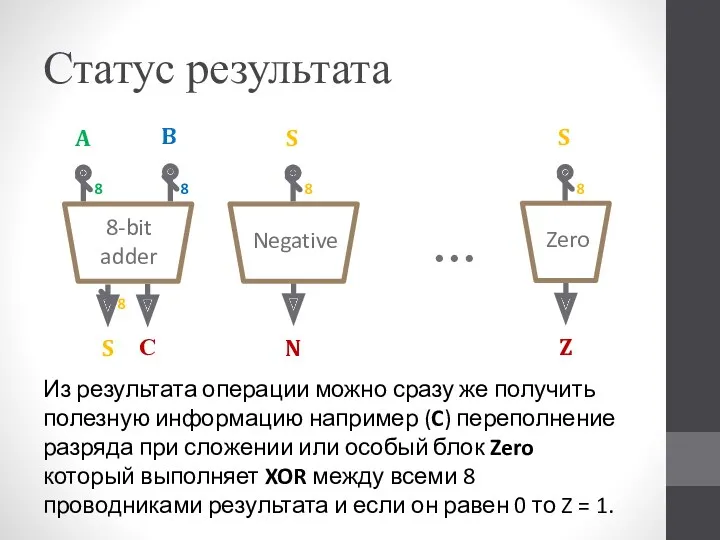

- 16. Статус результата Из результата операции можно сразу же получить полезную информацию например (C) переполнение разряда при

- 17. Арифметико-логическое устройство Операнд Операнд Статус Статус Сигналы управления Результат АЛУ

- 18. Архитектура AVR

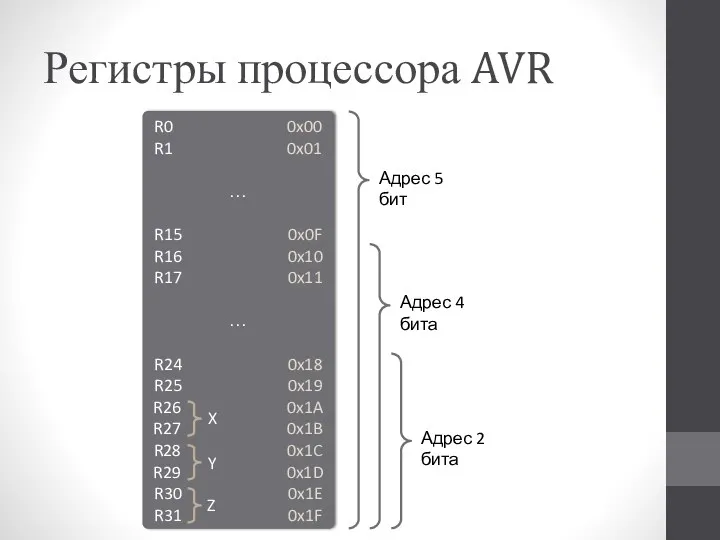

- 19. R0 0x00 R1 0x01 … R15 0x0F R16 0x10 R17 0x11 … R24 0x18 R25 0x19

- 20. Память AVR

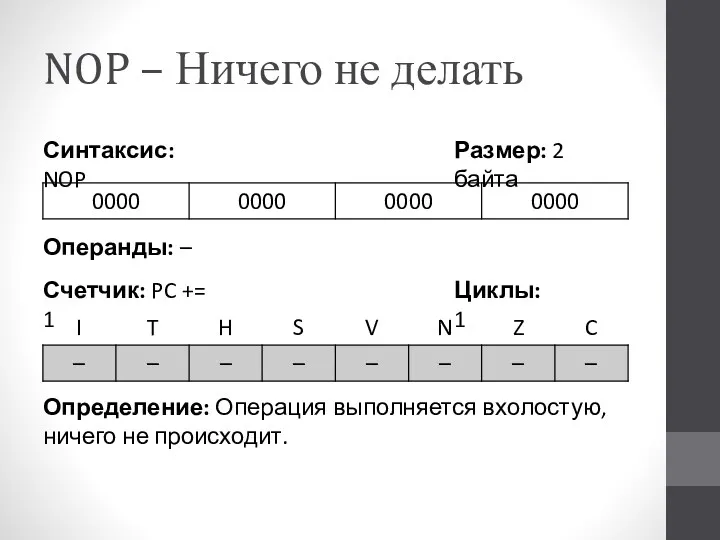

- 21. NOP – Ничего не делать Определение: Операция выполняется вхолостую, ничего не происходит. Синтаксис: NOP Размер: 2

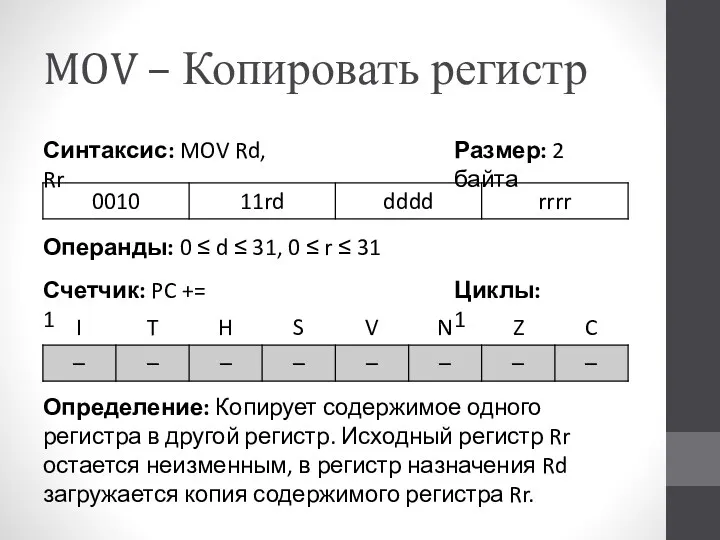

- 22. MOV – Копировать регистр Определение: Копирует содержимое одного регистра в другой регистр. Исходный регистр Rr остается

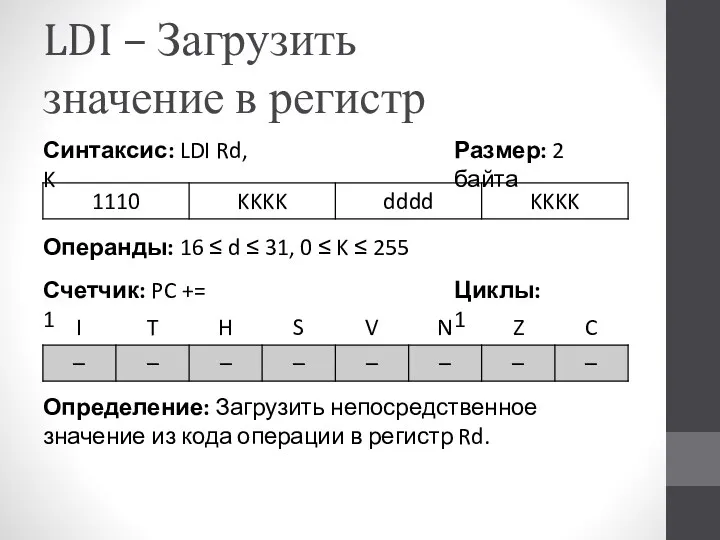

- 23. LDI – Загрузить значение в регистр Определение: Загрузить непосредственное значение из кода операции в регистр Rd.

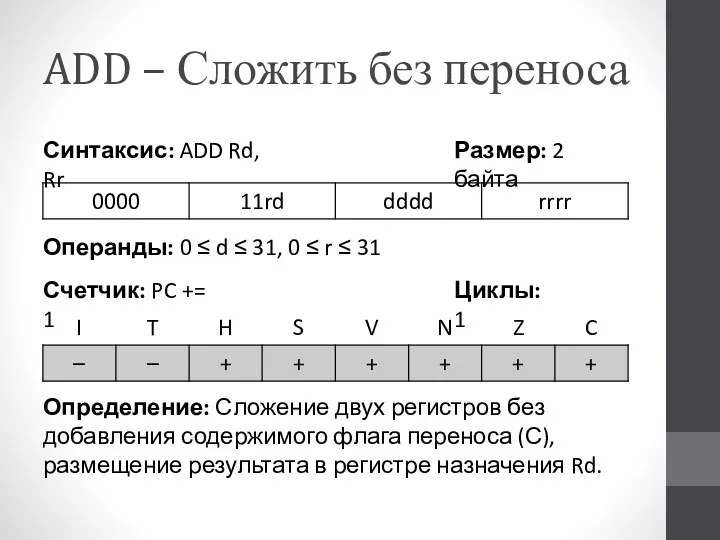

- 24. ADD – Сложить без переноса Определение: Сложение двух регистров без добавления содержимого флага переноса (С), размещение

- 26. Скачать презентацию

Алгоритмы и исполнители. (5 класс)

Алгоритмы и исполнители. (5 класс) Настройка маршрутизаторов DIR-300 и DIR-400 для работы в сети провайдера SKYNET* при помощи авторизатора

Настройка маршрутизаторов DIR-300 и DIR-400 для работы в сети провайдера SKYNET* при помощи авторизатора Элементы теории алгоритмов

Элементы теории алгоритмов Растровая и векторная графика

Растровая и векторная графика Актуалізація опорних знань. (інформатика 7 класс)

Актуалізація опорних знань. (інформатика 7 класс) Как сделать сайт максимально эффективным?

Как сделать сайт максимально эффективным? Программирование на стороне сервера. PHP

Программирование на стороне сервера. PHP Алгоритмдеу жєне программалау

Алгоритмдеу жєне программалау Алгоритмы STL

Алгоритмы STL Газета совета студенческого самоуправления

Газета совета студенческого самоуправления Компьютерные курсы. Создание трехмерных игр на движке Unity Юниум

Компьютерные курсы. Создание трехмерных игр на движке Unity Юниум Показатели публикационной активности как критерий оценки конкурентоспособности

Показатели публикационной активности как критерий оценки конкурентоспособности Алгоритмы со структурой Выбор. Урок 31

Алгоритмы со структурой Выбор. Урок 31 Communicating WNCRY

Communicating WNCRY История развития систем защиты информации

История развития систем защиты информации Hibernate query language (HQL)

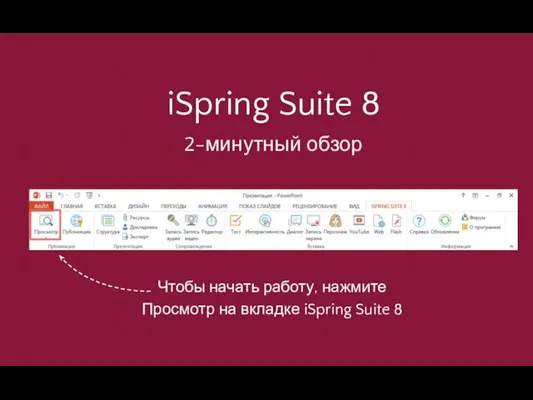

Hibernate query language (HQL) iSpring Suite 8. Быстрый инструмент для создания электронных курсов и тестов в PowerPoint

iSpring Suite 8. Быстрый инструмент для создания электронных курсов и тестов в PowerPoint Как появился компьютер, информатика 3 класс

Как появился компьютер, информатика 3 класс Поиск информации в сети Internet

Поиск информации в сети Internet Презентация к уроку информатики 3класс по теме Ориентированный граф

Презентация к уроку информатики 3класс по теме Ориентированный граф Информационные ресурсы

Информационные ресурсы Услуга Мобильные Сотрудники. МТС

Услуга Мобильные Сотрудники. МТС Основы сетей передачи данных. Общие принципы построения сетей. Коммутация каналов и пакетов

Основы сетей передачи данных. Общие принципы построения сетей. Коммутация каналов и пакетов Использование компьютерных технологий в детском саду.

Использование компьютерных технологий в детском саду. fbea8-fe014e85

fbea8-fe014e85 Текстовий редактор Word

Текстовий редактор Word Технология Умный дом

Технология Умный дом Скрипты Перезвон, Обзвон по базе

Скрипты Перезвон, Обзвон по базе