Содержание

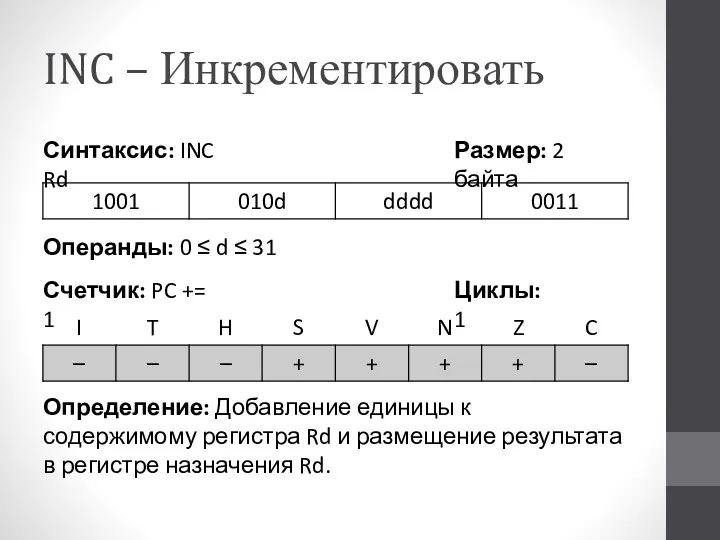

- 2. INC – Инкрементировать Определение: Добавление единицы к содержимому регистра Rd и размещение результата в регистре назначения

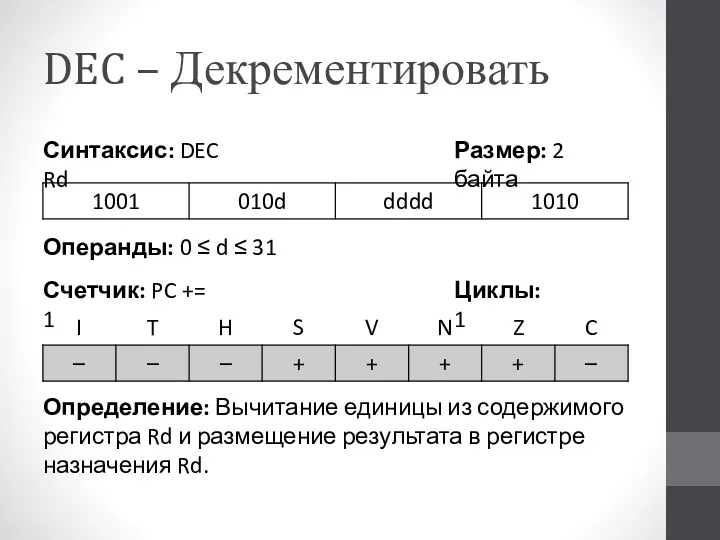

- 3. DEC – Декрементировать Определение: Вычитание единицы из содержимого регистра Rd и размещение результата в регистре назначения

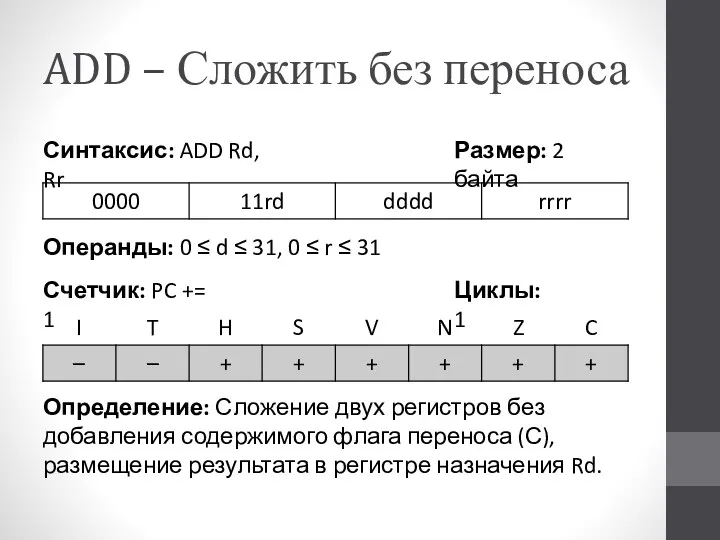

- 4. ADD – Сложить без переноса Определение: Сложение двух регистров без добавления содержимого флага переноса (С), размещение

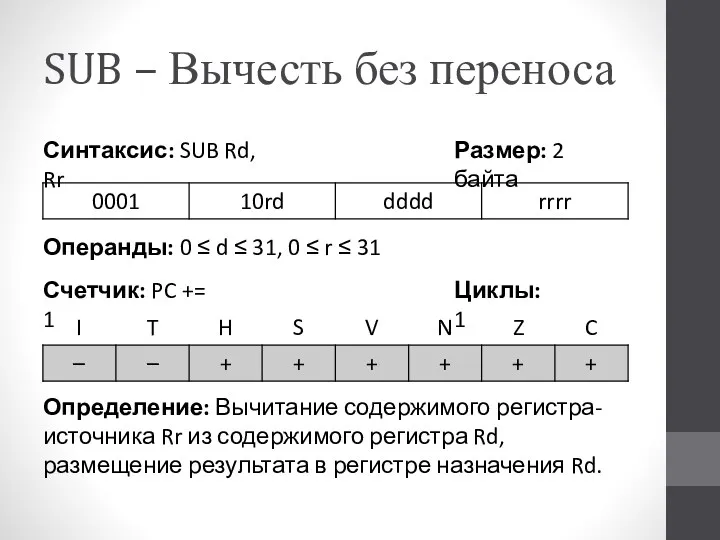

- 5. SUB – Вычесть без переноса Определение: Вычитание содержимого регистра-источника Rr из содержимого регистра Rd, размещение результата

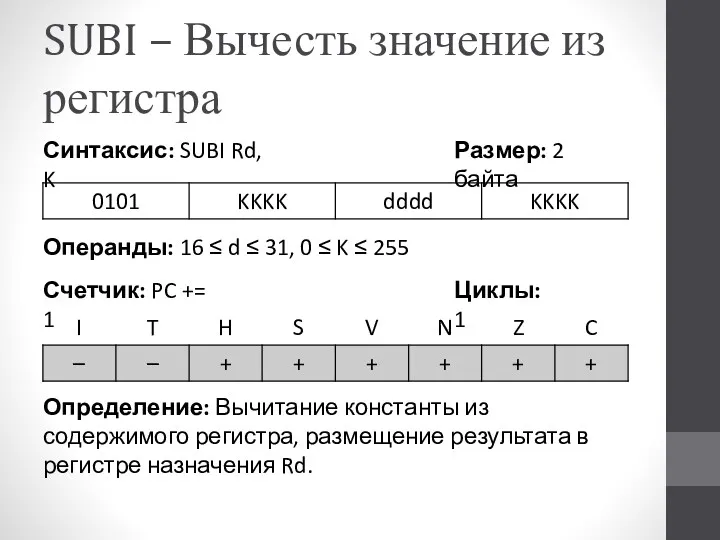

- 6. SUBI – Вычесть значение из регистра Определение: Вычитание константы из содержимого регистра, размещение результата в регистре

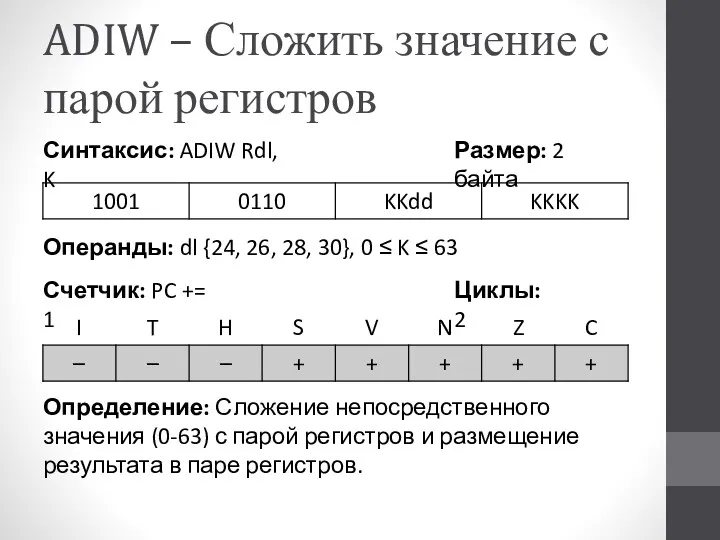

- 7. ADIW – Сложить значение с парой регистров Определение: Сложение непосредственного значения (0-63) с парой регистров и

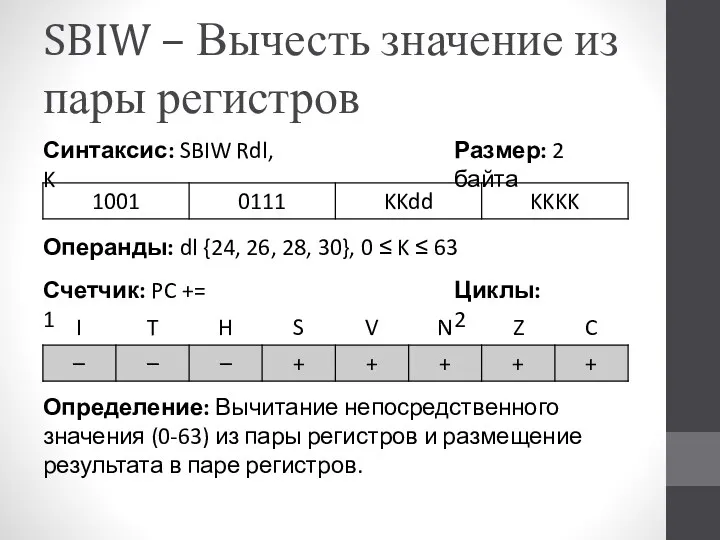

- 8. SBIW – Вычесть значение из пары регистров Определение: Вычитание непосредственного значения (0-63) из пары регистров и

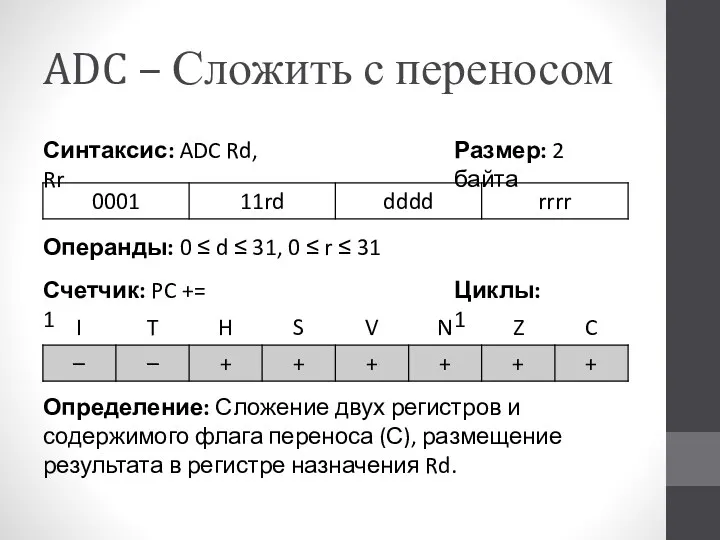

- 9. ADC – Сложить с переносом Определение: Сложение двух регистров и содержимого флага переноса (С), размещение результата

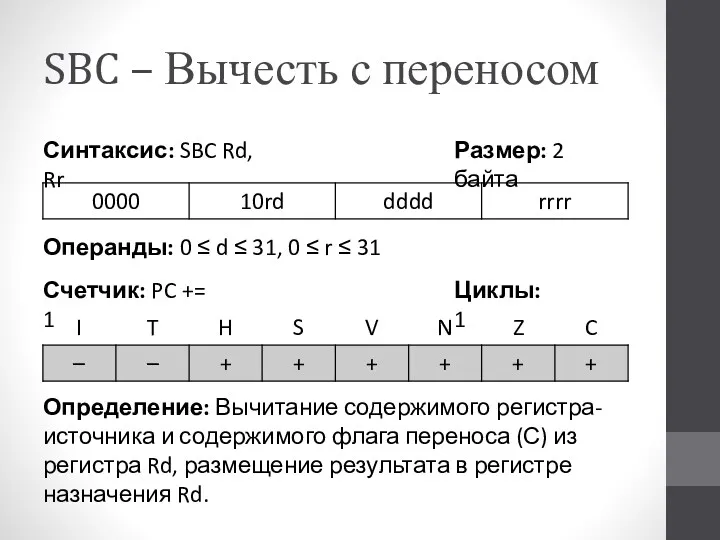

- 10. SBC – Вычесть с переносом Определение: Вычитание содержимого регистра-источника и содержимого флага переноса (С) из регистра

- 12. Скачать презентацию

1С: Администрирование

1С: Администрирование Опасный Интернет и детский суицид

Опасный Интернет и детский суицид Электронные таблицы MS Excel

Электронные таблицы MS Excel Разработка электронной торговой площадки интернет-магазина мебели Пчёлка

Разработка электронной торговой площадки интернет-магазина мебели Пчёлка Анализ сложности алгоритмов

Анализ сложности алгоритмов Компьютерные вирусы и антивирусные программы

Компьютерные вирусы и антивирусные программы Графический редактор Paint

Графический редактор Paint Презентация к уроку информатики в 5 классе по теме Табличная форма представления информации

Презентация к уроку информатики в 5 классе по теме Табличная форма представления информации Пользовательский интерфейс

Пользовательский интерфейс Информационные системы в экономике и концепции их построения

Информационные системы в экономике и концепции их построения БД и серверная часть приложения

БД и серверная часть приложения Внутренняя оптимизация

Внутренняя оптимизация Двоичная система счисления. Двоичная арифметика

Двоичная система счисления. Двоичная арифметика Малый бизнес и мобильные приложения

Малый бизнес и мобильные приложения Логические операции

Логические операции Файловые системы операционных систем MS DOS и Windows

Файловые системы операционных систем MS DOS и Windows Информационные технологии: общая характеристика

Информационные технологии: общая характеристика Масиви та рядки. Алгоритми сортування масивів даних

Масиви та рядки. Алгоритми сортування масивів даних Понятие как форма мышления. 6 класс

Понятие как форма мышления. 6 класс Электронные таблицы

Электронные таблицы Создание гипертекстовых страниц информации. Основы языка HTML

Создание гипертекстовых страниц информации. Основы языка HTML Optimizing device drivers for terminal server’s plug and play device redirection framework

Optimizing device drivers for terminal server’s plug and play device redirection framework Табличные процессоры. Создание и обработка документов в MS Office c помощью приложения Ms Excel. (Лекция 5)

Табличные процессоры. Создание и обработка документов в MS Office c помощью приложения Ms Excel. (Лекция 5) Нехимические зависимости

Нехимические зависимости Инфо-умники и умницы. Викторина

Инфо-умники и умницы. Викторина Теория алгоритмов

Теория алгоритмов Информационная культура

Информационная культура презентация Моделирование. Введение в теорию графов

презентация Моделирование. Введение в теорию графов