Содержание

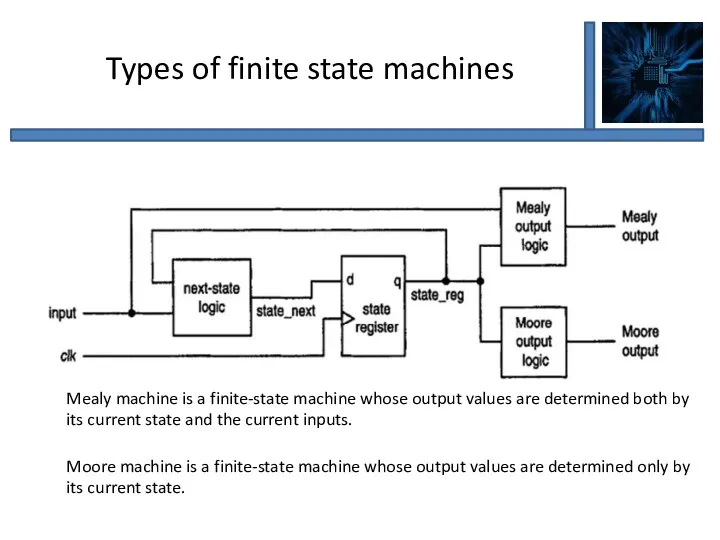

- 2. Types of finite state machines Mealy machine is a finite-state machine whose output values are determined

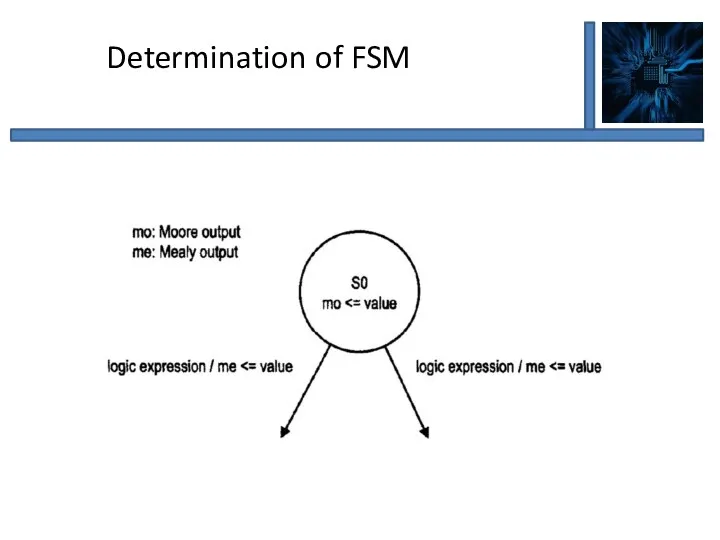

- 3. Determination of FSM

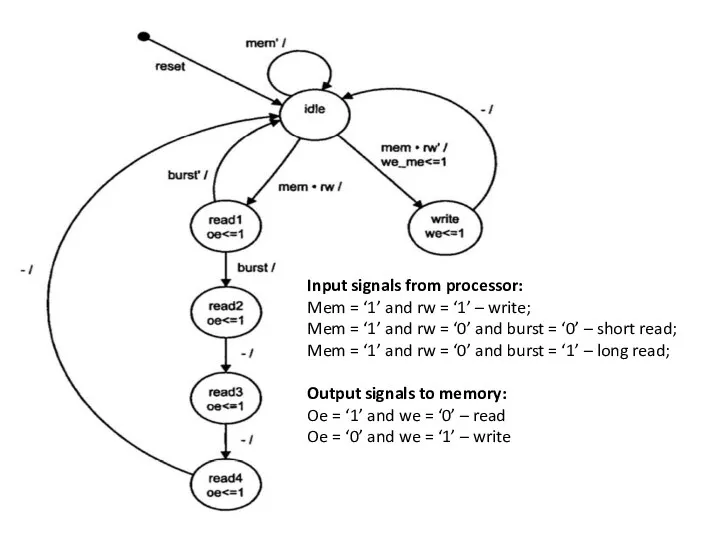

- 4. Input signals from processor: Mem = ‘1’ and rw = ‘1’ – write; Mem = ‘1’

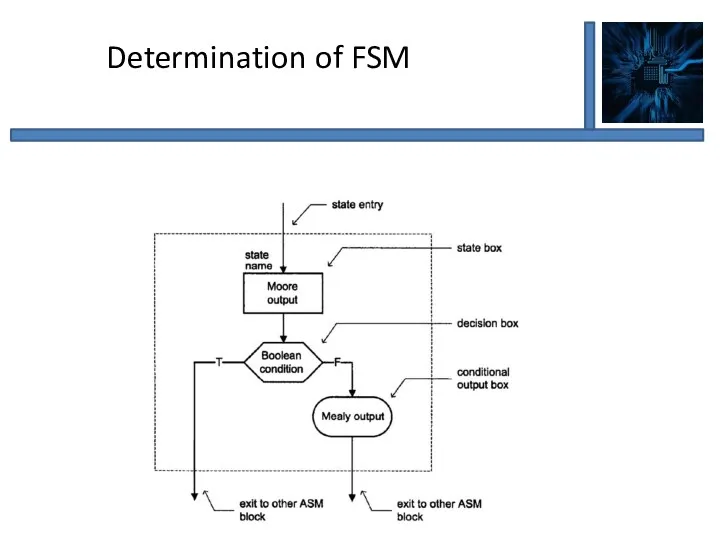

- 5. Determination of FSM

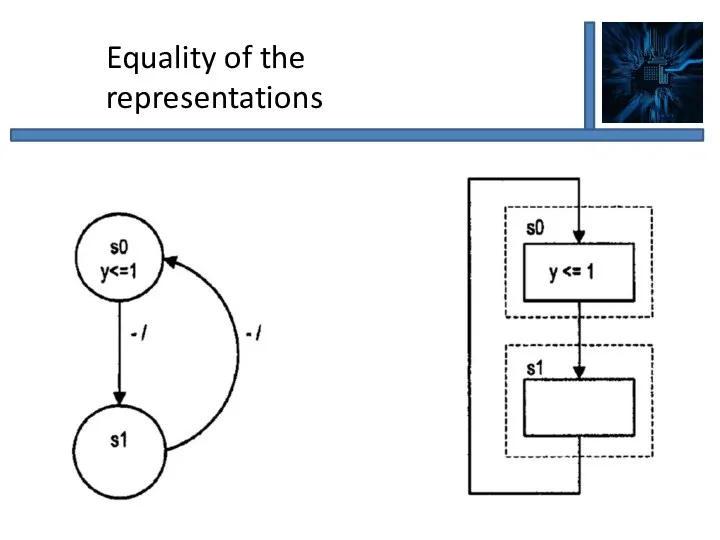

- 6. Equality of the representations

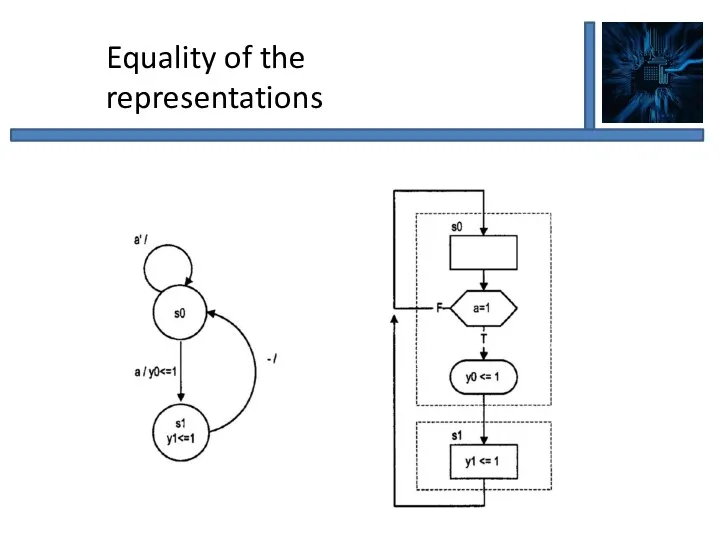

- 7. Equality of the representations

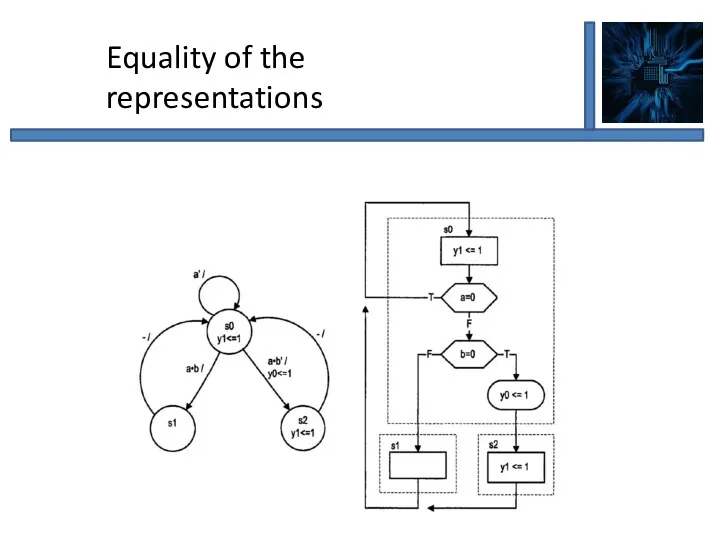

- 8. Equality of the representations

- 9. Main rules Each input combination Каждой входной комбинации должен соответствовать единственный выходной путь из данного узла

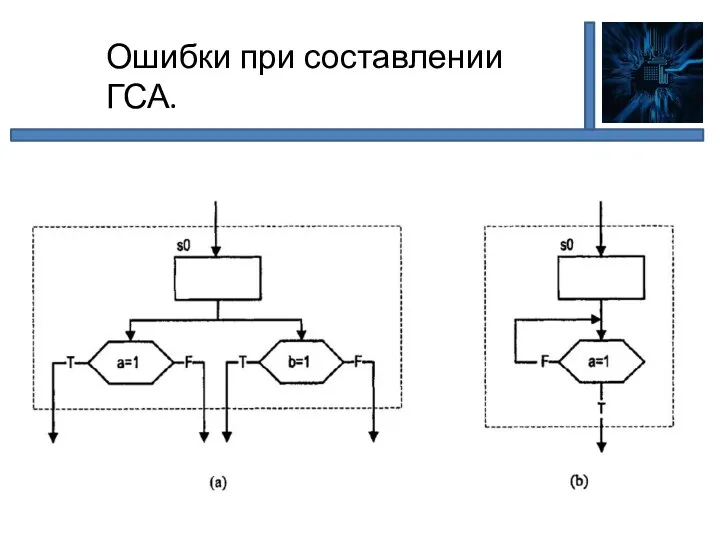

- 10. Ошибки при составлении ГСА.

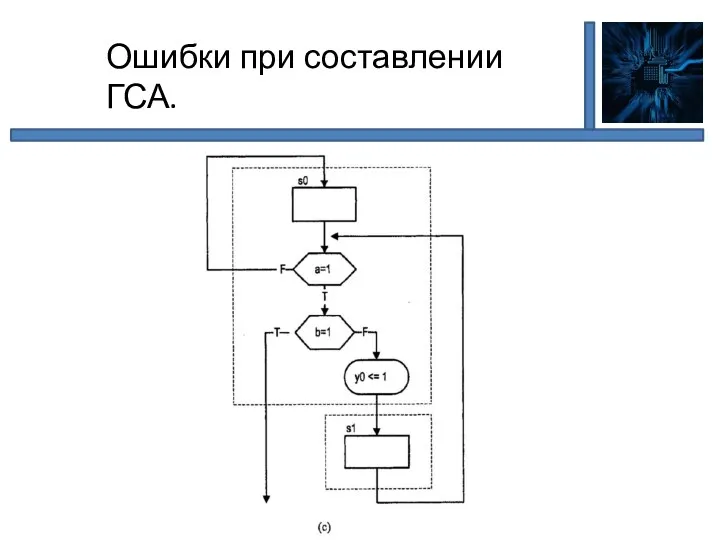

- 11. Ошибки при составлении ГСА.

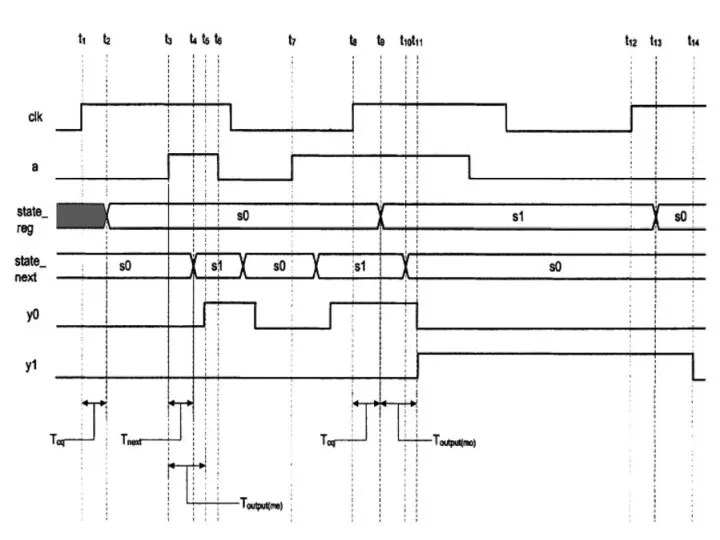

- 12. Временная диаграмма конечного автомата.

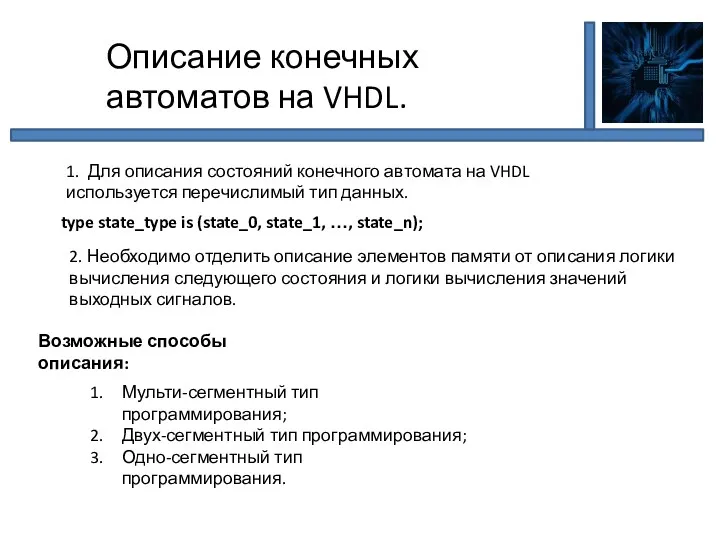

- 14. Описание конечных автоматов на VHDL. 1. Для описания состояний конечного автомата на VHDL используется перечислимый тип

- 15. Мульти-сегментный тип программирования.

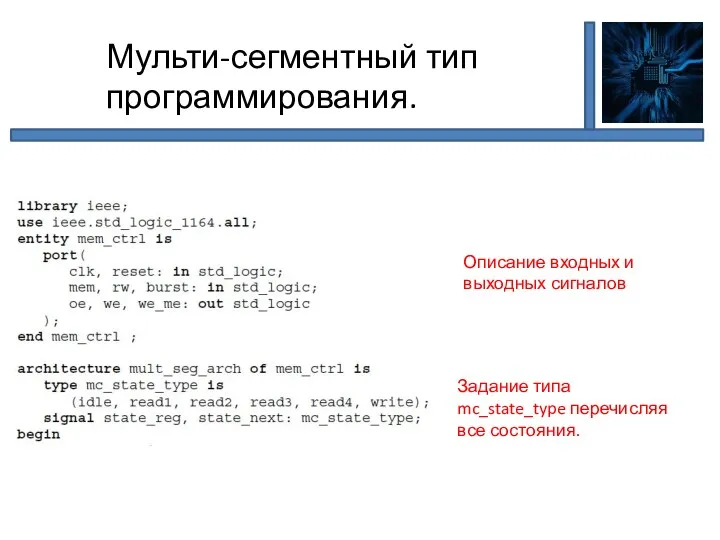

- 16. Мульти-сегментный тип программирования. Описание входных и выходных сигналов Задание типа mc_state_type перечисляя все состояния.

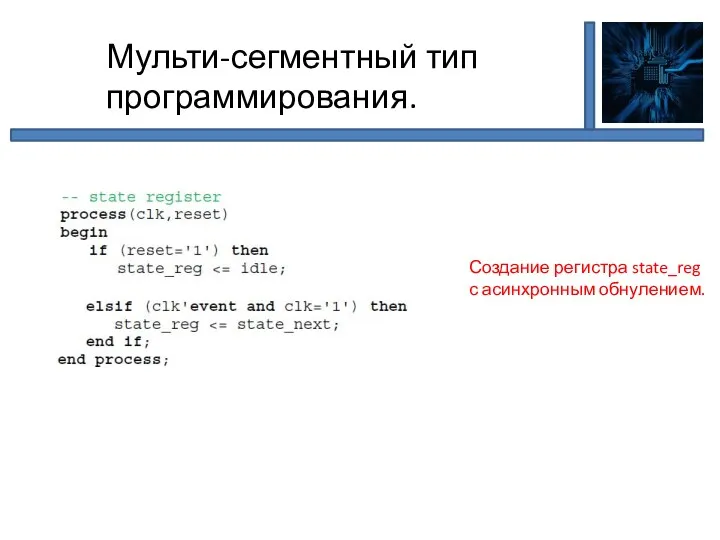

- 17. Мульти-сегментный тип программирования. Создание регистра state_reg с асинхронным обнулением.

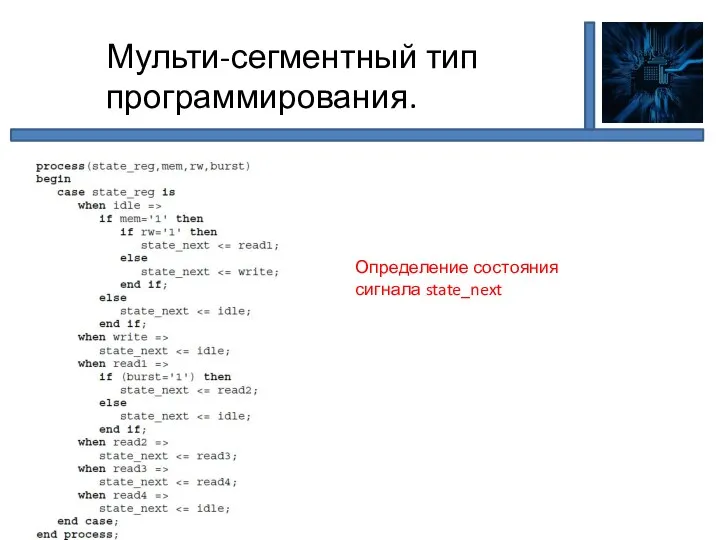

- 18. Мульти-сегментный тип программирования. Определение состояния сигнала state_next

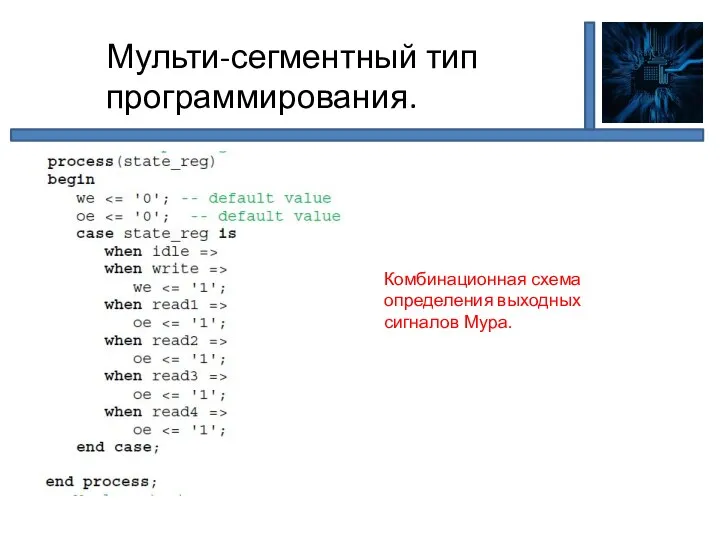

- 19. Мульти-сегментный тип программирования. Комбинационная схема определения выходных сигналов Мура.

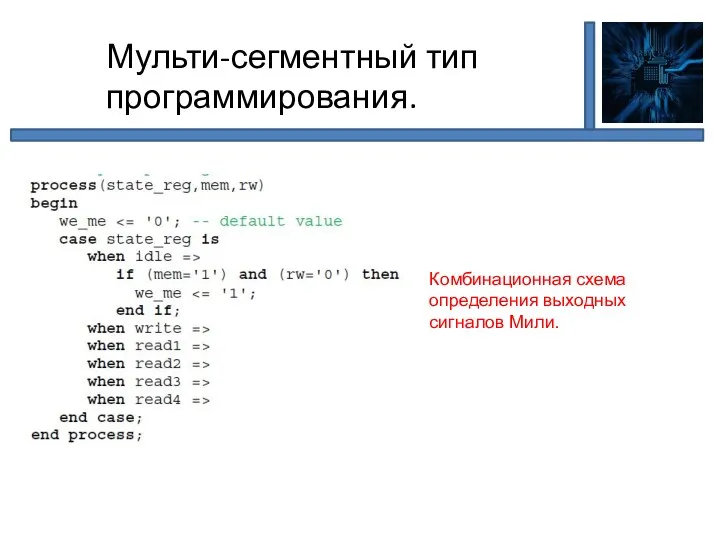

- 20. Мульти-сегментный тип программирования. Комбинационная схема определения выходных сигналов Мили.

- 21. Двух-сегментный тип программирования.

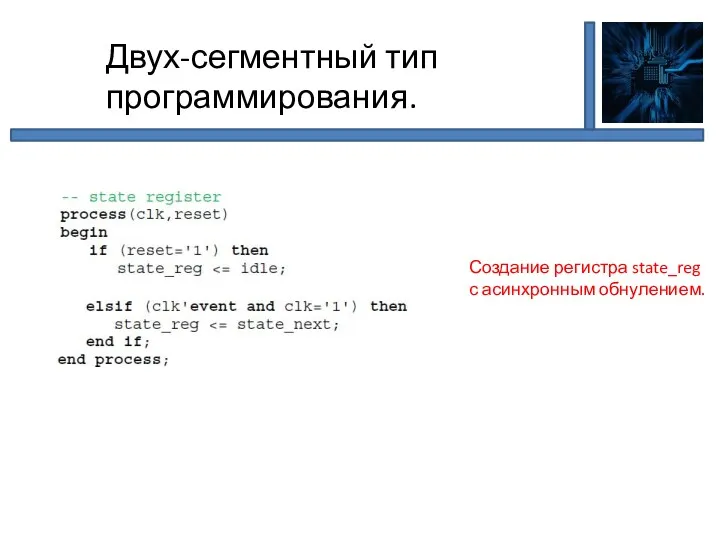

- 22. Двух-сегментный тип программирования. Создание регистра state_reg с асинхронным обнулением.

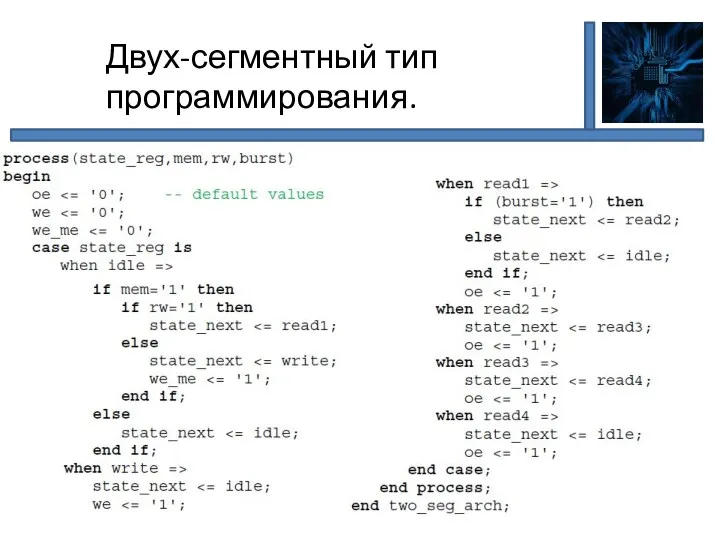

- 23. Двух-сегментный тип программирования.

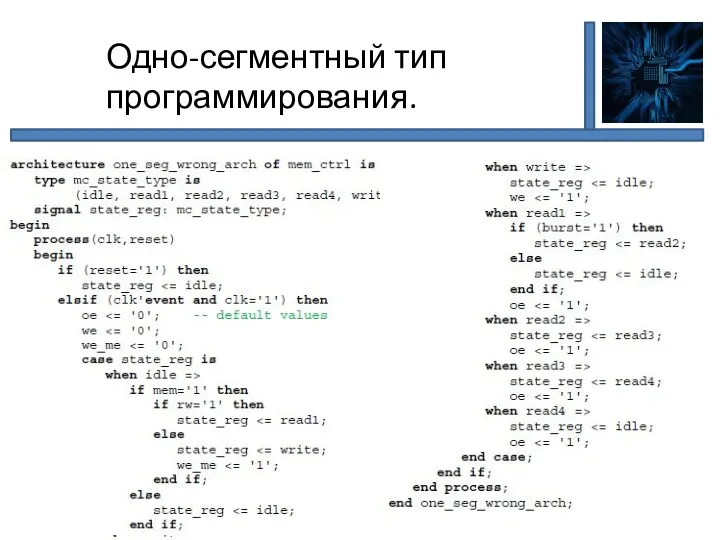

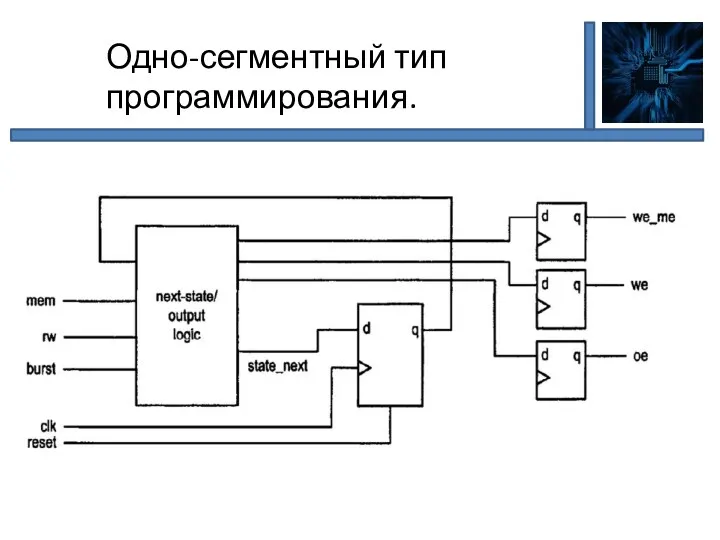

- 24. Одно-сегментный тип программирования.

- 25. Одно-сегментный тип программирования.

- 26. Кодирование состояний

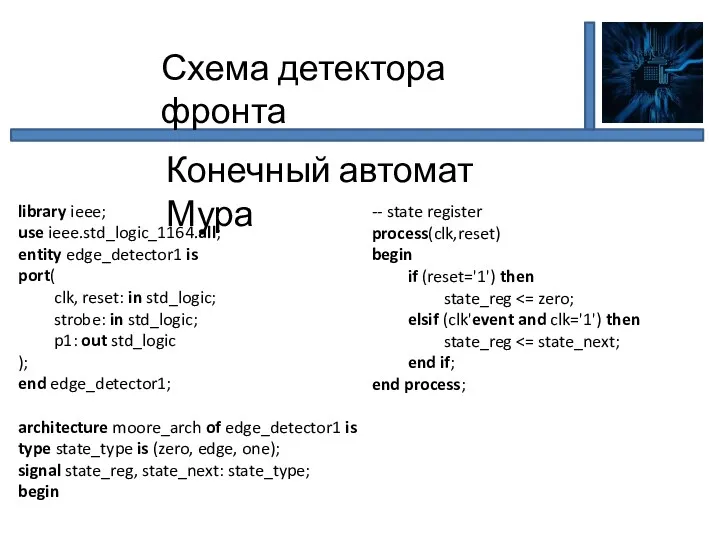

- 27. Схема детектора фронта Конечный автомат Мура library ieee; use ieee.std_logic_1164.all; entity edge_detector1 is port( clk, reset:

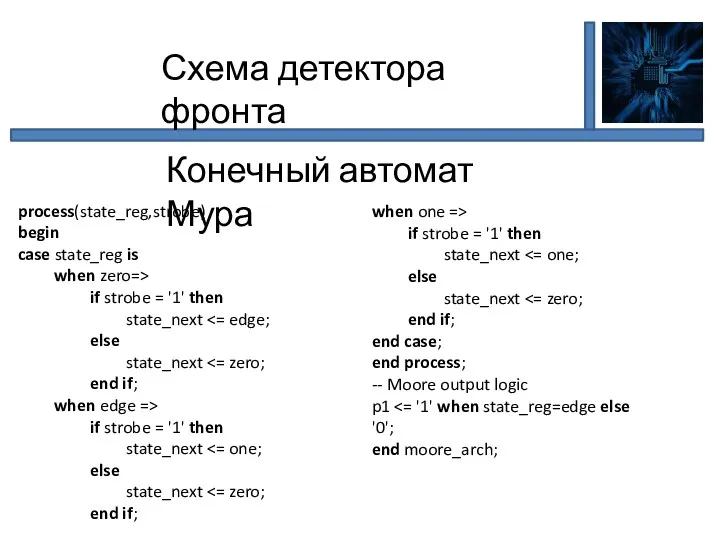

- 28. Схема детектора фронта Конечный автомат Мура process(state_reg,strobe) begin case state_reg is when zero=> if strobe =

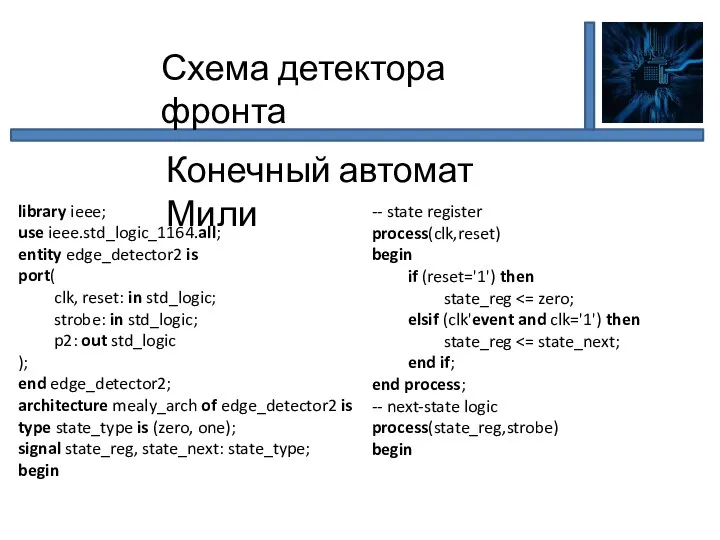

- 29. Схема детектора фронта Конечный автомат Мили library ieee; use ieee.std_logic_1164.all; entity edge_detector2 is port( clk, reset:

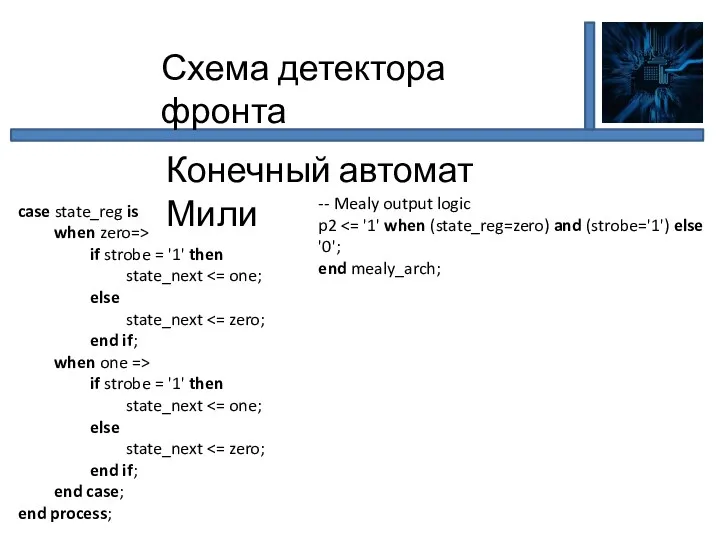

- 30. Схема детектора фронта Конечный автомат Мили case state_reg is when zero=> if strobe = '1' then

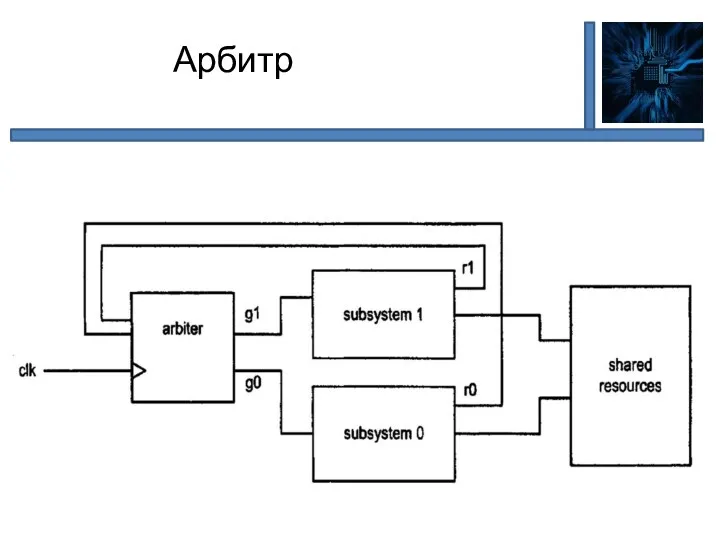

- 31. Арбитр

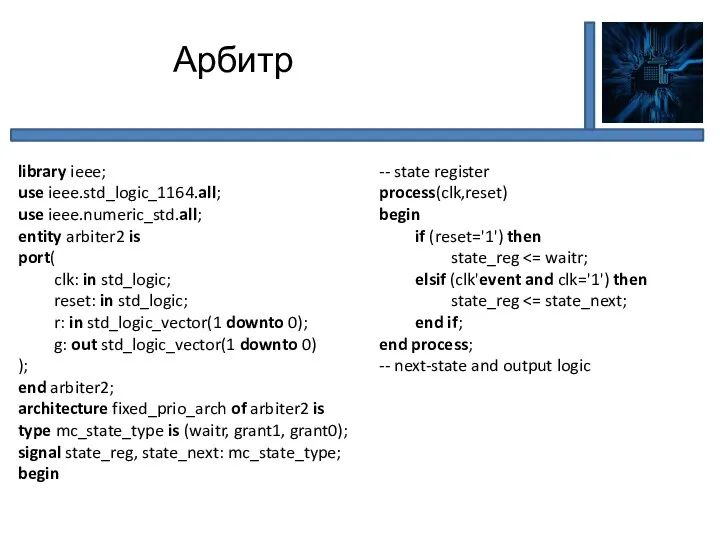

- 32. Арбитр library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity arbiter2 is port( clk: in std_logic; reset: in

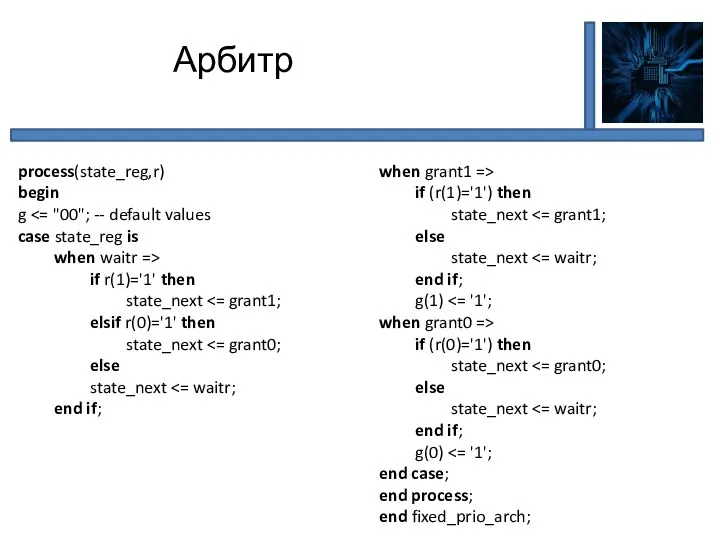

- 33. Арбитр process(state_reg,r) begin g case state_reg is when waitr => if r(1)='1' then state_next elsif r(0)='1'

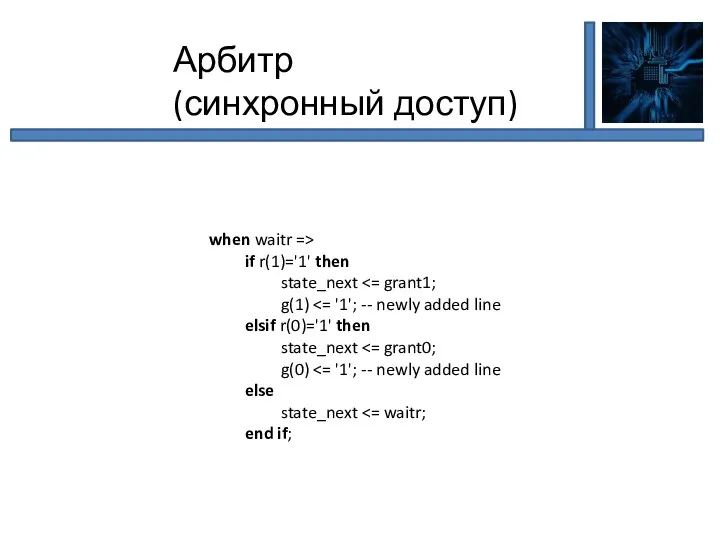

- 34. Арбитр (синхронный доступ) when waitr => if r(1)='1' then state_next g(1) elsif r(0)='1' then state_next g(0)

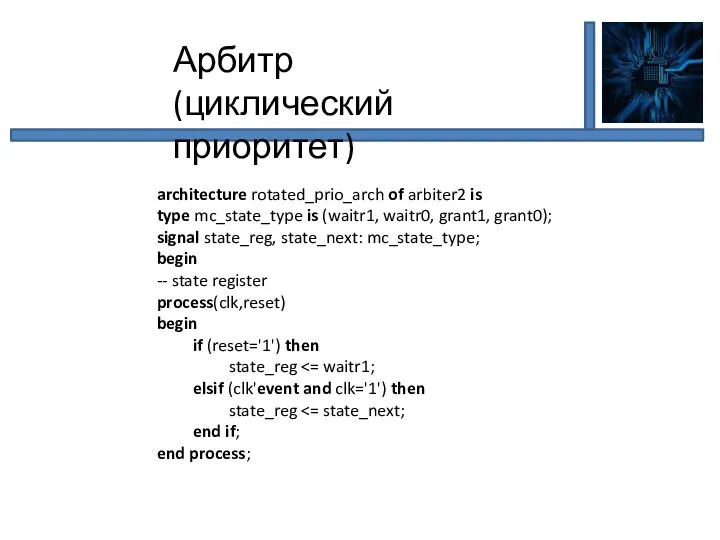

- 35. Арбитр (циклический приоритет) architecture rotated_prio_arch of arbiter2 is type mc_state_type is (waitr1, waitr0, grant1, grant0); signal

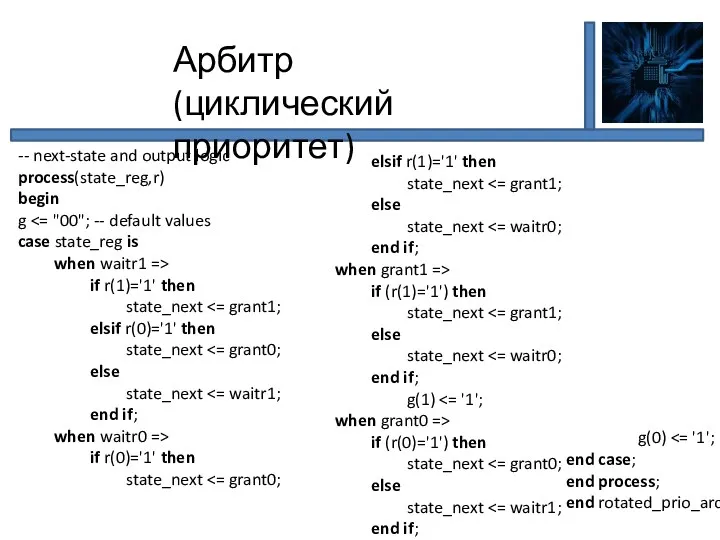

- 36. Арбитр (циклический приоритет) -- next-state and output logic process(state_reg,r) begin g case state_reg is when waitr1

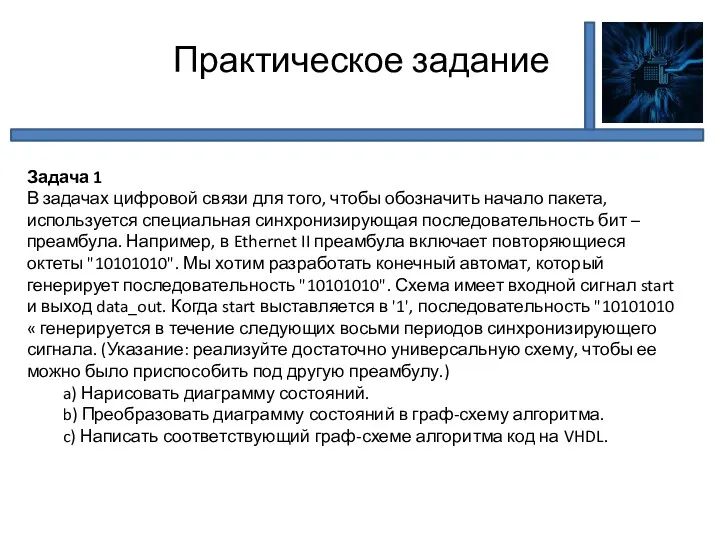

- 37. Практическое задание Задача 1 В задачах цифровой связи для того, чтобы обозначить начало пакета, используется специальная

- 38. Практическое задание Задача 2 Модифицируйте генератор преамбулы таким образом, чтобы он преобразовывал заданную в параллельном коде

- 39. Домашнее задание 1. В режиме пакетного чтения ("burst") контроллера памяти неявно требуется, чтобы процессор сначала выставлял

- 40. Домашнее задание 3. Разработайте конечный автомат, детектирующий последовательность "10101010" во входном сигнале на стороне получателя. Схема

- 42. Скачать презентацию

Декоративно-прикладне мистецтво. Підручник

Декоративно-прикладне мистецтво. Підручник Задачи по теме Алгоритмизация. Алгоритмы с ветвлениями.

Задачи по теме Алгоритмизация. Алгоритмы с ветвлениями. Организация современного телевидения и перспективы развития. Лекция 2

Организация современного телевидения и перспективы развития. Лекция 2 Моделирование как метод познания

Моделирование как метод познания С++ // язык программирования

С++ // язык программирования Классы и объекты

Классы и объекты Наследование. Базовые понятия и примеры (лекция 8)

Наследование. Базовые понятия и примеры (лекция 8) Сервисы Google

Сервисы Google Параллельное и многопоточное программирование. (Лекция 7)

Параллельное и многопоточное программирование. (Лекция 7) Разработка агрегатора для подбора банковских услуг

Разработка агрегатора для подбора банковских услуг Зв'язані списки у програмуванні

Зв'язані списки у програмуванні Возможности, структура и основные элементы языка HTML

Возможности, структура и основные элементы языка HTML Создавай легко с программой Online Test Pad

Создавай легко с программой Online Test Pad Выборка данных из нескольких таблиц

Выборка данных из нескольких таблиц Passive Past Simple

Passive Past Simple Система автоматизации библиотек ИРБИС

Система автоматизации библиотек ИРБИС 1015355

1015355 Scrum метрики

Scrum метрики Up work app. App Idea Explained

Up work app. App Idea Explained Опыт внедрения BDD в разработку

Опыт внедрения BDD в разработку Операционные устройства (ОУ)

Операционные устройства (ОУ) Network security

Network security Задача физической передачи данных. Основные методы доступа

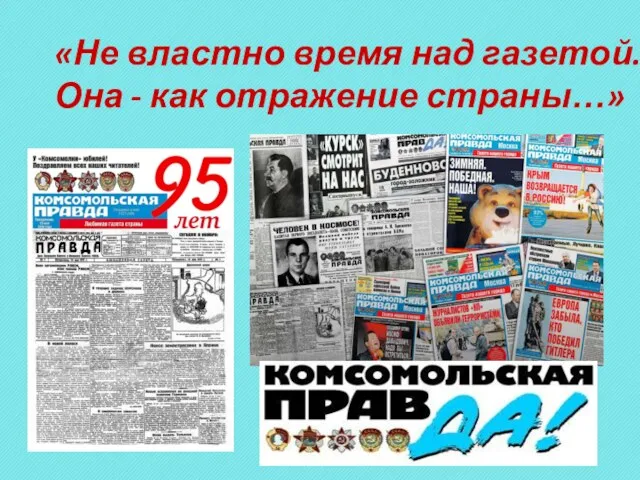

Задача физической передачи данных. Основные методы доступа К 95-летию КП. Не властно время над газетой. Она - как отражение страны…

К 95-летию КП. Не властно время над газетой. Она - как отражение страны… Принцип наглядности и компьютерная графика

Принцип наглядности и компьютерная графика Разработка web-сайта для ООО Севердойстрой

Разработка web-сайта для ООО Севердойстрой Экосистема больших данных

Экосистема больших данных Базы данных. Что это?

Базы данных. Что это?