Слайд 2

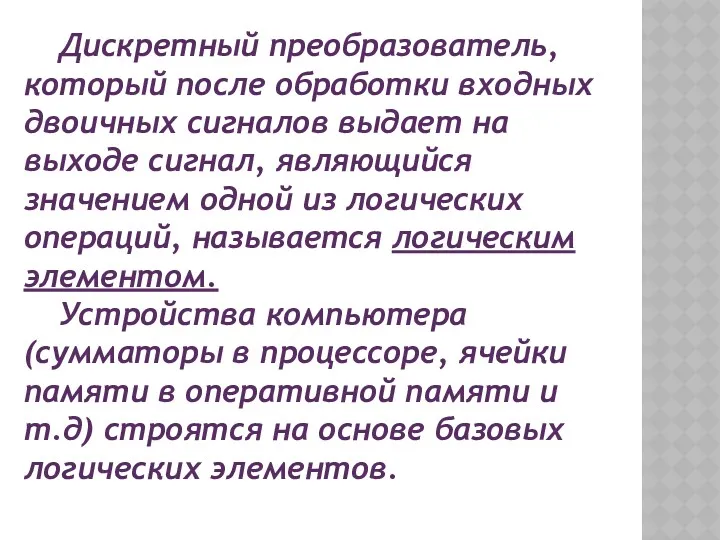

Дискретный преобразователь, который после обработки входных двоичных сигналов выдает на выходе

сигнал, являющийся значением одной из логических операций, называется логическим элементом.

Устройства компьютера (сумматоры в процессоре, ячейки памяти в оперативной памяти и т.д) строятся на основе базовых логических элементов.

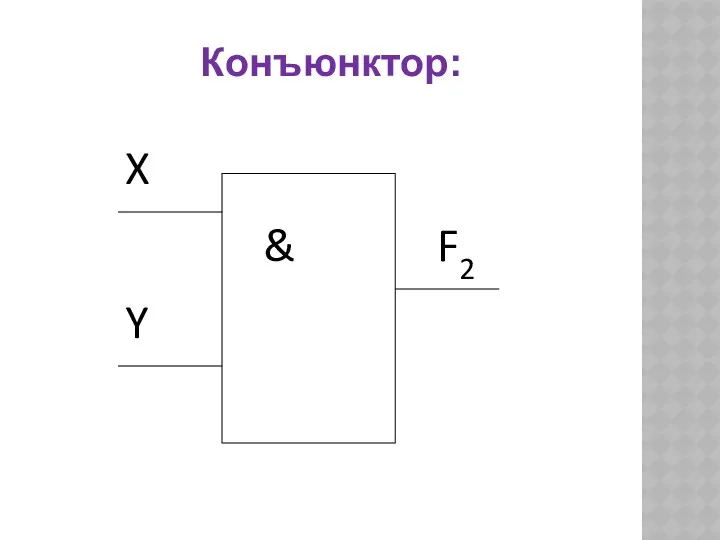

Слайд 3

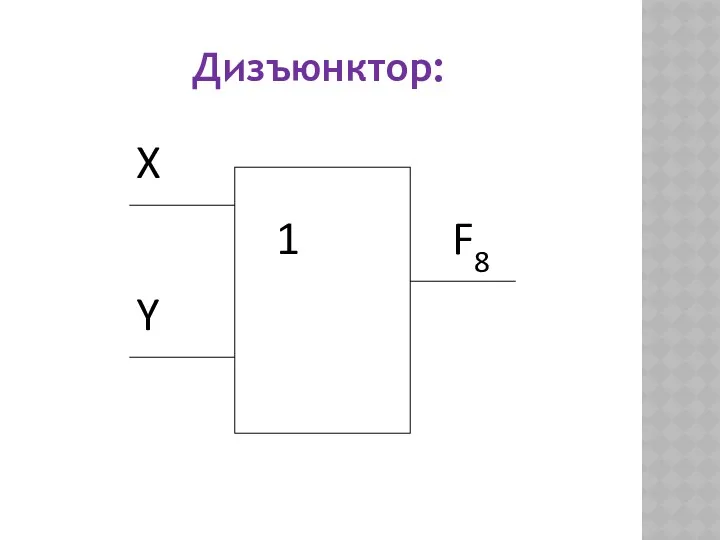

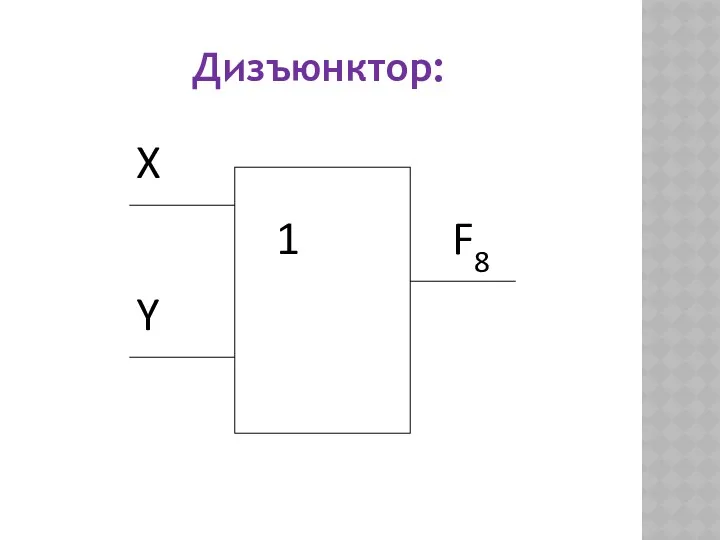

Слайд 4

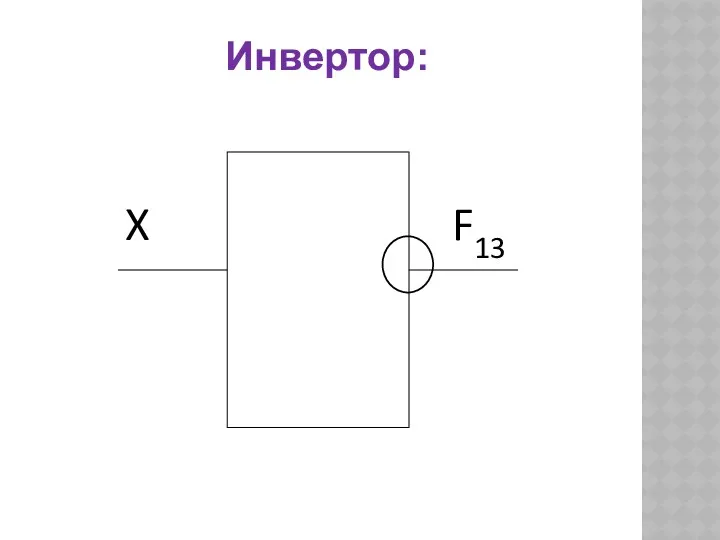

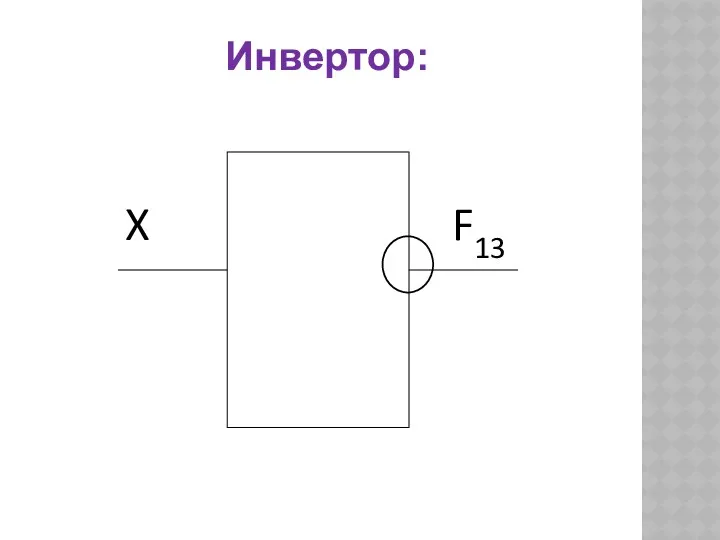

Слайд 5

Слайд 6

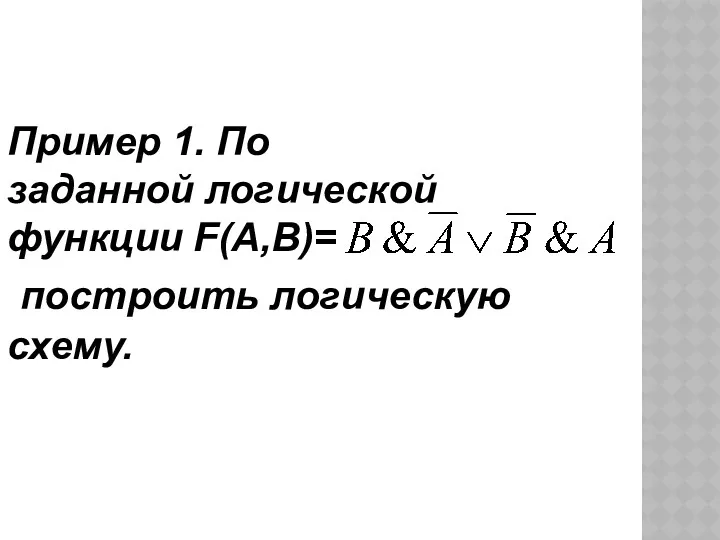

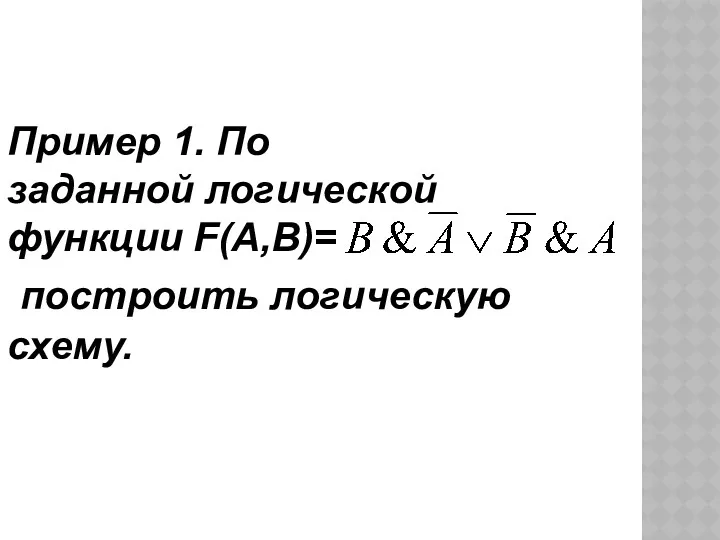

Пример 1. По заданной логической функции F(A,B)=

построить логическую схему.

Слайд 7

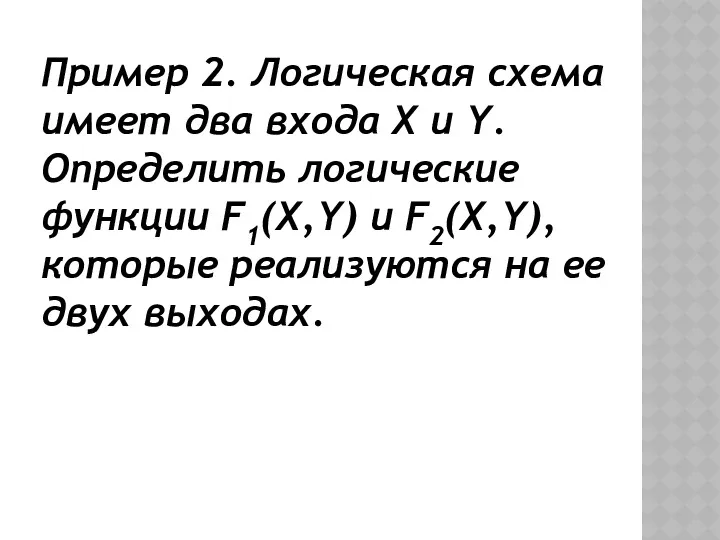

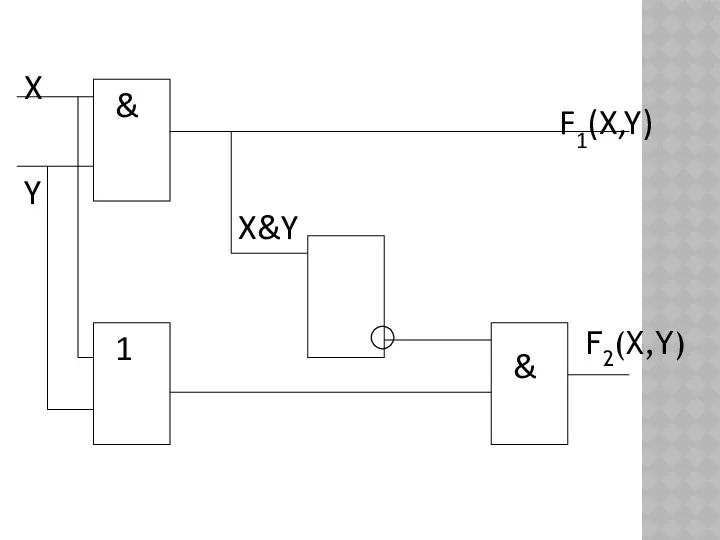

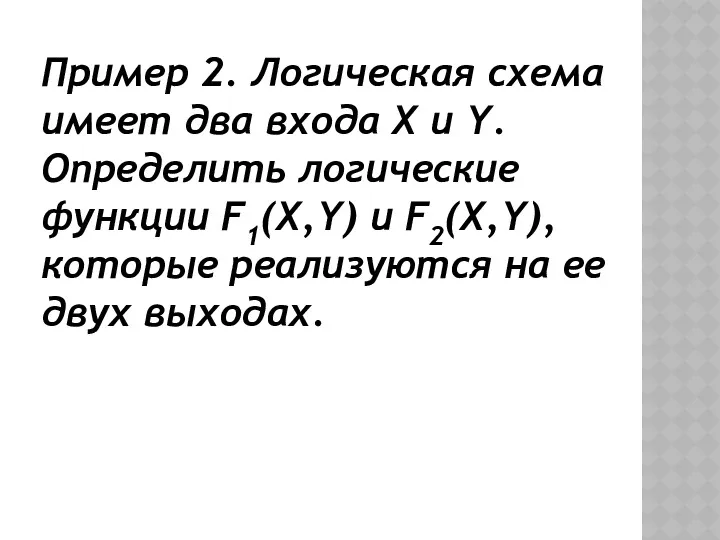

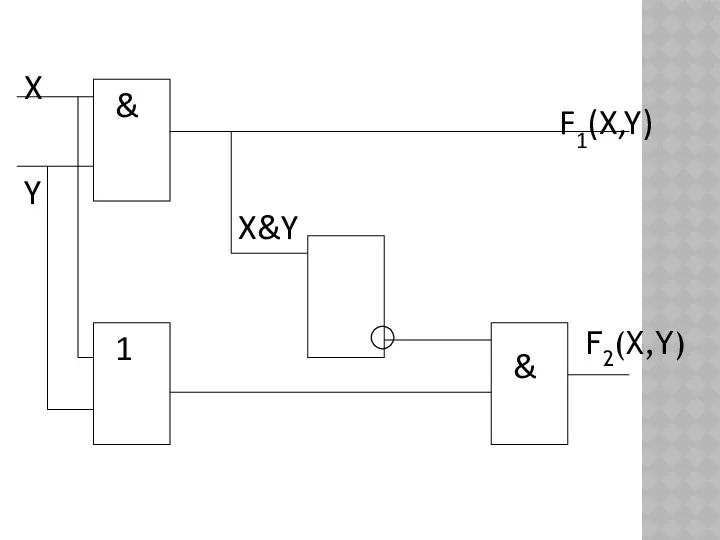

Пример 2. Логическая схема имеет два входа X и Y. Определить

логические функции F1(X,Y) и F2(X,Y), которые реализуются на ее двух выходах.

Слайд 8

Слайд 9

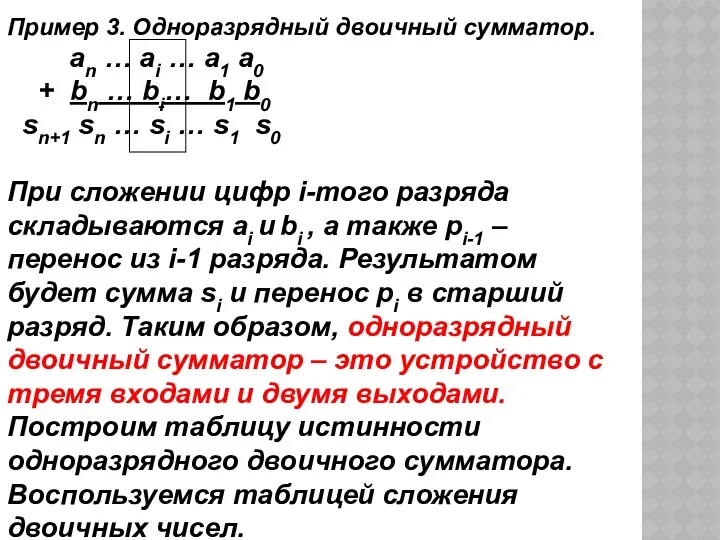

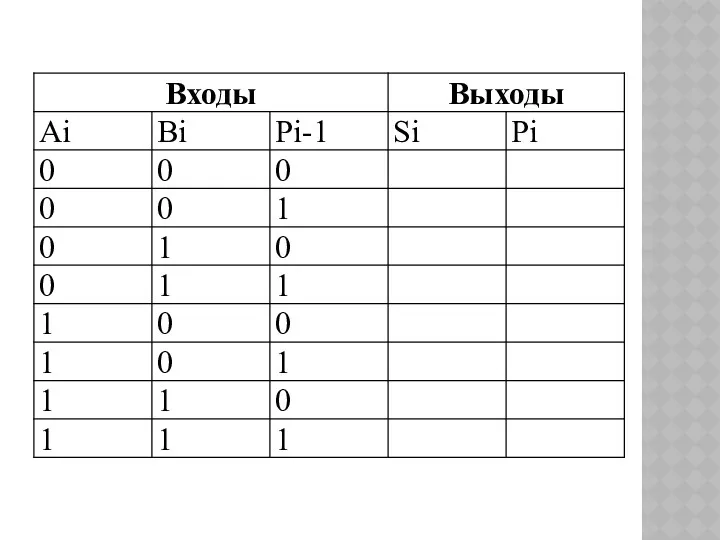

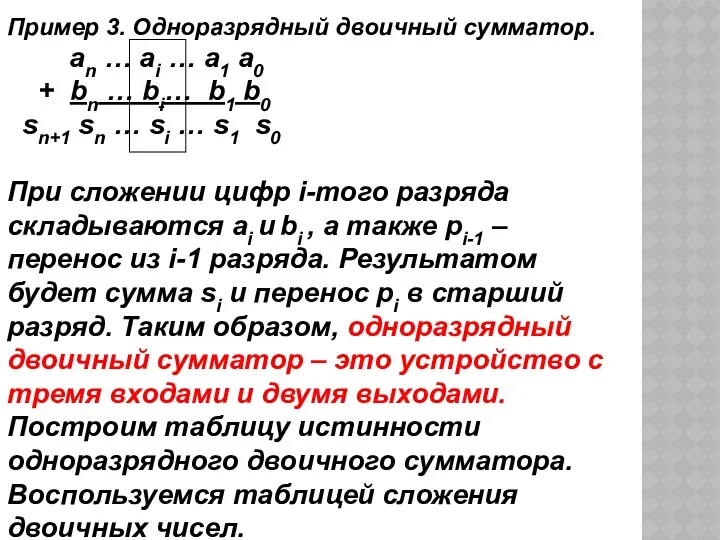

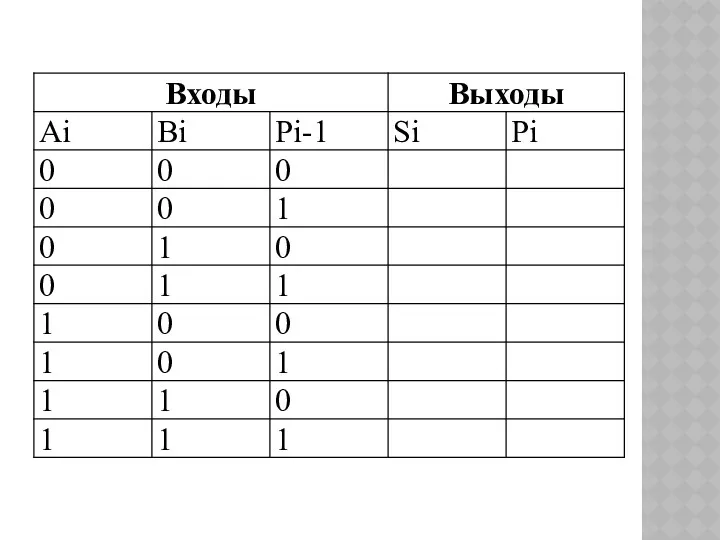

Пример 3. Одноразрядный двоичный сумматор.

an … ai … a1 a0

+ bn … bi… b1 b0

sn+1 sn … si … s1 s0

При сложении цифр i-того разряда складываются ai и bi , а также pi-1 – перенос из i-1 разряда. Результатом будет сумма si и перенос pi в старший разряд. Таким образом, одноразрядный двоичный сумматор – это устройство с тремя входами и двумя выходами.

Построим таблицу истинности одноразрядного двоичного сумматора. Воспользуемся таблицей сложения двоичных чисел.

Слайд 10

Слайд 11

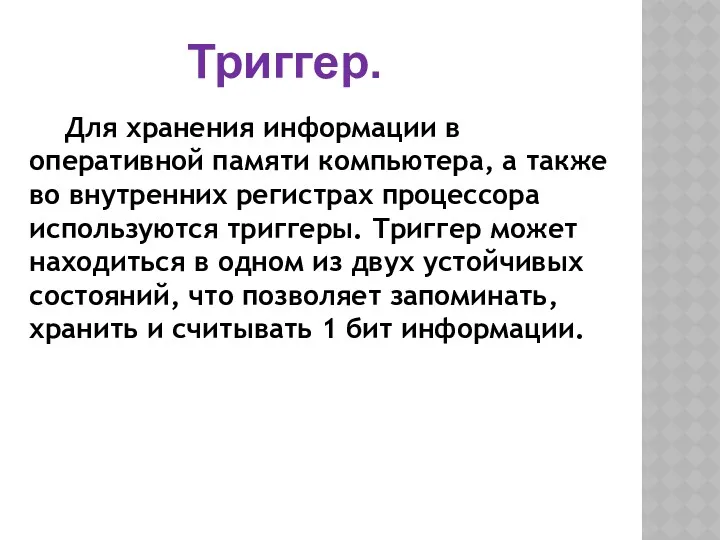

Триггер.

Для хранения информации в оперативной памяти компьютера, а также во внутренних

регистрах процессора используются триггеры. Триггер может находиться в одном из двух устойчивых состояний, что позволяет запоминать, хранить и считывать 1 бит информации.

Слайд 12

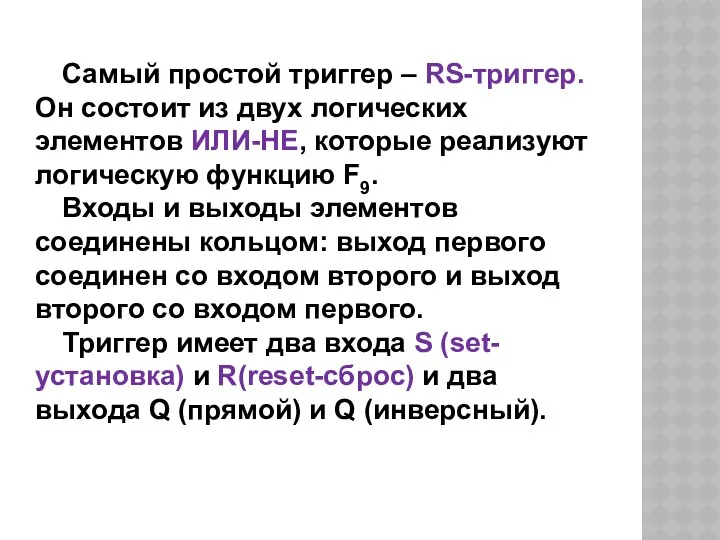

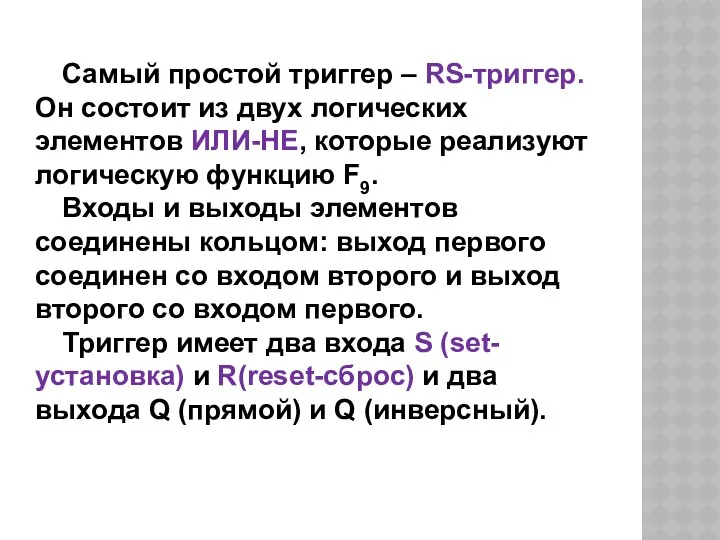

Самый простой триггер – RS-триггер. Он состоит из двух логических элементов

ИЛИ-НЕ, которые реализуют логическую функцию F9.

Входы и выходы элементов соединены кольцом: выход первого соединен со входом второго и выход второго со входом первого.

Триггер имеет два входа S (set-установка) и R(reset-сброс) и два выхода Q (прямой) и Q (инверсный).

Слайд 13

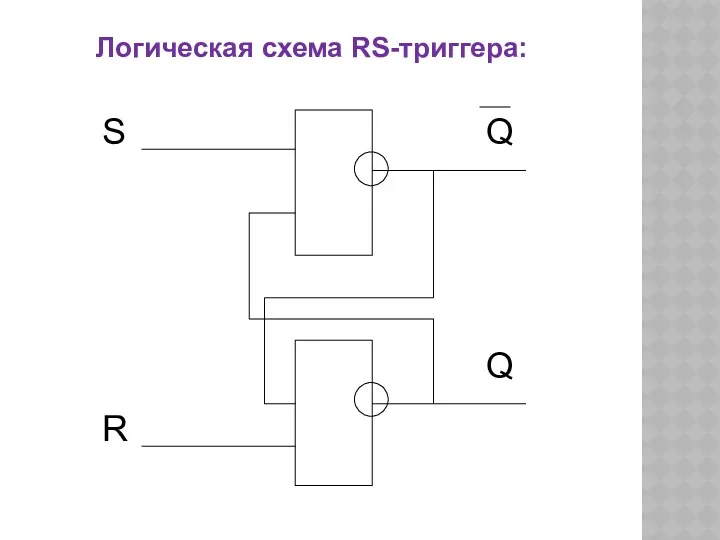

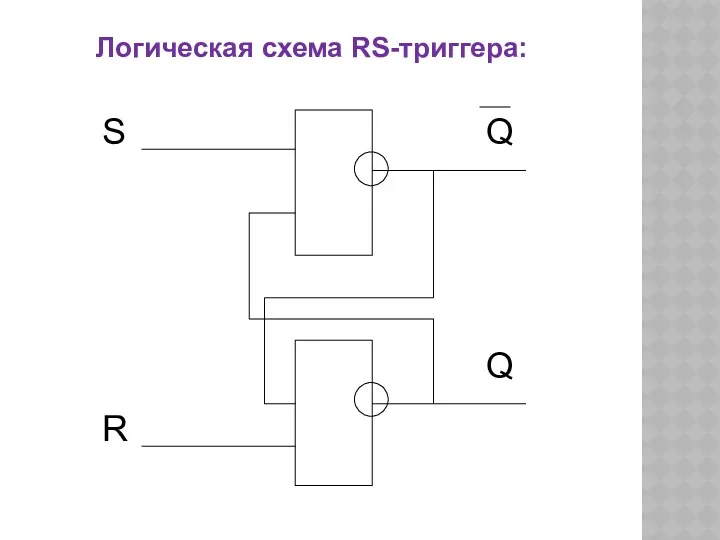

Логическая схема RS-триггера:

Слайд 14

Слайд 15

Автор презентации:

Ширяева Ольга Мухадинновна,

Муниципальное Общеобразовательное Учреждение

«Средняя общеобразовательная школа №2»,

учитель информатики,

1 квалификационной

категории.

http://www.shiryaeva.86sch2-nyagan.edusite.ru

Использование деловой графики для визуализации текстовой информации

Использование деловой графики для визуализации текстовой информации Анализ бизнес-процессов средствами BPwin

Анализ бизнес-процессов средствами BPwin Delphi – язык программирования

Delphi – язык программирования Corel draw бағдарламасымен жұмыс

Corel draw бағдарламасымен жұмыс Презентация Инновационные подходы в образовании

Презентация Инновационные подходы в образовании ГИС технологии в современной картографии

ГИС технологии в современной картографии Линейные и разветвленные алгоритмы. (Лекция 6)

Линейные и разветвленные алгоритмы. (Лекция 6) Презентация к уроку Словесное описание модели

Презентация к уроку Словесное описание модели Защита информации

Защита информации Информатика. Основные понятия информатики (часть 1)

Информатика. Основные понятия информатики (часть 1) Спеціалізовані мови програмування Python

Спеціалізовані мови програмування Python Информационные системы

Информационные системы Основы алгоритмизации и быстрое введение в язык Си

Основы алгоритмизации и быстрое введение в язык Си Библиотека STL. Классы string, vector

Библиотека STL. Классы string, vector Організація та управління базами даних. Зовнішній рівень проектування

Організація та управління базами даних. Зовнішній рівень проектування Понятие как форма мышления

Понятие как форма мышления Язык программирования C#

Язык программирования C# Кодирование информации. Особенности кодирования различных видов информации: текстовой, графической, звуковой

Кодирование информации. Особенности кодирования различных видов информации: текстовой, графической, звуковой Общественное мнение о журналистском сообществе

Общественное мнение о журналистском сообществе Майнкрафт. Викторина

Майнкрафт. Викторина Автоматизация кофейни

Автоматизация кофейни Задачи классификации и регрессии. Технологии обработки данных

Задачи классификации и регрессии. Технологии обработки данных понятие подпрограмм. Механизм реализации подпрограмм с помощью процедур и функций

понятие подпрограмм. Механизм реализации подпрограмм с помощью процедур и функций Книги PascalABC.NET. Современное программирование

Книги PascalABC.NET. Современное программирование Основы связей с общественностью: СМИ, социальные сети

Основы связей с общественностью: СМИ, социальные сети История развития языка программирования С++

История развития языка программирования С++ Контент ВКонтакте для видеокурса ВКонтакте для партнеров

Контент ВКонтакте для видеокурса ВКонтакте для партнеров Состояние и перспективы развития информационных технологий в Республике Беларусь

Состояние и перспективы развития информационных технологий в Республике Беларусь