Содержание

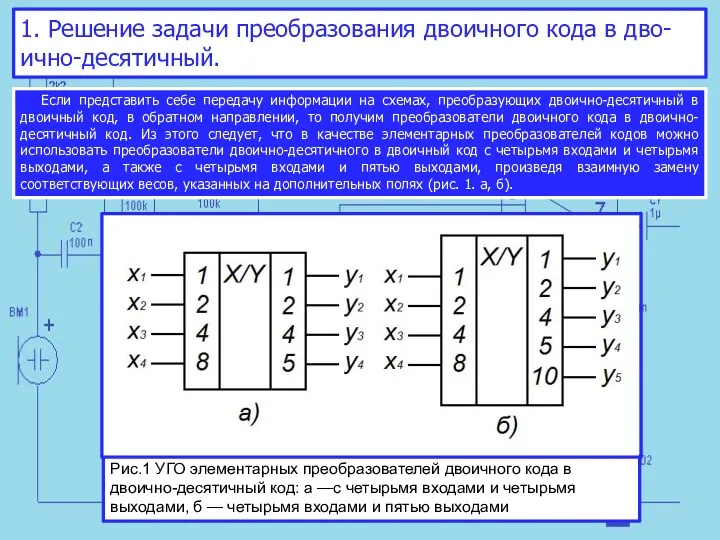

- 2. 1. Решение задачи преобразования двоичного кода в дво-ично-десятичный. Если представить себе передачу информации на схемах, преобразующих

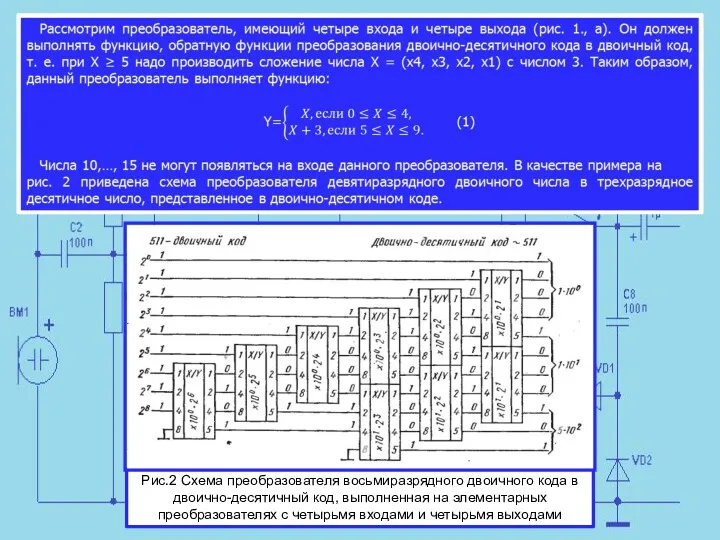

- 3. Рис.2 Схема преобразователя восьмиразрядного двоичного кода в двоично-десятичный код, выполненная на элементарных преобразователях с четырьмя входами

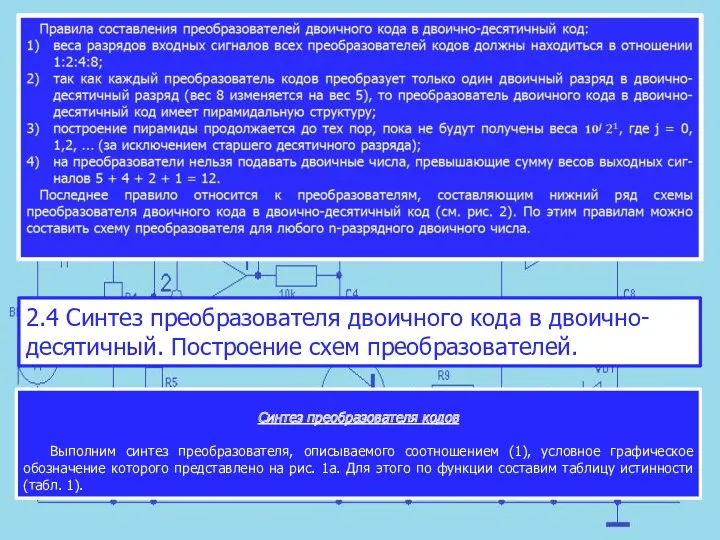

- 4. 2.4 Синтез преобразователя двоичного кода в двоично-десятичный. Построение схем преобразователей. Синтез преобразователя кодов Выполним синтез преобразователя,

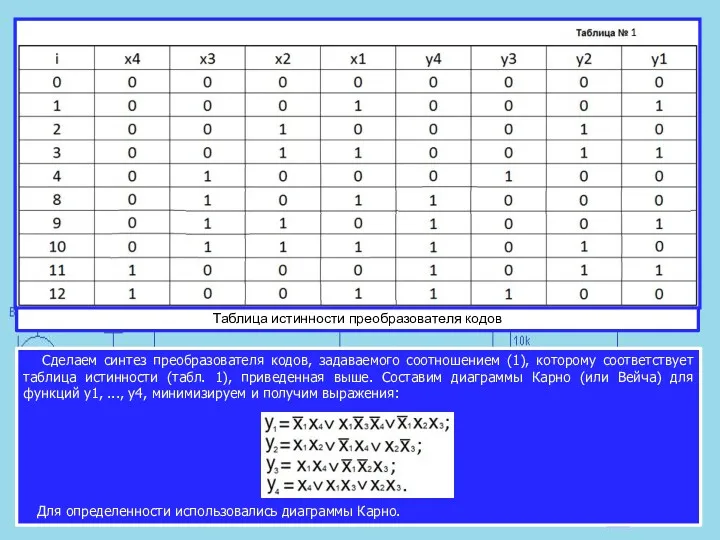

- 5. Таблица истинности преобразователя кодов Сделаем синтез преобразователя кодов, задаваемого соотношением (1), которому соответствует таблица истинности (табл.

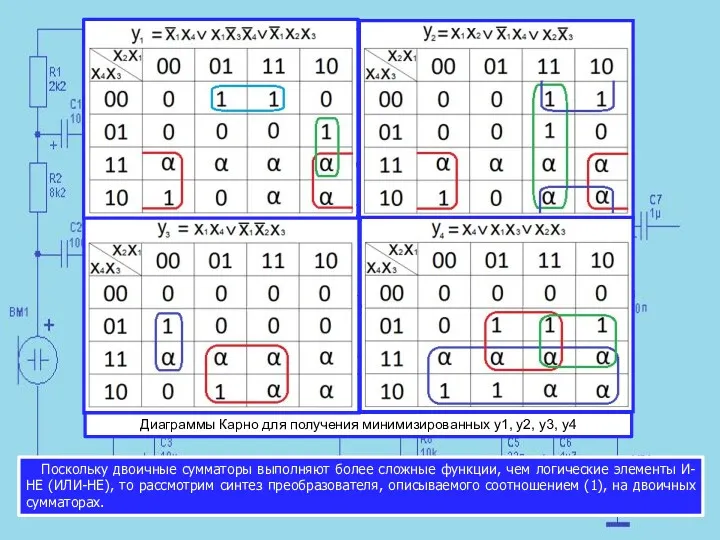

- 6. Диаграммы Карно для получения минимизированных y1, y2, y3, y4 Поскольку двоичные сумматоры выполняют более сложные функции,

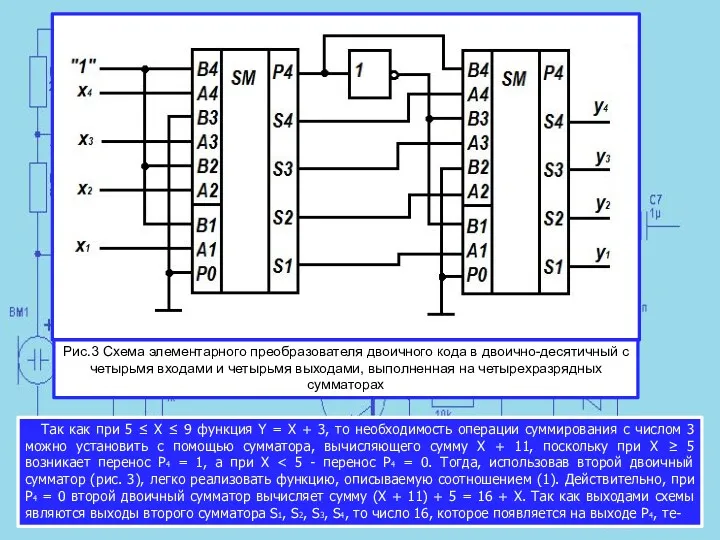

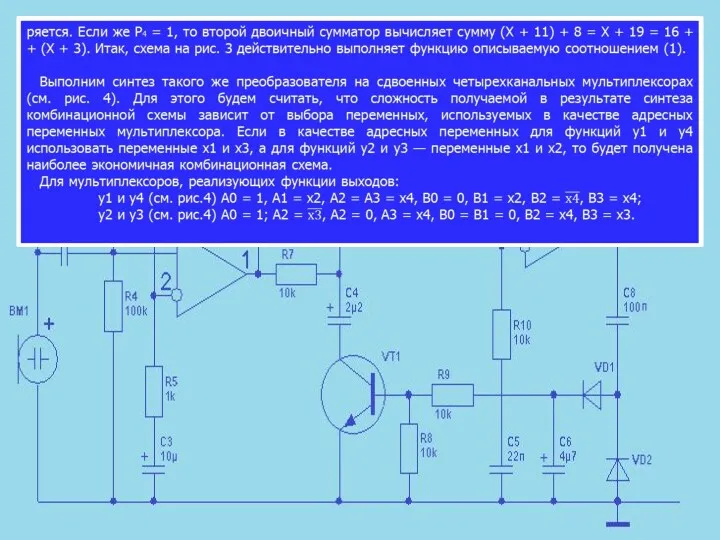

- 7. Рис.3 Схема элементарного преобразователя двоичного кода в двоично-десятичный с четырьмя входами и четырьмя выходами, выполненная на

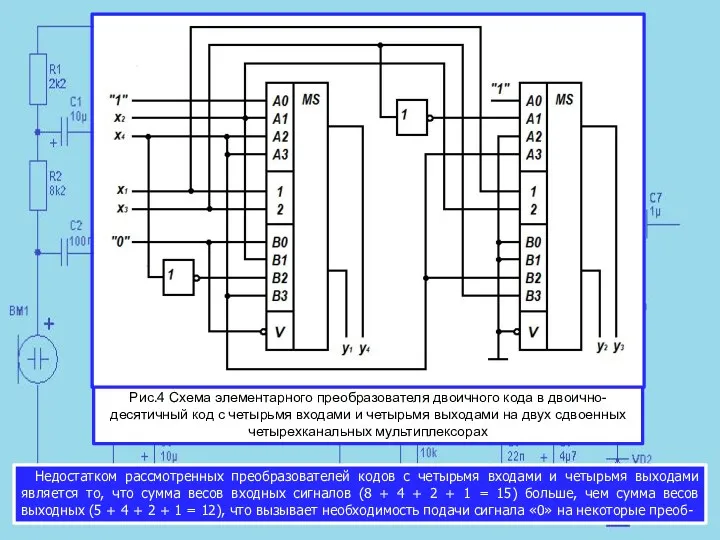

- 9. Рис.4 Схема элементарного преобразователя двоичного кода в двоично-десятичный код с четырьмя входами и четырьмя выходами на

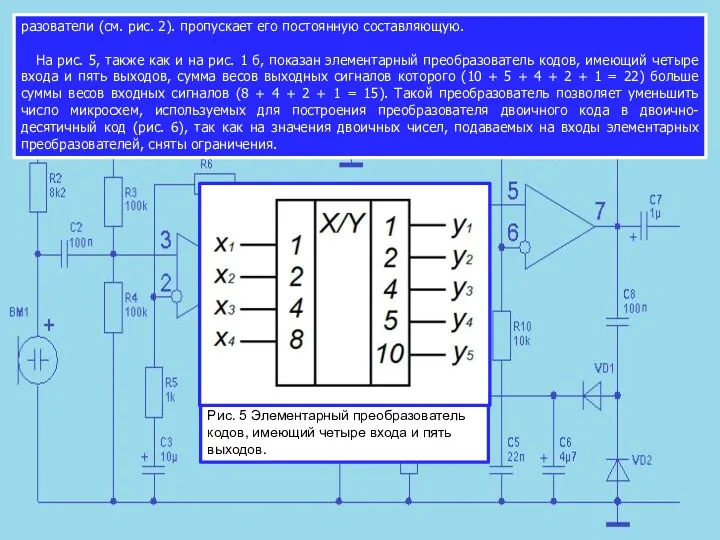

- 10. Рис. 5 Элементарный преобразователь кодов, имеющий четыре входа и пять выходов. разователи (см. рис. 2). пропускает

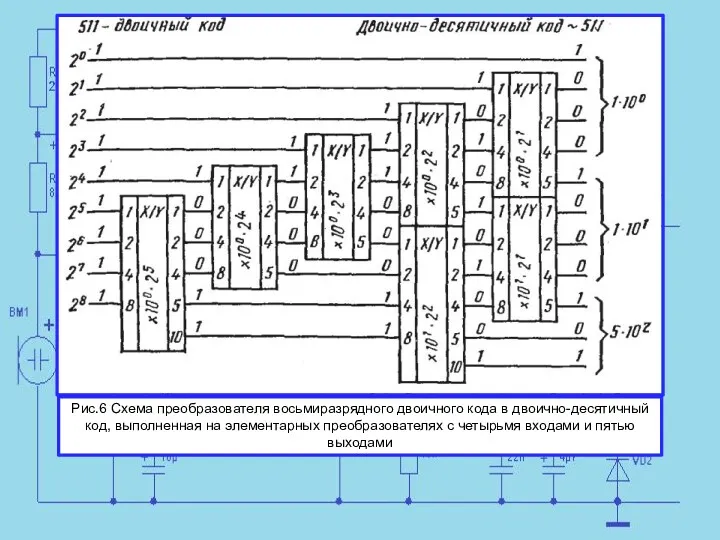

- 11. Рис.6 Схема преобразователя восьмиразрядного двоичного кода в двоично-десятичный код, выполненная на элементарных преобразователях с четырьмя входами

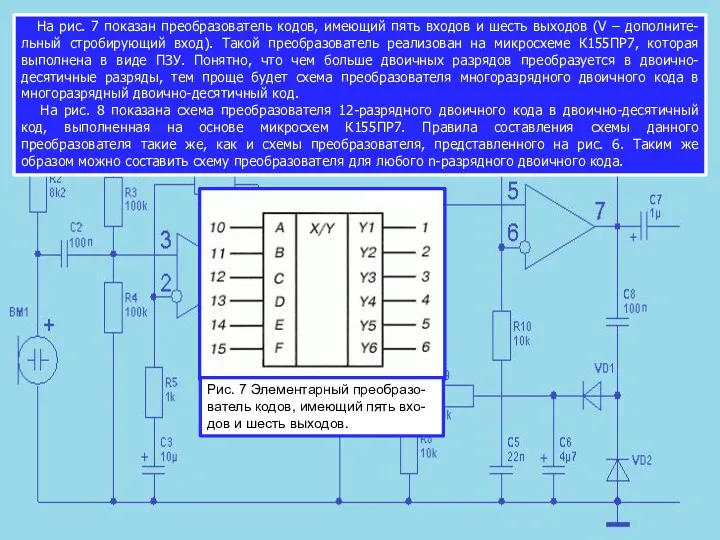

- 12. На рис. 7 показан преобразователь кодов, имеющий пять входов и шесть выходов (V – дополните-льный стробирующий

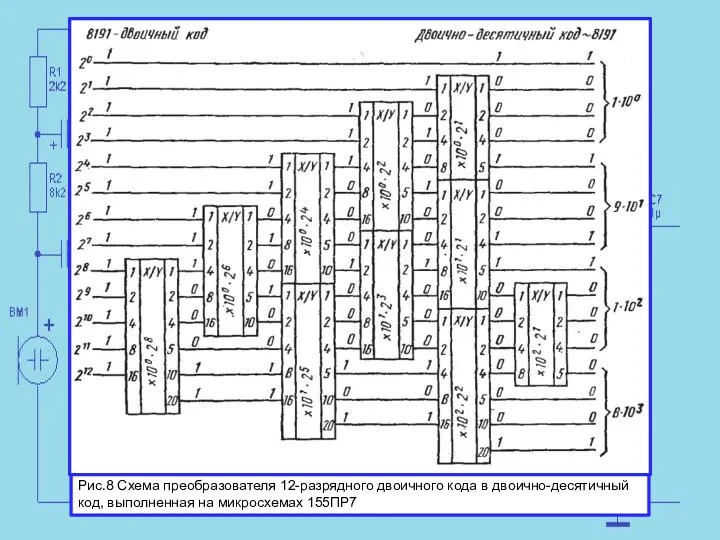

- 13. Рис.8 Схема преобразователя 12-разрядного двоичного кода в двоично-десятичный код, выполненная на микросхемах 155ПР7

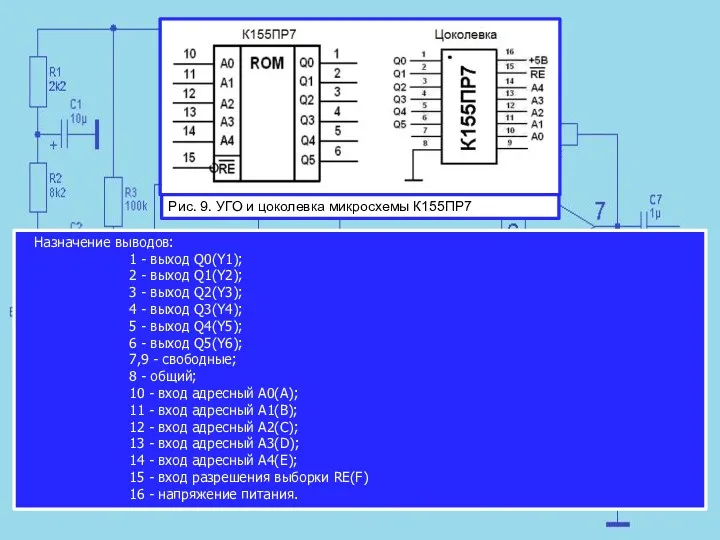

- 14. Назначение выводов: 1 - выход Q0(Y1); 2 - выход Q1(Y2); 3 - выход Q2(Y3); 4 -

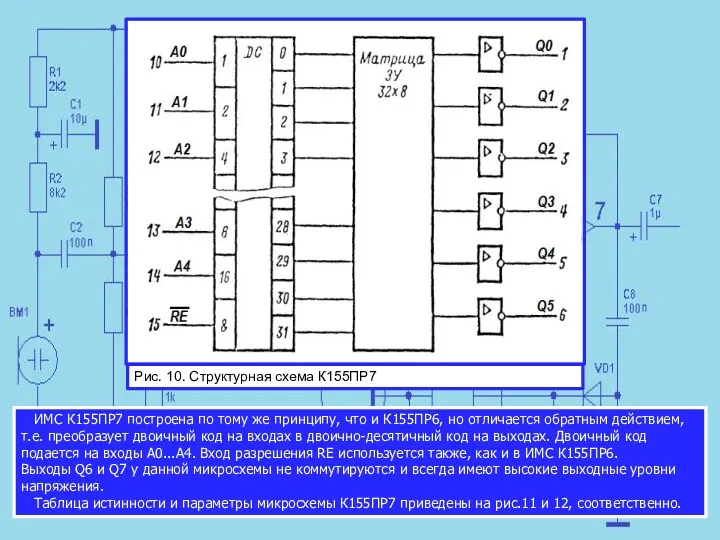

- 15. ИМС К155ПР7 построена по тому же принципу, что и К155ПР6, но отличается обратным действием, т.е. преобразует

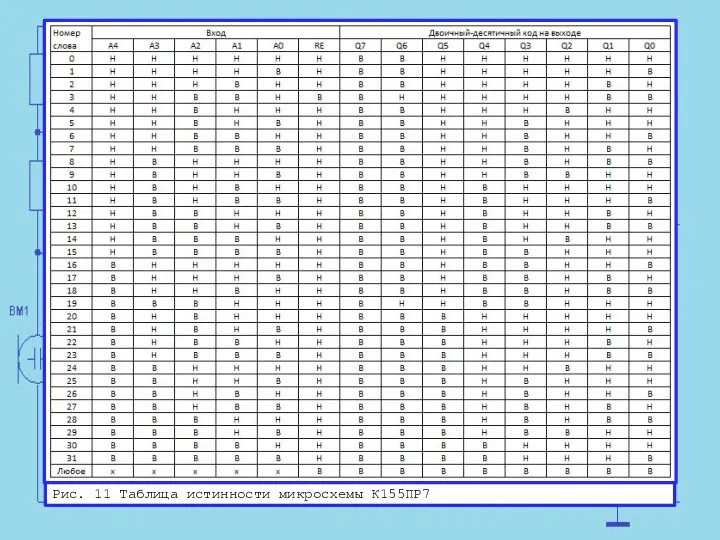

- 16. Рис. 11 Таблица истинности микросхемы К155ПР7

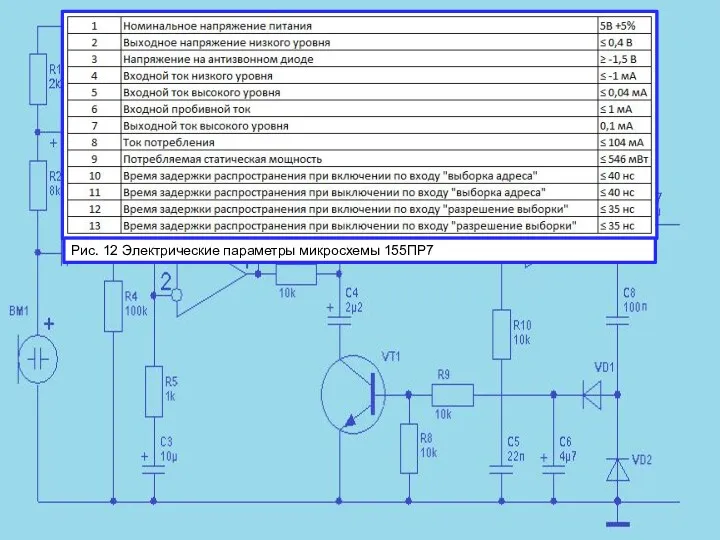

- 17. Рис. 12 Электрические параметры микросхемы 155ПР7

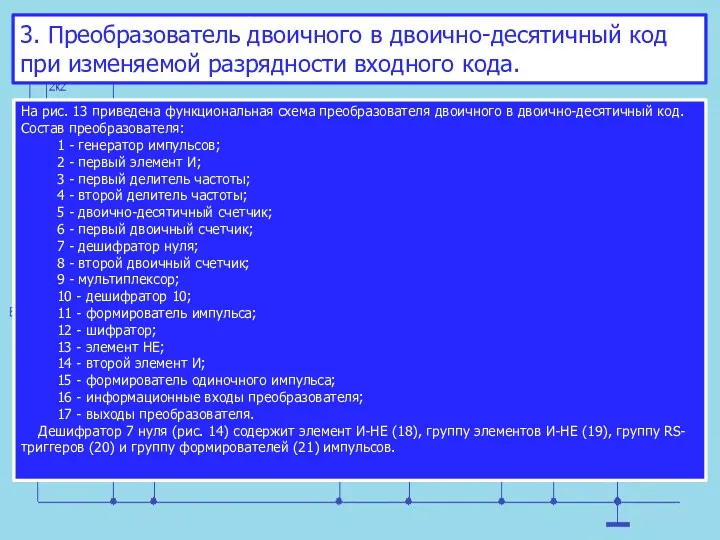

- 18. На рис. 13 приведена функциональная схема преобразователя двоичного в двоично-десятичный код. Состав преобразователя: 1 - генератор

- 19. Рис.13 Функциональная схема преобразователя двоичного в двоично-десятичный код

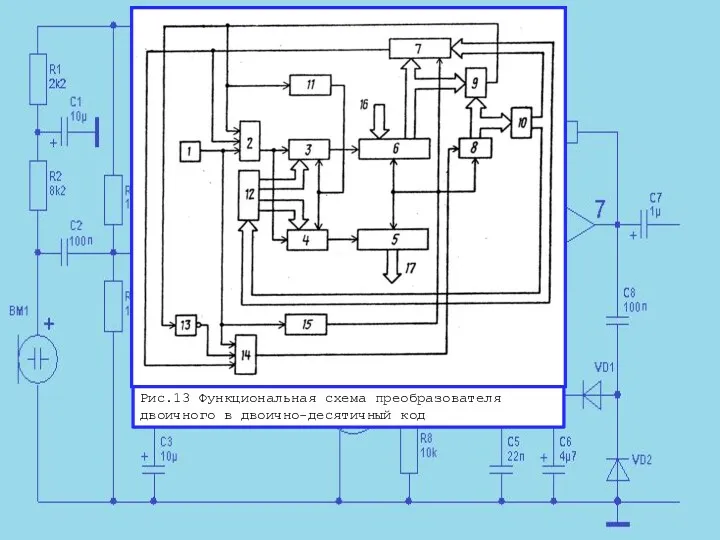

- 20. Работа преобразователя. Генератор импульсов (1) непрерывно вырабатывает последовательность импульсов, которые не проходят через первый элемент И

- 21. выхода делителя (3) частоты поступают в двоичный счетчик (6), работающий на вычитание, а выходные импульсы делителя

- 23. Скачать презентацию

Стандарты жизненного цикла ИС. (Лекция 2)

Стандарты жизненного цикла ИС. (Лекция 2) Методы на языке С#

Методы на языке С# Работа в текстовом процессоре основные приемы редактирования текста

Работа в текстовом процессоре основные приемы редактирования текста Алгоритмы и структуры данных

Алгоритмы и структуры данных Технологии аппаратной виртуализации

Технологии аппаратной виртуализации Операции реляционной алгебры

Операции реляционной алгебры Графический редактор Paint. Приемы создания и обработки графических изображений

Графический редактор Paint. Приемы создания и обработки графических изображений Умный контент

Умный контент Основы работы с Docker

Основы работы с Docker Игровая среда программирования Scratch

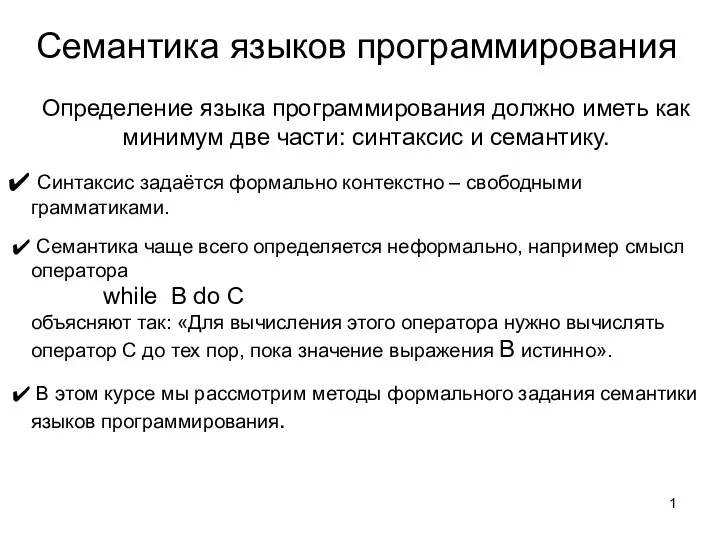

Игровая среда программирования Scratch Семантика языков программирования

Семантика языков программирования Открытый урок по теме компьютерная графика

Открытый урок по теме компьютерная графика Презантация по информатике Моделирование как метод познания

Презантация по информатике Моделирование как метод познания С++. История языка Си++

С++. История языка Си++ Системы, модели, графы. Построение информационной модели в виде графа. 8 класс

Системы, модели, графы. Построение информационной модели в виде графа. 8 класс Введение в Django

Введение в Django Логічні операції в мові С

Логічні операції в мові С Основные принципы построения и применения CПО МПС

Основные принципы построения и применения CПО МПС Логические величины, операции, выражения

Логические величины, операции, выражения Графические информационные модели

Графические информационные модели База данных в мини-отеле Флёр

База данных в мини-отеле Флёр Cтандартные телеграммы при обслуживании рейса

Cтандартные телеграммы при обслуживании рейса Організація класів і особливості роботи з об'єктами (тема 12)

Організація класів і особливості роботи з об'єктами (тема 12) Компьютерные вирусы и антивирусные программы

Компьютерные вирусы и антивирусные программы Проектирование и реализация дизайн-макета кинотеатра

Проектирование и реализация дизайн-макета кинотеатра Разработка мобильного приложения Квест по УрФУ в дополненной реальности

Разработка мобильного приложения Квест по УрФУ в дополненной реальности Особенности организации защиты информации на предприятии

Особенности организации защиты информации на предприятии Человеко-машинное взаимодействие. XML и QT

Человеко-машинное взаимодействие. XML и QT