Содержание

- 2. Политики замещения данных в кэшпамяти Random LFU (Least Frequently Used) LRU (Least Recently Used) LRR (Least

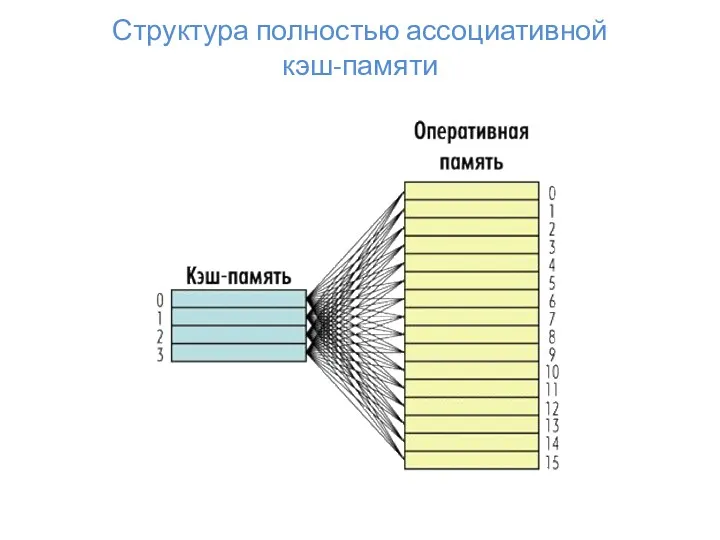

- 3. Структура полностью ассоциативной кэш-памяти

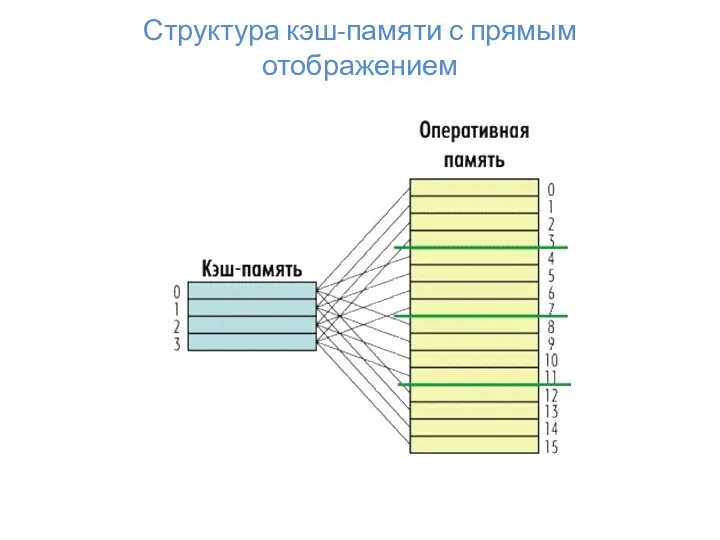

- 4. Структура кэш-памяти с прямым отображением

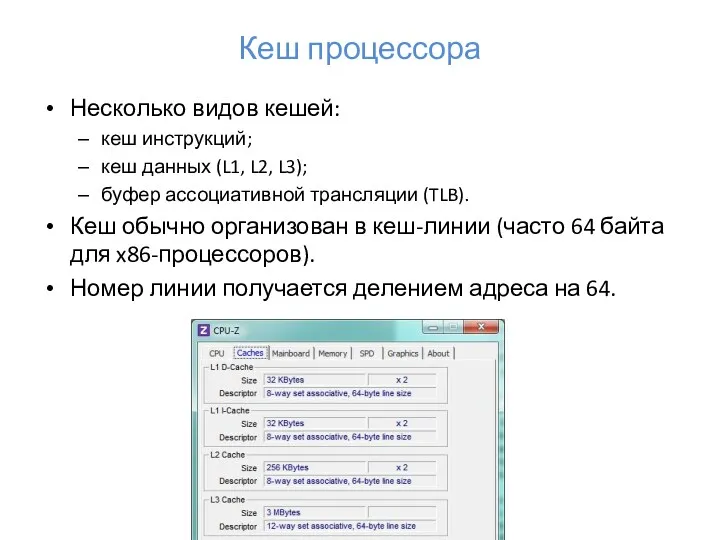

- 5. Кеш процессора Несколько видов кешей: кеш инструкций; кеш данных (L1, L2, L3); буфер ассоциативной трансляции (TLB).

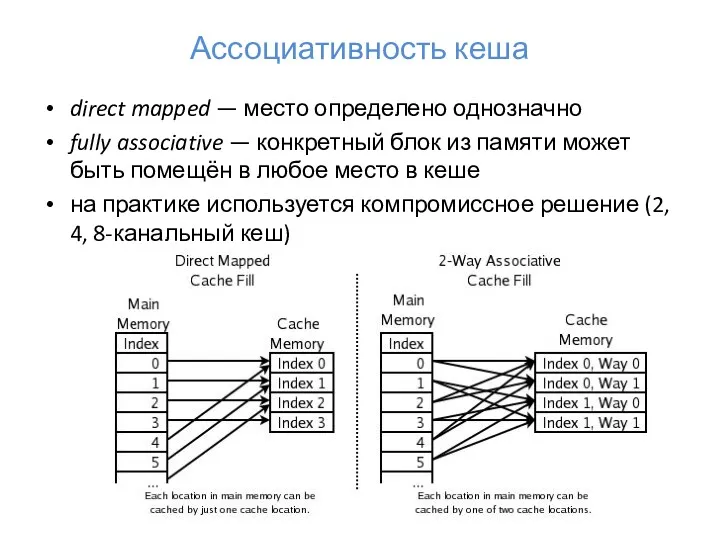

- 6. Ассоциативность кеша direct mapped — место определено однозначно fully associative — конкретный блок из памяти может

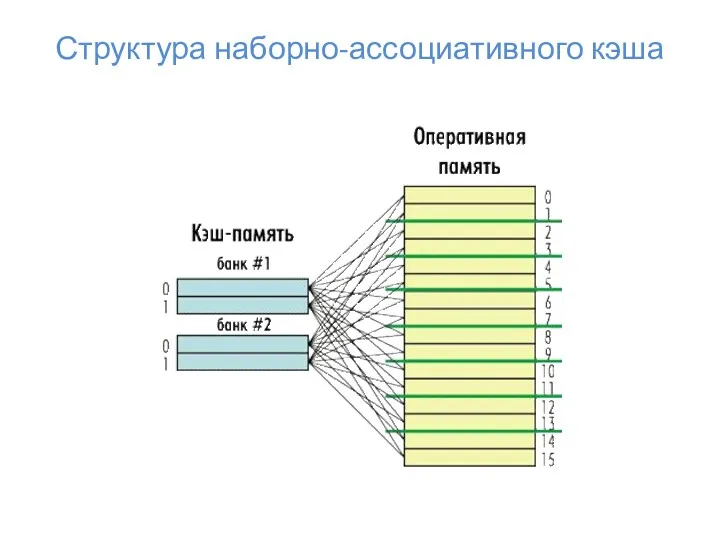

- 7. Структура наборно-ассоциативного кэша

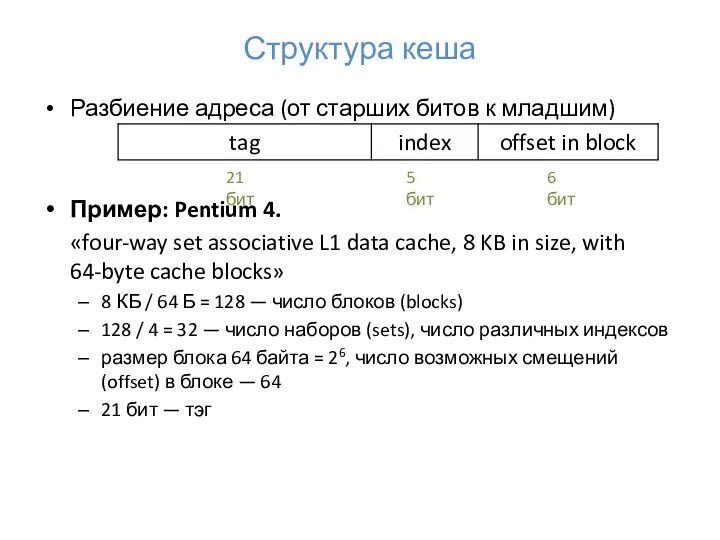

- 8. Структура кеша Разбиение адреса (от старших битов к младшим) Пример: Pentium 4. «four-way set associative L1

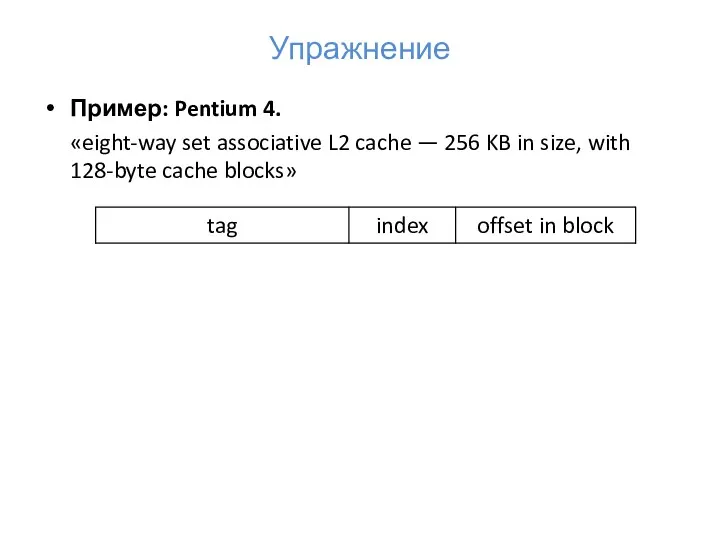

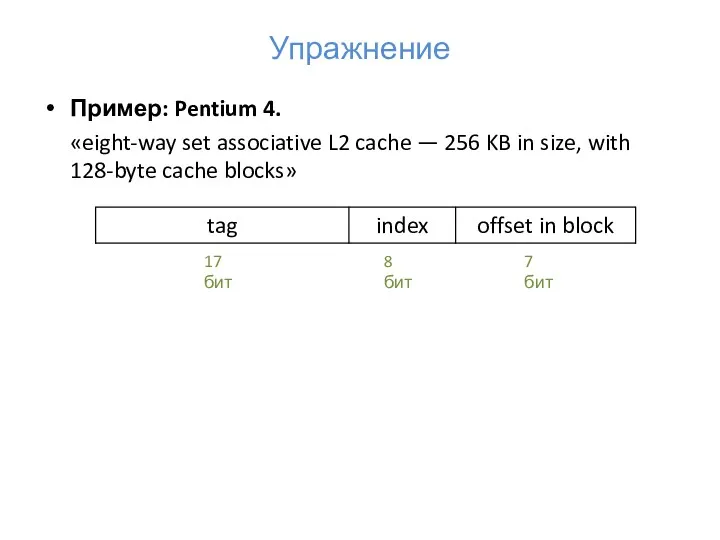

- 9. Упражнение Пример: Pentium 4. «eight-way set associative L2 cache — 256 KB in size, with 128-byte

- 10. Упражнение Пример: Pentium 4. «eight-way set associative L2 cache — 256 KB in size, with 128-byte

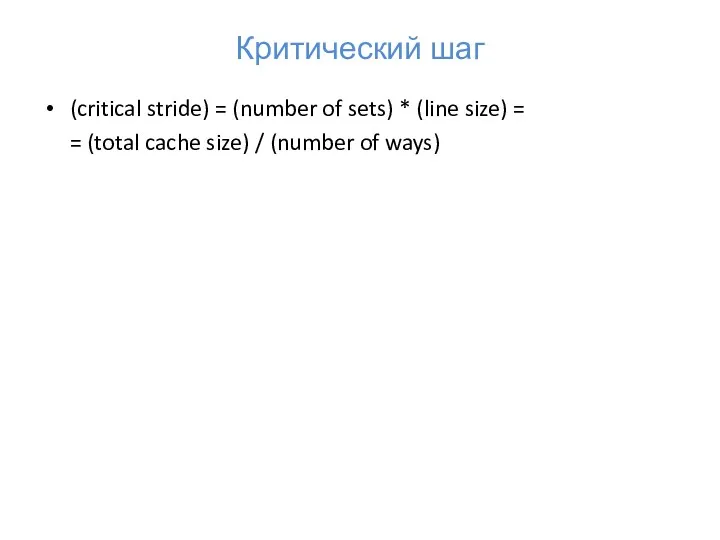

- 11. Критический шаг (critical stride) = (number of sets) * (line size) = = (total cache size)

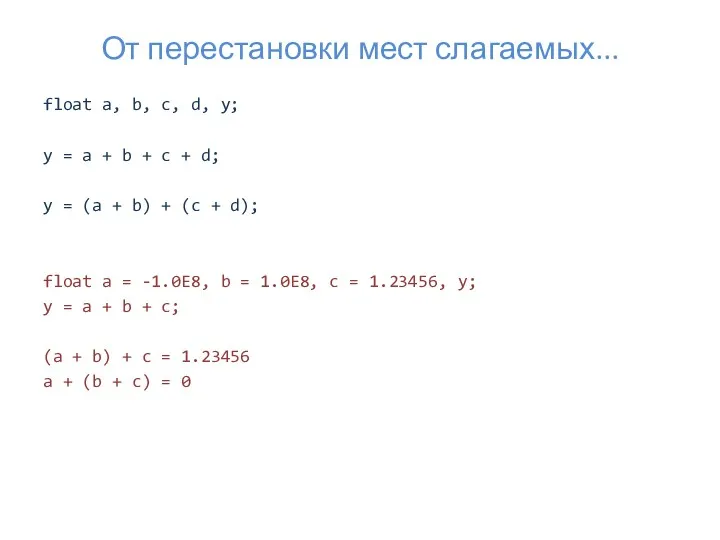

- 12. От перестановки мест слагаемых... float a, b, c, d, y; y = a + b +

- 13. Автоматическая векторизация const int size = 1024; int a[size], b[size]; // ... for (int i =

- 14. Задача транспонирования матрицы void transpose(double a[SIZE][SIZE]) { int r, c; double temp; for (r = 1;

- 16. Скачать презентацию

![Автоматическая векторизация const int size = 1024; int a[size], b[size];](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/288041/slide-12.jpg)

![Задача транспонирования матрицы void transpose(double a[SIZE][SIZE]) { int r, c;](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/288041/slide-13.jpg)

Создание документов в текстовых редакторах. Форматирование документов в текстовых редакторах.

Создание документов в текстовых редакторах. Форматирование документов в текстовых редакторах. Спутниковые радионавигационные системы. (Тема 3)

Спутниковые радионавигационные системы. (Тема 3) Что такое интернет

Что такое интернет Реформа перехода на новый порядок применения кассовой техники для сферы жилищно-коммунального хозяйства

Реформа перехода на новый порядок применения кассовой техники для сферы жилищно-коммунального хозяйства Як захистити себе від атак хакерів

Як захистити себе від атак хакерів FLEX Application Instructions Program Year 2018-2019

FLEX Application Instructions Program Year 2018-2019 Серверная разработка ПО. Лабораторная работа №3

Серверная разработка ПО. Лабораторная работа №3 Принципы разработки тестов

Принципы разработки тестов Урок Безопасность в интернете

Урок Безопасность в интернете Selenium RC

Selenium RC Задание 19, ОГЭ по информатике

Задание 19, ОГЭ по информатике Развитие музеев. Конец 20, начало 21 века

Развитие музеев. Конец 20, начало 21 века Different types of operating system

Different types of operating system Інформаційні характеристики каналів зв'язку

Інформаційні характеристики каналів зв'язку Составление тестовых заданий с использованием системы программ MyTest X

Составление тестовых заданий с использованием системы программ MyTest X Презентации к уроку информатики в 3 классе по теме Объект

Презентации к уроку информатики в 3 классе по теме Объект Электронная почта

Электронная почта Наследование. Лекция 2.1

Наследование. Лекция 2.1 Информационная безопасность. Пассивный вид атаки

Информационная безопасность. Пассивный вид атаки Snort. Система обнаружения атак

Snort. Система обнаружения атак Разработка программы по шифрованию осмысленного текста

Разработка программы по шифрованию осмысленного текста Информационная безопасность. Методы защиты информации

Информационная безопасность. Методы защиты информации Режимы и способы обработки данных

Режимы и способы обработки данных Информация измерение

Информация измерение Editing Slides With Polaris Office

Editing Slides With Polaris Office Урок Своя игра по информатике

Урок Своя игра по информатике Реляционная алгебра

Реляционная алгебра Разработка ГОСТ и СП для информационного моделирования в строительстве

Разработка ГОСТ и СП для информационного моделирования в строительстве