Содержание

- 2. Основными техническими параметрами сумматоров являются: аппаратная сложность и быстродействие и поэтому имеется огромное множество вариантов сумматоров,

- 3. Выделяя главные моменты, остановимся лишь на некоторых из них. 1) одноразрядный сумматор 2)полные сумматоры 3)полусумматоры 4)четвертьсумматоры

- 4. Одноразрядный сумматор Он имеет три входа (2 слагаемых и перенос из предыдущего разряда) и 2 выхода

- 5. Полные сумматоры тринарные (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием трёх входов, на которые

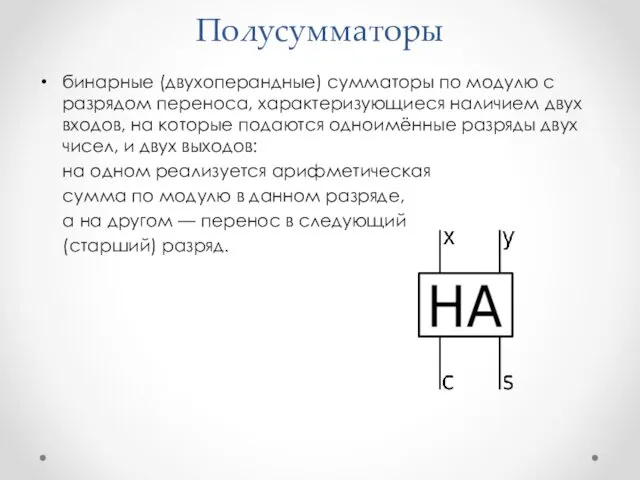

- 6. Полусумматоры бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух входов, на которые подаются

- 7. Четвертьсумматоры бинарные (двухоперандные) сумматоры по модулю без разряда переноса, характеризующиеся наличием двух входов, на которые подаются

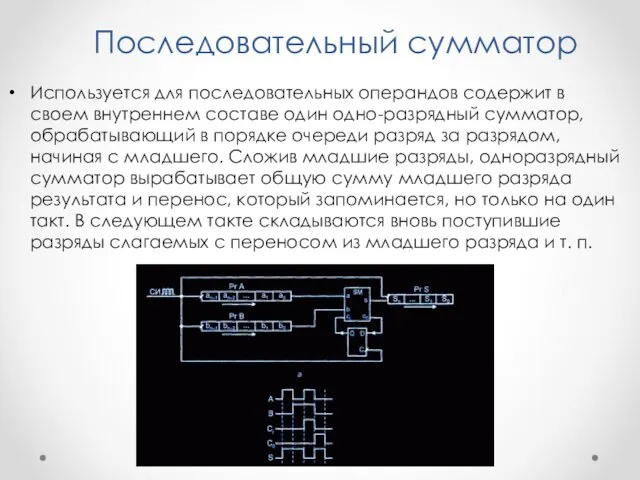

- 8. Последовательный сумматор Используется для последовательных операндов содержит в своем внутреннем составе один одно-разрядный сумматор, обрабатывающий в

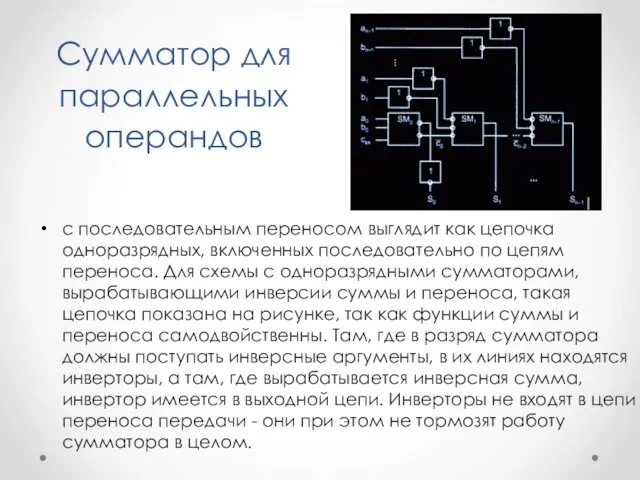

- 9. Сумматор для параллельных операндов с последовательным переносом выглядит как цепочка одноразрядных, включенных последовательно по цепям переноса.

- 10. Параллельный сумматор с параллельным переносом Разработан специально для получения наилучшего быстродействия. Концепция к решению этой многоходовки

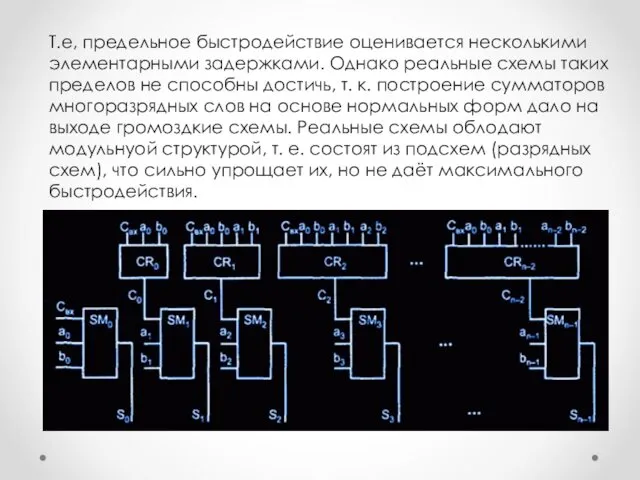

- 11. Т.е, предельное быстродействие оценивается несколькими элементарными задержками. Однако реальные схемы таких пределов не способны достичь, т.

- 12. Сумматор с передачей сигнала переноса по цепочке замкнутых ключей. Среди компромиссных вариантов существующих сумматоров, занимающих промежуточное

- 13. Сумматор с условным переносом Давно известная структура, которая чуть раньше не нашла широкого использования, но сейчас

- 14. Накапливающий снабжённый собственной внутренней памятью. схема, суммирующая поочередно поступающие на ее вход цифры слагаемого и переноса

- 16. Скачать презентацию

Умножение десятичных дробей

Умножение десятичных дробей Тест по теме: Теорема Пифагора

Тест по теме: Теорема Пифагора Стереометрия. Основные понятия и аксиомы стереометрии

Стереометрия. Основные понятия и аксиомы стереометрии Действия с десятичными дробями

Действия с десятичными дробями Степенева функція (урок, 10 клас)

Степенева функція (урок, 10 клас) Сложение и вычитание вида 26±10

Сложение и вычитание вида 26±10 ОП-213 10.04

ОП-213 10.04 Высшая математика. Глава 1. Элементы линейной алгебры. Матрицы и определители

Высшая математика. Глава 1. Элементы линейной алгебры. Матрицы и определители Задача 6 стр.103

Задача 6 стр.103 Занимательная математика для детей

Занимательная математика для детей Методы решения тригонометрических уравнений. 10 класс

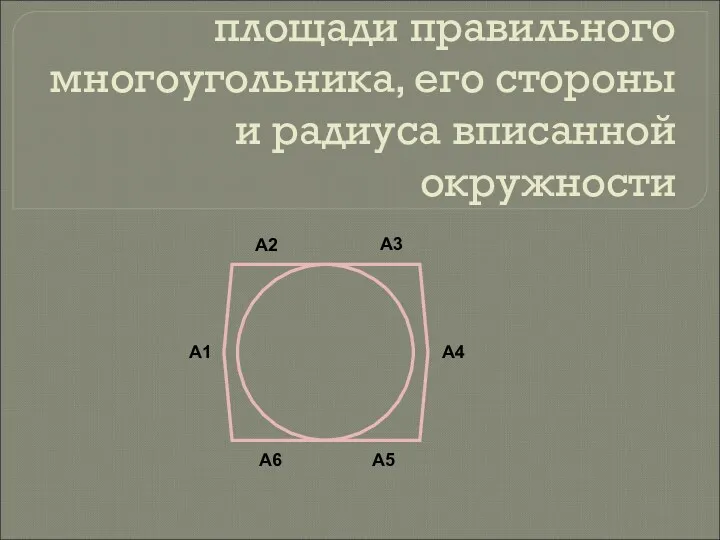

Методы решения тригонометрических уравнений. 10 класс Формулы для вычисления площади правильного многоугольника, его стороны и радиуса вписанной окружности

Формулы для вычисления площади правильного многоугольника, его стороны и радиуса вписанной окружности Различные методы решения неравенств. Общие методы решения неравенств

Различные методы решения неравенств. Общие методы решения неравенств Приближенное построение правильных многоугольников с помощью циркуля и линейки. Учебно-методические пособие

Приближенное построение правильных многоугольников с помощью циркуля и линейки. Учебно-методические пособие Дискретная математика. Множества

Дискретная математика. Множества Презентация Фольклорные задачи в математике

Презентация Фольклорные задачи в математике Уравнение касательной. 10 класс

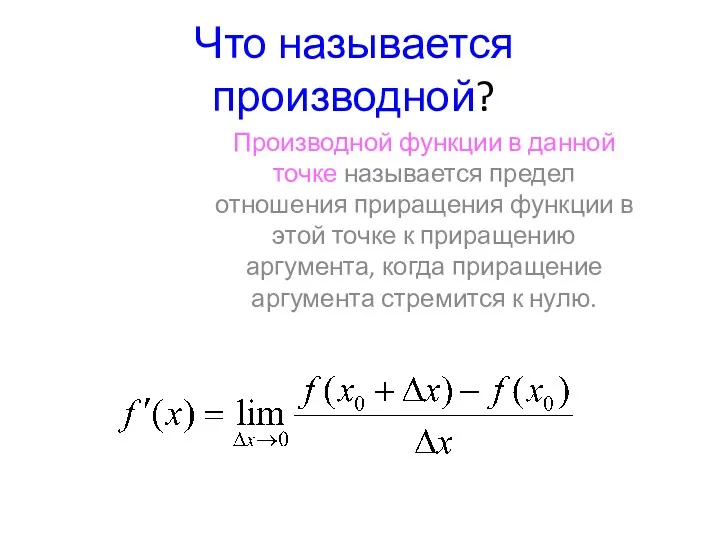

Уравнение касательной. 10 класс մաթեմատիկա

մաթեմատիկա задачи для устного счета в стихах

задачи для устного счета в стихах Порівняння задач на пропорційне ділення. Ділення з остачею на круглі числа. Вирази на порядок виконання дій

Порівняння задач на пропорційне ділення. Ділення з остачею на круглі числа. Вирази на порядок виконання дій компьютерная математическая игра Куда плывёт кораблик? (1-2 класс)

компьютерная математическая игра Куда плывёт кораблик? (1-2 класс) Таблица умножения на 4

Таблица умножения на 4 Функция. Графики функций

Функция. Графики функций Тренажёры Таблица умножения и деления Диск

Тренажёры Таблица умножения и деления Диск Решение неравенств, содержащих модуль

Решение неравенств, содержащих модуль Задачи по комбинаторике

Задачи по комбинаторике Многомерная линейная регрессия

Многомерная линейная регрессия Приближенные значения действительных чисел

Приближенные значения действительных чисел