Содержание

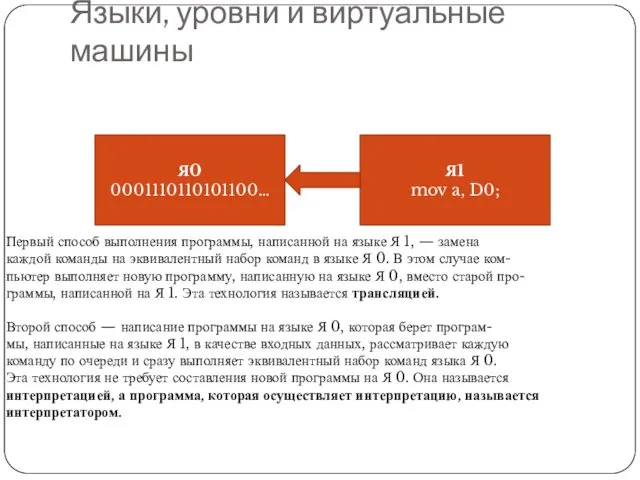

- 2. Языки, уровни и виртуальные машины Я0 0001110110101100… Я1 mov a, D0; Первый способ выполнения программы, написанной

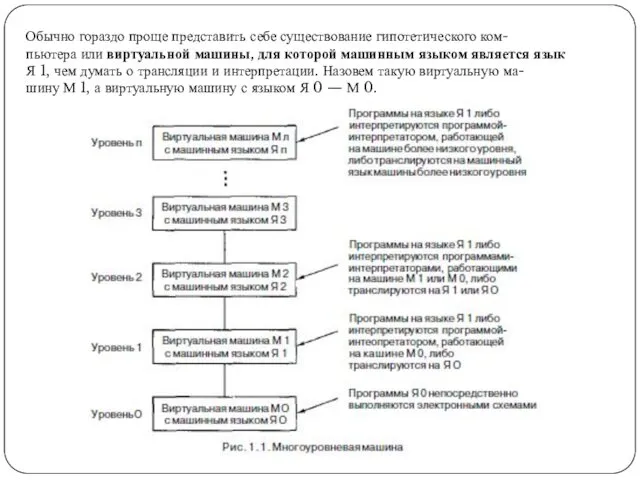

- 3. Обычно гораздо проще представить себе существование гипотетического ком- пьютера или виртуальной машины, для которой машинным языком

- 4. Между языком и виртуальной машиной существует важная зависимость. У каж- дой машины есть какой-то определенный машинный

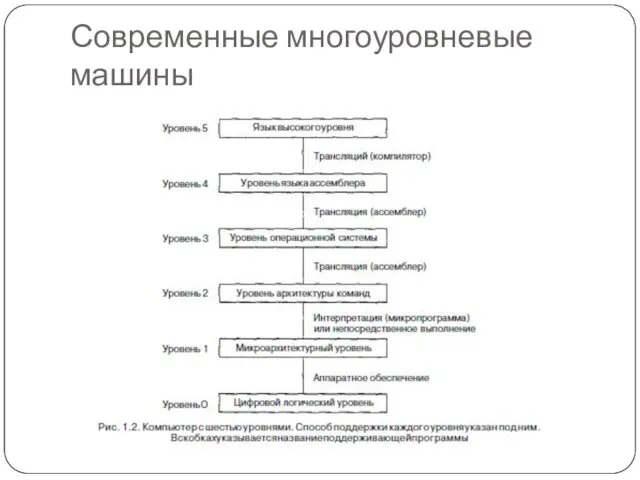

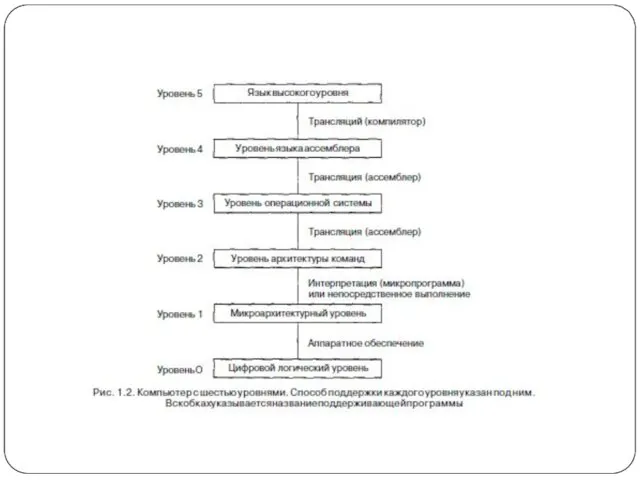

- 5. Современные многоуровневые машины

- 6. Уровень 0 Уровень 0 — аппаратное обеспечение машины. Его электронные схемы выполняют программы, написанные на языке

- 7. Уровень 1 Следующий уровень — микроархитектурный уровень. На этом уровне можно видеть совокупности 8 или 32

- 8. Уровень 2 Второй уровень мы будем называть уровнем архитектуры системы команд. Каждый производитель публикует руководство для

- 9. Уровень 3 Следующий уровень обычно гибридный. Большинство команд в его языке есть также и на уровне

- 10. Уровень 4 Между третьим и четвертым уровнями есть существенная разница. Нижние три уровня конструируются не для

- 11. Уровень 5 Пятый уровень обычно состоит из языков, разработанных для прикладных про- граммистов. Такие языки называются

- 13. Процессоры

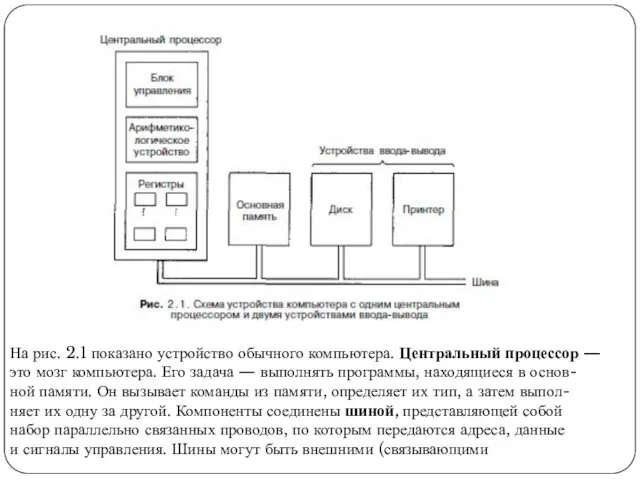

- 14. На рис. 2.1 показано устройство обычного компьютера. Центральный процессор — это мозг компьютера. Его задача —

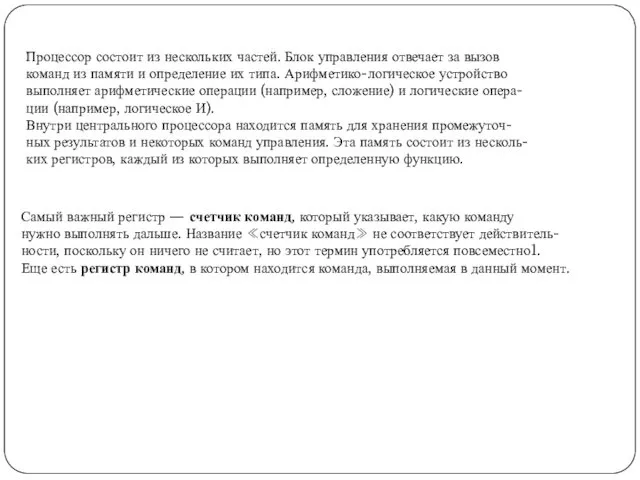

- 15. Процессор состоит из нескольких частей. Блок управления отвечает за вызов команд из памяти и определение их

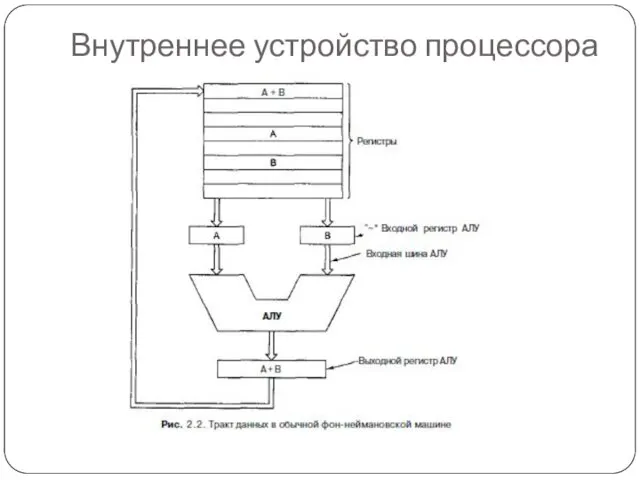

- 16. Внутреннее устройство процессора

- 17. Выполнение команд Центральный процессор выполняет каждую команду за несколько шагов: 1) вызывает следующую команду из памяти

- 18. Микропрограммирование Первые компьютеры содержали небольшое количество команд, и эти команды были простыми. Но поиски более мощных

- 19. Но как построить дешевый компьютер, который будет выполнять все сложные команды, предназначенные для высокоэффективных дорогостоящих машин?

- 20. RISC и CISC RISC — это сокращение от Reduced Instruction Set Computer — компьютер с сокращенным

- 21. Принципы современных архитектур Все команды непосредственно выполняются аппаратным обеспечением. Компьютер должен начинать выполнение большого числа команд.

- 22. Кэширование Уже много лет известно, что главным препятствием высокой скорости выполне- ния команд является их вызов

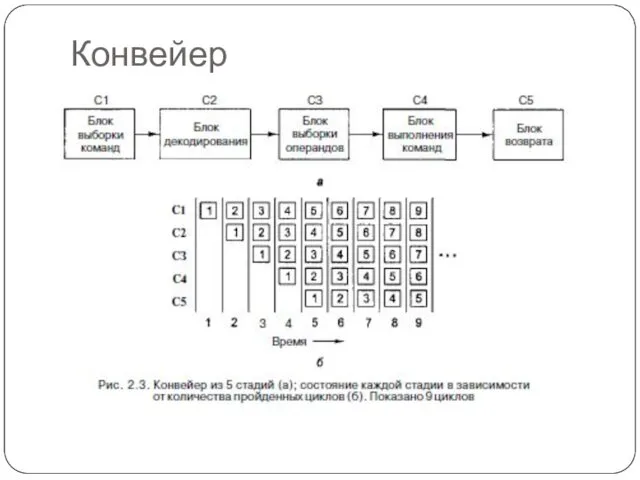

- 23. Конвейер

- 24. На рис. 2.3, б мы видим, как действует конвейер во времени. Во время цикла 1 стадия

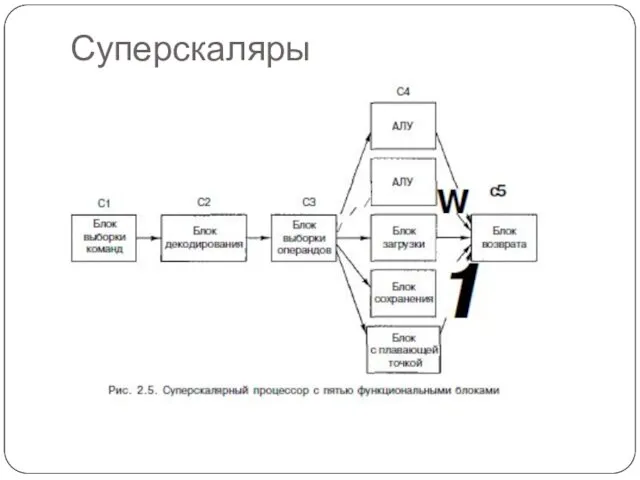

- 25. Суперскаляры

- 26. Векторный компьютер Массивно-параллельный процессор (array processor) состоит из большого числа сходных процессоров, которые выполняют одну и

- 28. Скачать презентацию

Ливень. Азбука рисования

Ливень. Азбука рисования Гармония любви

Гармония любви Теоретическая грамматика английского языка. Артикль

Теоретическая грамматика английского языка. Артикль Классный час Толерантность – путь к миру.

Классный час Толерантность – путь к миру. Межотраслевые комплексы. Чёрная и цветная металлургия России

Межотраслевые комплексы. Чёрная и цветная металлургия России Бизнес. Как управлять своим доходом. Сибирское здоровье

Бизнес. Как управлять своим доходом. Сибирское здоровье Тема урока: Коробка

Тема урока: Коробка Повышение эффективности разработки залежи нефти в отложениях бобриковского объекта Троельжанского месторождения

Повышение эффективности разработки залежи нефти в отложениях бобриковского объекта Троельжанского месторождения Нептун - восьмая планета от Солнца

Нептун - восьмая планета от Солнца Алгоритмические структуры языка Basic

Алгоритмические структуры языка Basic Нормы устройства стрелочных переводов и глухих пересечений

Нормы устройства стрелочных переводов и глухих пересечений Киберспорт в России и СНГ: история, текущее состояние и перспективы

Киберспорт в России и СНГ: история, текущее состояние и перспективы Новые пространственные концепции (продолжение). Тема 2

Новые пространственные концепции (продолжение). Тема 2 Презентация практической работы по химии 8 класс Очистка поваренной соли

Презентация практической работы по химии 8 класс Очистка поваренной соли Самарская область прошлое и настоящее. Народы Самарской губернии

Самарская область прошлое и настоящее. Народы Самарской губернии Клиническое проявление и диагностика инфекционных заболеваний слизистой ротовой полости

Клиническое проявление и диагностика инфекционных заболеваний слизистой ротовой полости Реализация в Кировской области проекта Народный бюджет

Реализация в Кировской области проекта Народный бюджет Яндекс Директ. Как получать клиентов, а не клики 2.0

Яндекс Директ. Как получать клиентов, а не клики 2.0 Суперкомпьютеры

Суперкомпьютеры База поддержки морских операций. Схема организации территории ТОО Батыс Мунай Транс

База поддержки морских операций. Схема организации территории ТОО Батыс Мунай Транс Асновы кіравання інтэлектуальнай уласнасцю

Асновы кіравання інтэлектуальнай уласнасцю Курить - здоровью вредить

Курить - здоровью вредить О беспозвоночных животных Калужской области

О беспозвоночных животных Калужской области Europejski Bank Centralny

Europejski Bank Centralny Специальная теория относительности. Относительность одновременности. Постулаты Эйнштейна

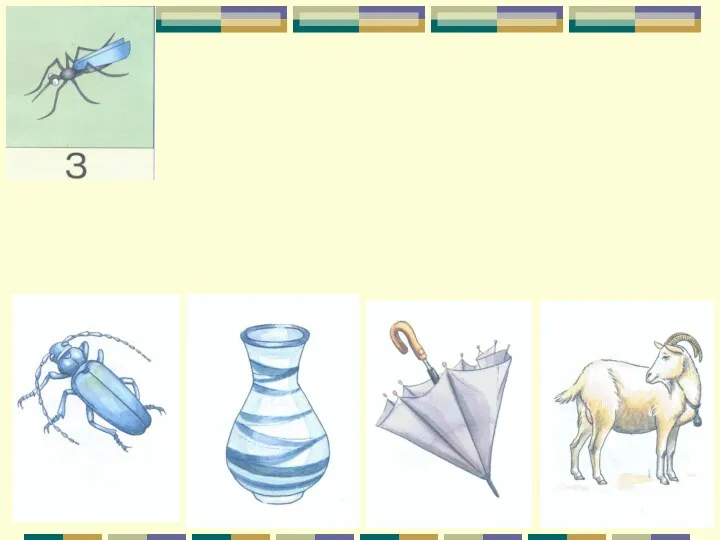

Специальная теория относительности. Относительность одновременности. Постулаты Эйнштейна дифференциация з -ж Диск

дифференциация з -ж Диск Робот пылесос VR5901LVM

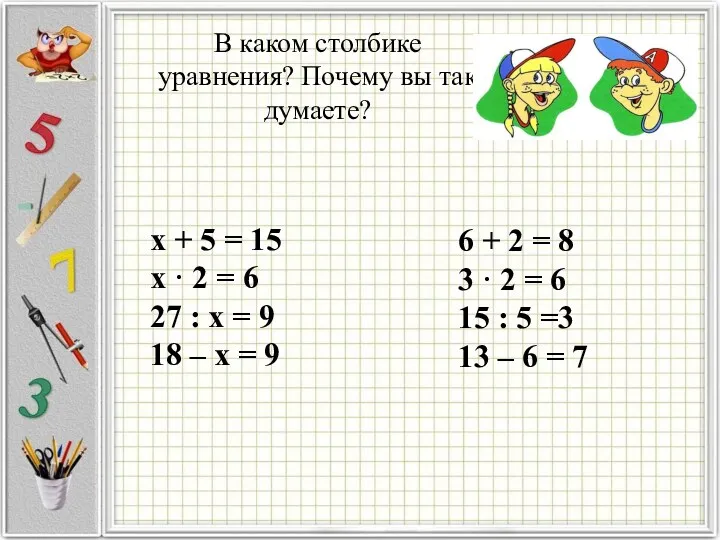

Робот пылесос VR5901LVM Неизвестный множитель - копия

Неизвестный множитель - копия