Содержание

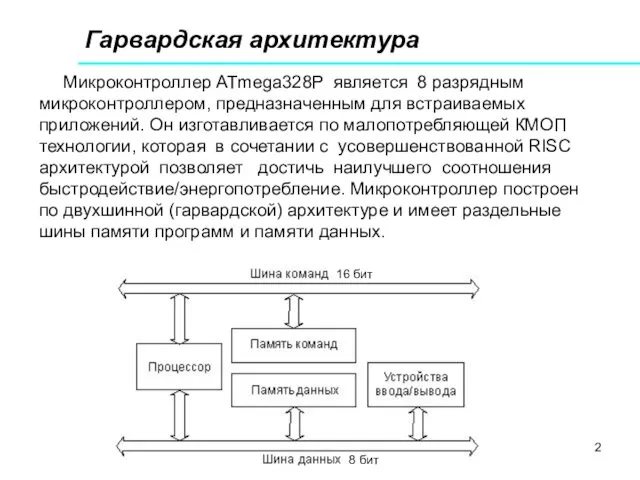

- 2. Гарвардская архитектура Микроконтроллер ATmega328P является 8 разрядным микроконтроллером, предназначенным для встраиваемых приложений. Он изготавливается по малопотребляющей

- 3. Основные характеристики • FLASH память программ объемом 32 Кбайт (число циклов стирания/записи не менее 1000); •

- 4. Подсистема ввода-вывода • 3 порта ввода-вывода (23 линии): В (8 линий), С (7 линий) и D

- 5. Периферийные устройства • 8 разрядные таймеры/счетчики (таймеры T0 и T2); • 16 разрядный таймер/счетчик (таймер T1);

- 6. Структурная схема ATmega328P

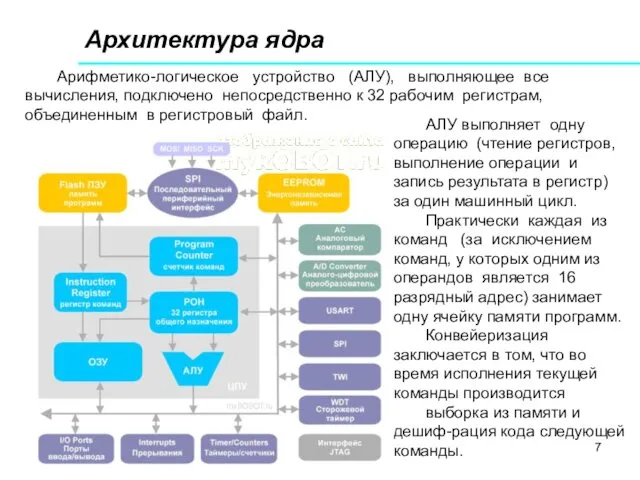

- 7. Архитектура ядра Арифметико-логическое устройство (АЛУ), выполняющее все вычисления, подключено непосредственно к 32 рабочим регистрам, объединенным в

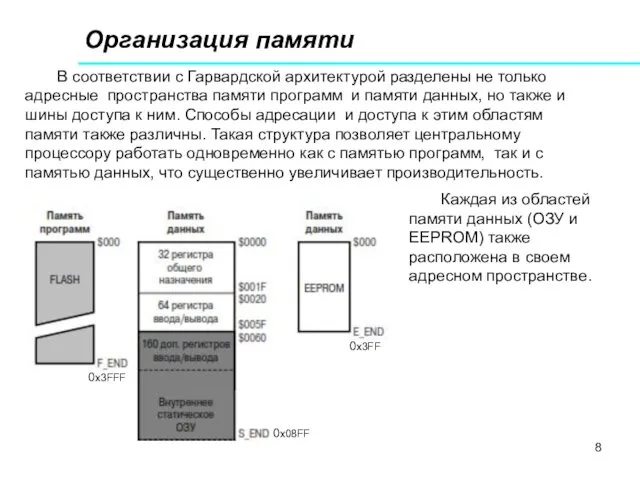

- 8. Организация памяти В соответствии с Гарвардской архитектурой разделены не только адресные пространства памяти программ и памяти

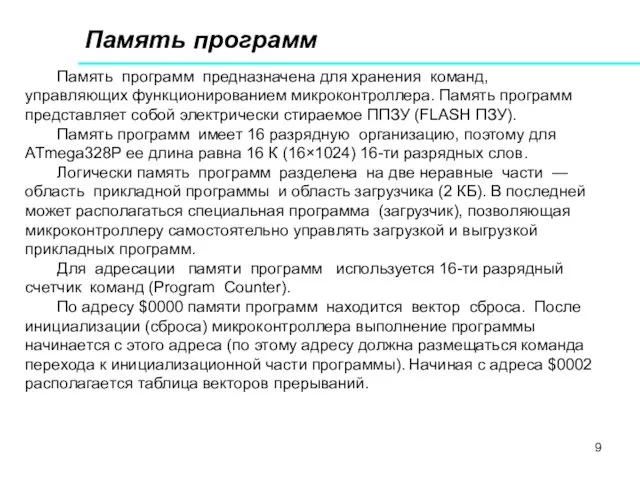

- 9. Память программ Память программ предназначена для хранения команд, управляющих функционированием микроконтроллера. Память программ представляет собой электрически

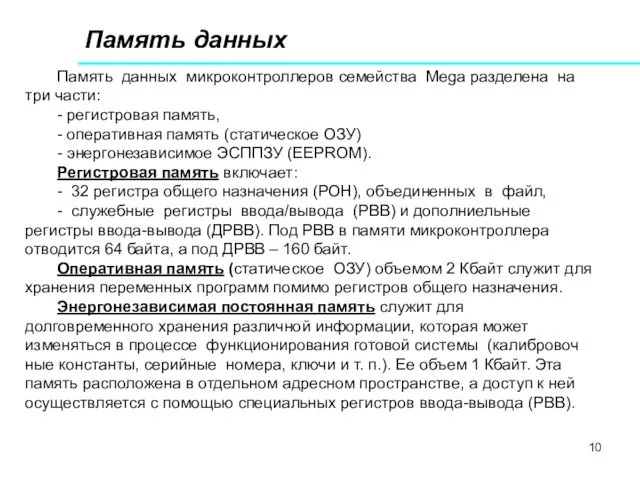

- 10. Память данных Память данных микроконтроллеров семейства Mega разделена на три части: - регистровая память, - оперативная

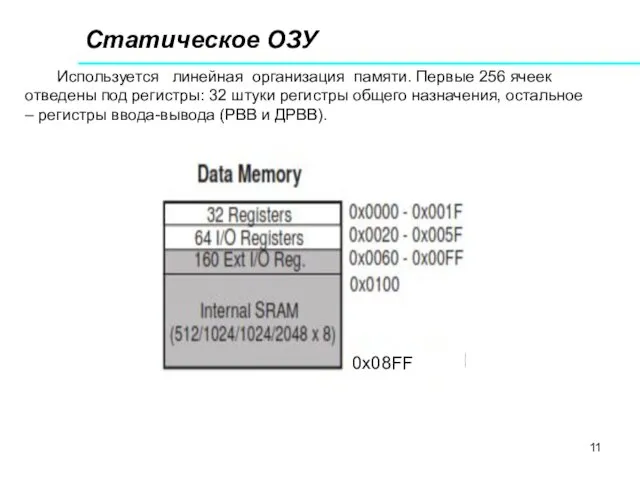

- 11. Статическое ОЗУ Используется линейная организация памяти. Первые 256 ячеек отведены под регистры: 32 штуки регистры общего

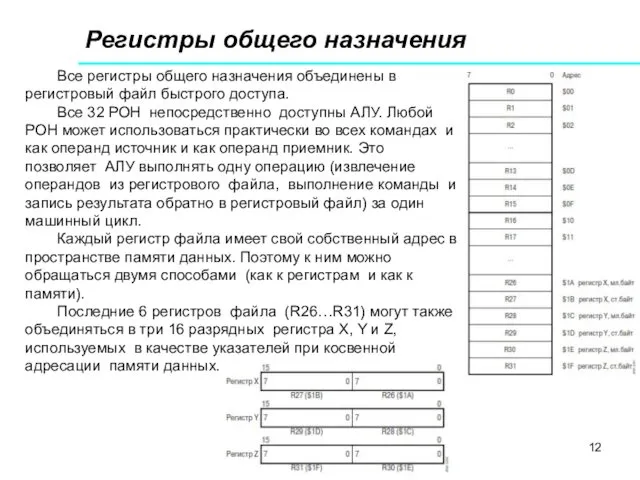

- 12. Регистры общего назначения Все регистры общего назначения объединены в регистровый файл быстрого доступа. Все 32 РОН

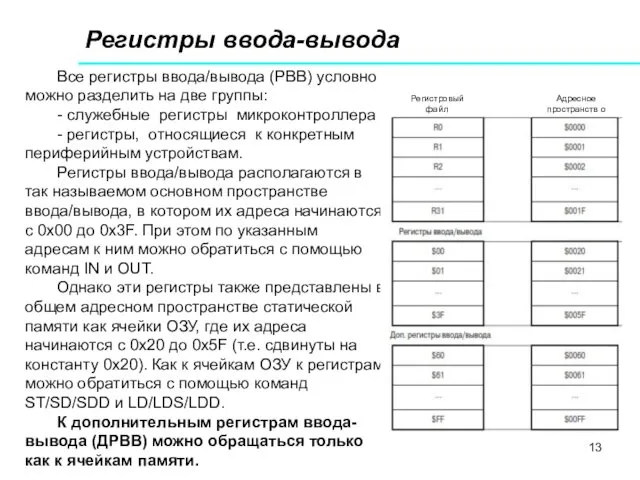

- 13. Регистры ввода-вывода Все регистры ввода/вывода (РВВ) условно можно разделить на две группы: - служебные регистры микроконтроллера

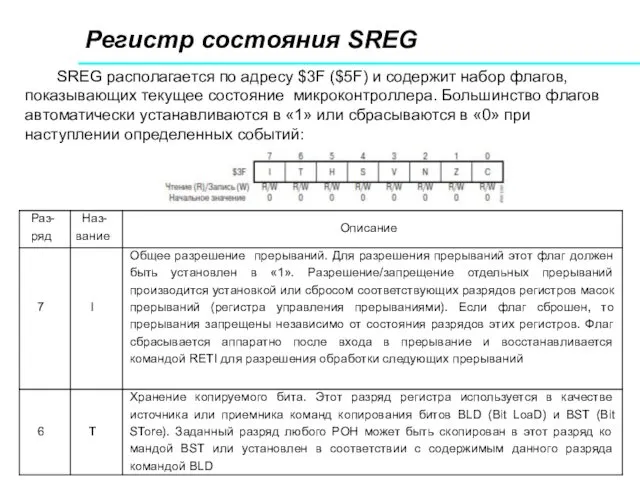

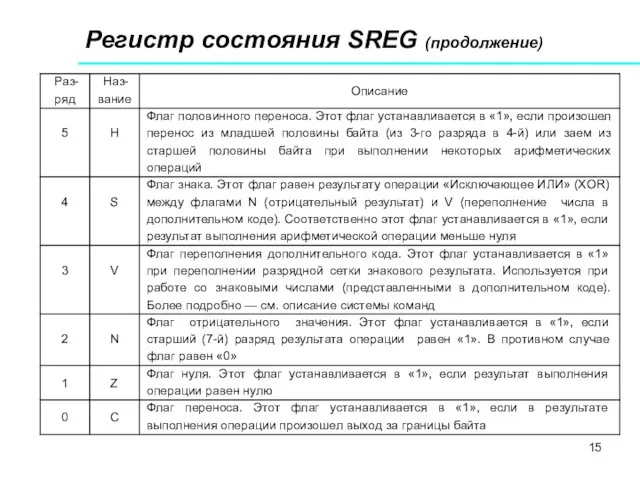

- 14. Регистр состояния SREG SREG располагается по адресу $3F ($5F) и содержит набор флагов, показывающих текущее состояние

- 15. Регистр состояния SREG (продолжение)

- 16. Содержание: Общие сведения о микроконтроллере ATmega328P Порты ввода-вывода

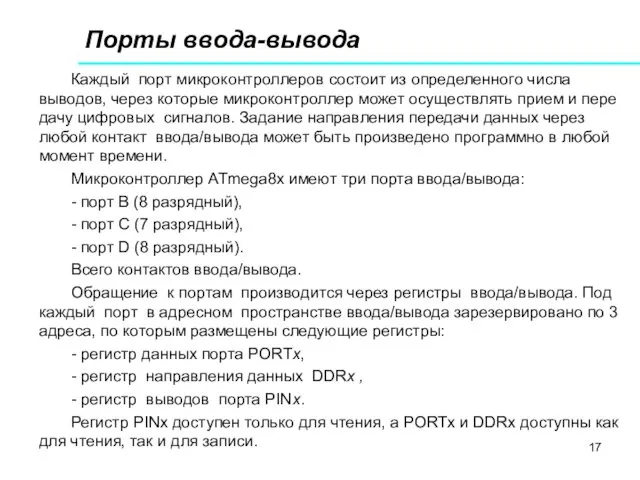

- 17. Порты ввода-вывода Каждый порт микроконтроллеров состоит из определенного числа выводов, через которые микроконтроллер может осуществлять прием

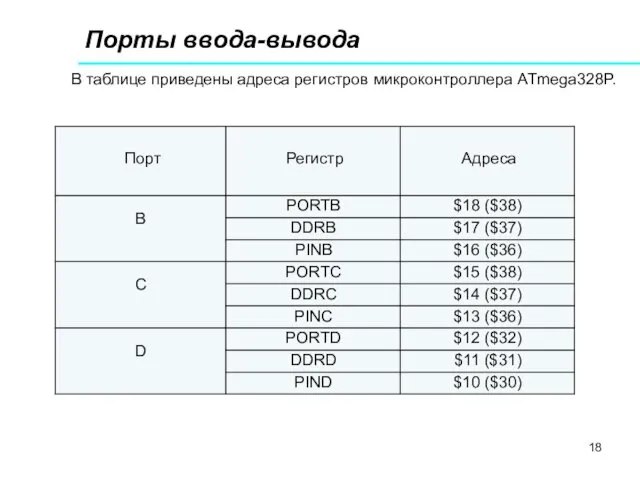

- 18. Порты ввода-вывода В таблице приведены адреса регистров микроконтроллера ATmega328P.

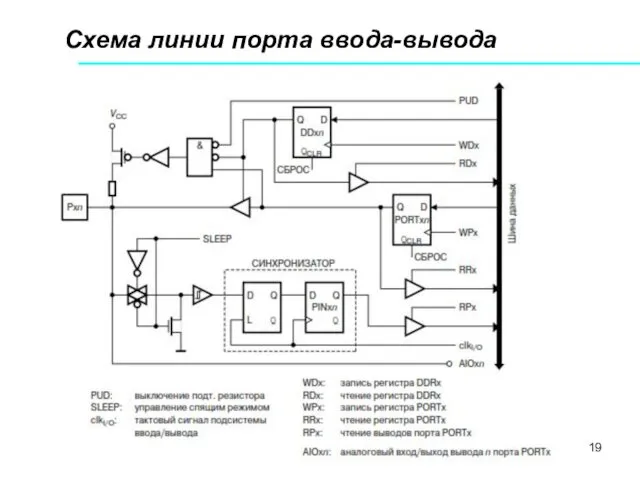

- 19. Схема линии порта ввода-вывода

- 21. Скачать презентацию

Zontic Corporation of Umbrellas

Zontic Corporation of Umbrellas Презентация Наш класс-наша семья!-выпуск 2010-2011 Диск

Презентация Наш класс-наша семья!-выпуск 2010-2011 Диск 29 октября - юбилей ВЛКСМ

29 октября - юбилей ВЛКСМ Искусство и духовная жизнь

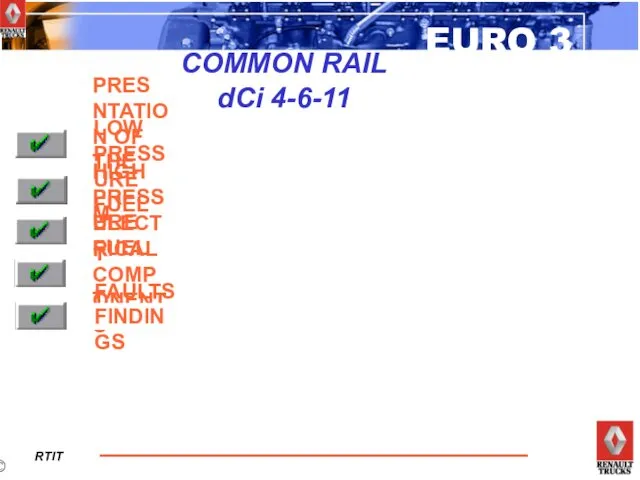

Искусство и духовная жизнь Common rail

Common rail Настоящая любовь

Настоящая любовь Классный час Отечественная война 1812 года для 3 класса

Классный час Отечественная война 1812 года для 3 класса Денежные потоки и управление денежными потоками

Денежные потоки и управление денежными потоками Игра - форма организации детской жизни

Игра - форма организации детской жизни Вклад сподвижников Пророка Мухаммада в развитие и становление Ислама

Вклад сподвижников Пророка Мухаммада в развитие и становление Ислама Федеральный стандарт оценки ФСО-9. Оценка для целей залога

Федеральный стандарт оценки ФСО-9. Оценка для целей залога Радиолокация. Классификация и виды

Радиолокация. Классификация и виды История строительства скважин

История строительства скважин Великобритания: конец Викторианской эпохи

Великобритания: конец Викторианской эпохи Лесная промышленность России

Лесная промышленность России МБОУ СОШ №126 г. Барнаул

МБОУ СОШ №126 г. Барнаул Портландцемент. Химический состав

Портландцемент. Химический состав Порядок аттестации педагогических работников

Порядок аттестации педагогических работников Ожоги лица. Осложнения огнестрельных и лучевых повреждений. Методы лечения пострадавших в экстремальных условиях

Ожоги лица. Осложнения огнестрельных и лучевых повреждений. Методы лечения пострадавших в экстремальных условиях Современный урок. 4 лекция

Современный урок. 4 лекция Игра - презентация на различение парных звонких и глухих согласных Найди соседа

Игра - презентация на различение парных звонких и глухих согласных Найди соседа Ферма. Картинки для дошкольников

Ферма. Картинки для дошкольников Авигационное (штурманское) обеспечение полетов

Авигационное (штурманское) обеспечение полетов Учебная практика. Бухгалтерская технология проведения и оформления инвентаризации

Учебная практика. Бухгалтерская технология проведения и оформления инвентаризации Инновационные методы по озеленению

Инновационные методы по озеленению Природные зоны Австралии

Природные зоны Австралии Знакомство с Майло. Конструктор

Знакомство с Майло. Конструктор Социальная стратификация и мобильность

Социальная стратификация и мобильность