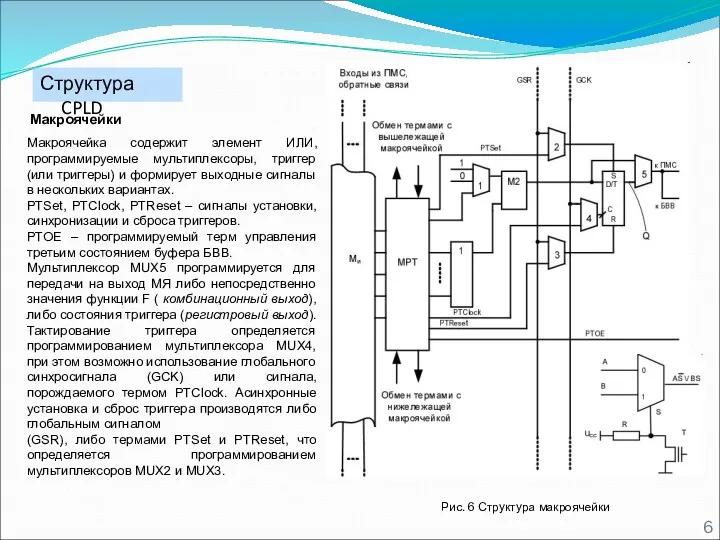

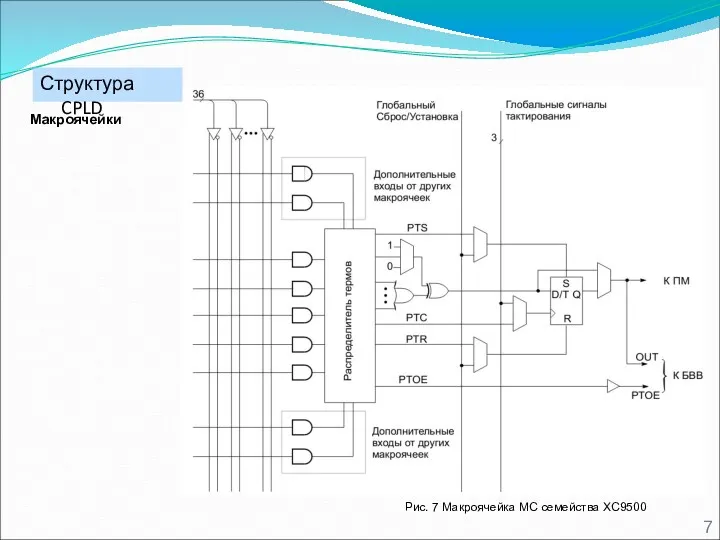

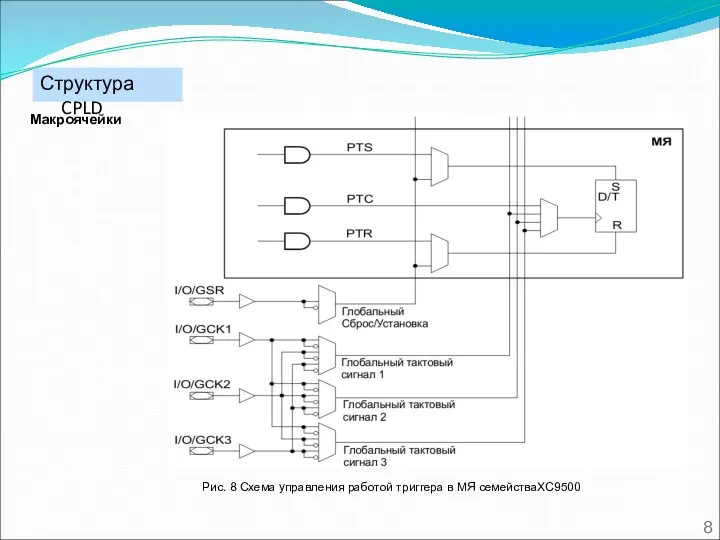

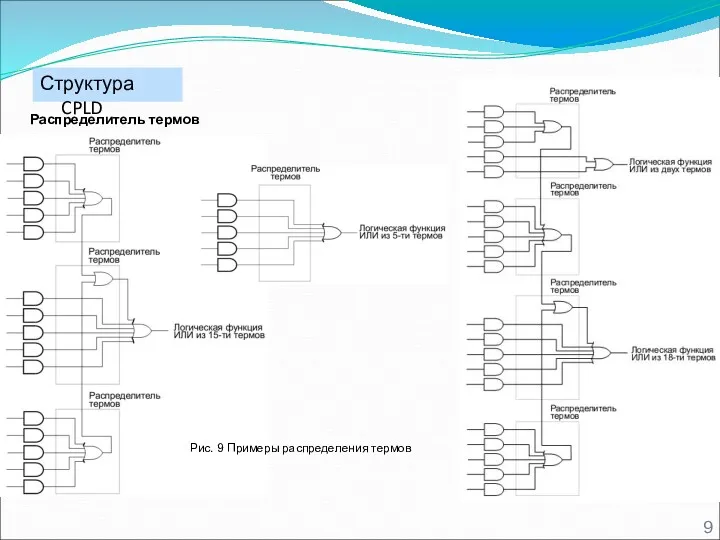

Структура CPLD

Рис. 6 Структура макроячейки

Макроячейка содержит элемент ИЛИ, программируемые мультиплексоры, триггер

(или триггеры) и формирует выходные сигналы в нескольких вариантах.

PTSet, PTClock, PTReset – сигналы установки, синхронизации и сброса триггеров.

PTOE – программируемый терм управления третьим состоянием буфера БВВ.

Мультиплексор MUX5 программируется для передачи на выход МЯ либо непосредственно значения функции F ( комбинационный выход), либо состояния триггера (регистровый выход). Тактирование триггера определяется программированием мультиплексора MUX4, при этом возможно использование глобального синхросигнала (GCK) или сигнала, порождаемого термом PTClock. Асинхронные установка и сброс триггера производятся либо глобальным сигналом

(GSR), либо термами PTSet и PTReset, что определяется программированием мультиплексоров MUX2 и MUX3.

Макроячейки

Выбор и подготовка материалов для резки

Выбор и подготовка материалов для резки Изготовление цветка гвоздики

Изготовление цветка гвоздики Зороастризм

Зороастризм Дошкольное детство. Психология развития и возрастная психология

Дошкольное детство. Психология развития и возрастная психология Types of transport

Types of transport Стихи на уроках - 8

Стихи на уроках - 8 Механические методы индукции родов

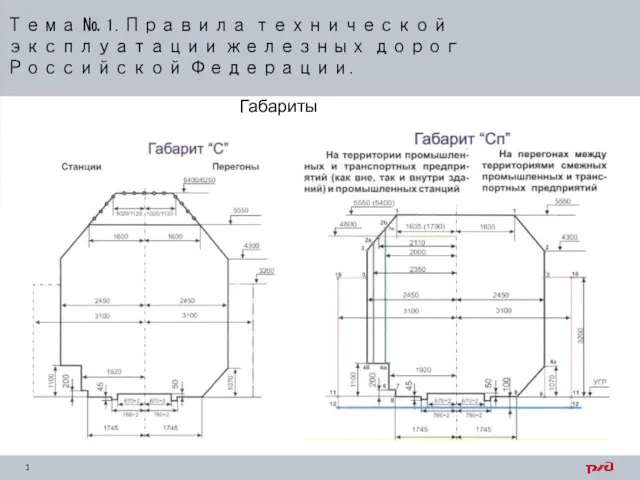

Механические методы индукции родов Правила технической эксплуатации железных дорог Российской Федерации

Правила технической эксплуатации железных дорог Российской Федерации Распорный анкерный болт

Распорный анкерный болт Компьютерные технологий в обучении математике

Компьютерные технологий в обучении математике Международный день родного языка - 21 февраля. Викторина Я знаю удмуртский язык

Международный день родного языка - 21 февраля. Викторина Я знаю удмуртский язык Исследование и разработка системы автоматического управления процессом сушки аммиачной селитры

Исследование и разработка системы автоматического управления процессом сушки аммиачной селитры Гештальт-терапия как практико-ориентированный подход в психологии

Гештальт-терапия как практико-ориентированный подход в психологии Прекрасное Далеко. Слова Ю. Энтина. Музыка Е. Крылатова

Прекрасное Далеко. Слова Ю. Энтина. Музыка Е. Крылатова История возникновения образа Золотой век Голливуда 40-х годов

История возникновения образа Золотой век Голливуда 40-х годов В Новый год по странам мира

В Новый год по странам мира Winemaking In Russia

Winemaking In Russia Создание контента в Instagram

Создание контента в Instagram История происхождения и развития шрифтов

История происхождения и развития шрифтов Трудный диалог с учёбой, или как помочь своему ребёнку учиться

Трудный диалог с учёбой, или как помочь своему ребёнку учиться Симптомы поражения различных долей головного мозга, мозжечка, экстрапирамидных структур

Симптомы поражения различных долей головного мозга, мозжечка, экстрапирамидных структур Регистры

Регистры Зимние Олимпийские игры XX - XXII

Зимние Олимпийские игры XX - XXII ЛДО Прикамье отряд: Еще не взрослые! 5-7 классы

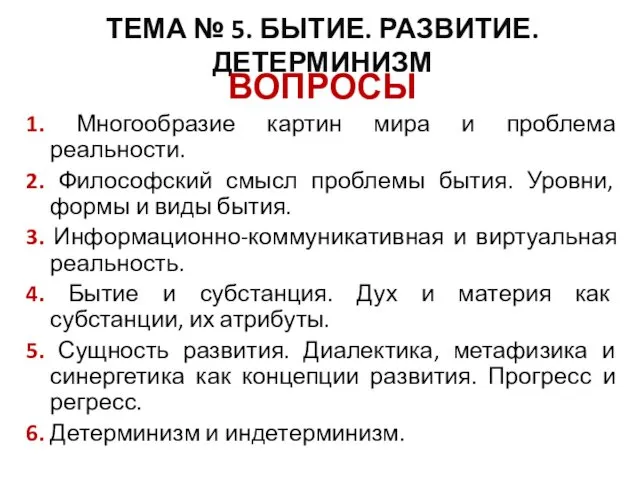

ЛДО Прикамье отряд: Еще не взрослые! 5-7 классы Бытие. Развитие. Детерминизм. Тема №5

Бытие. Развитие. Детерминизм. Тема №5 Река и ее части

Река и ее части Кордиц совет (1)

Кордиц совет (1) Клиническая физиология кислотно-щелочного равновесия

Клиническая физиология кислотно-щелочного равновесия