Содержание

- 2. Регистр – последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований

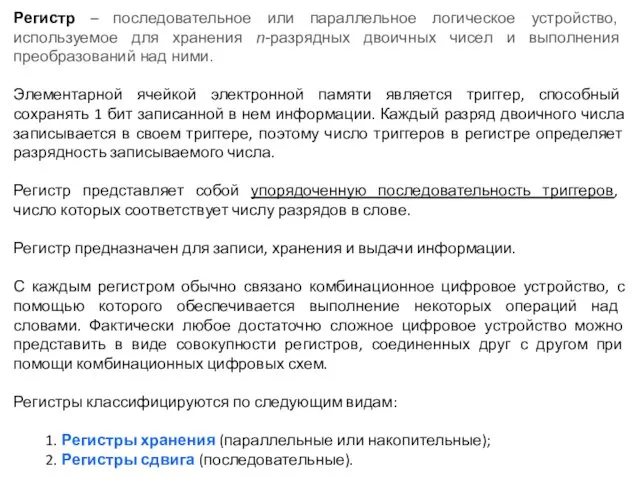

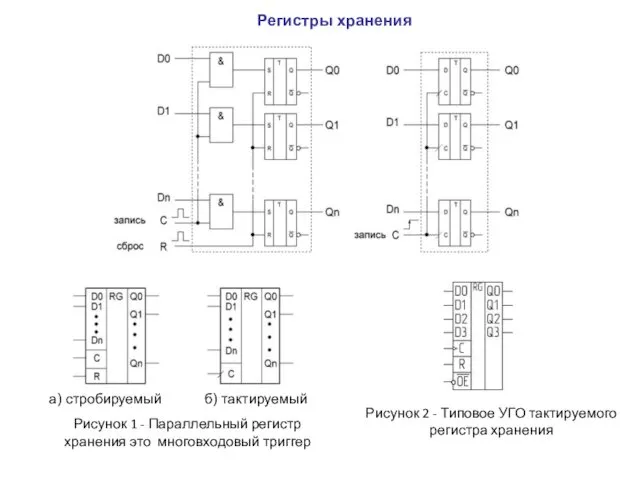

- 3. Регистры хранения Рисунок 1 - Параллельный регистр хранения это многовходовый триггер Рисунок 2 - Типовое УГО

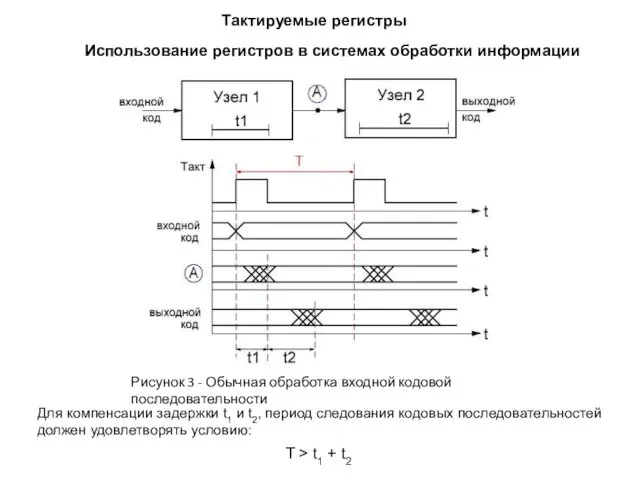

- 4. Рисунок 3 - Обычная обработка входной кодовой последовательности T > t1 + t2 Для компенсации задержки

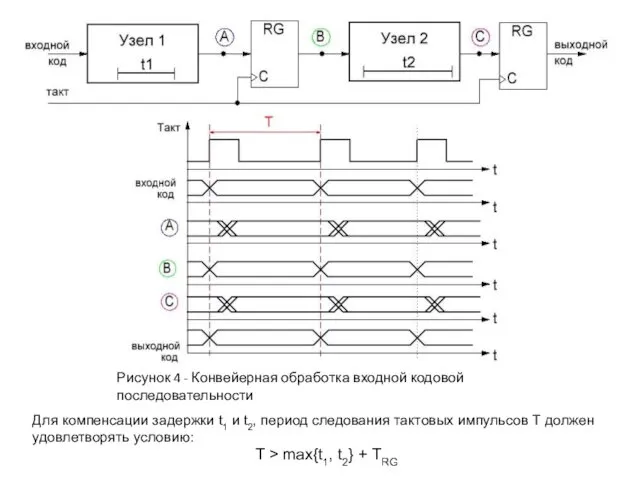

- 5. Рисунок 4 - Конвейерная обработка входной кодовой последовательности Для компенсации задержки t1 и t2, период следования

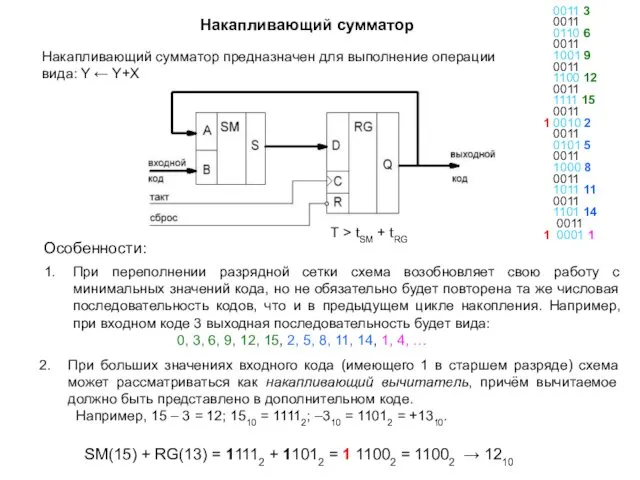

- 6. Накапливающий сумматор T > tSM + tRG Особенности: При переполнении разрядной сетки схема возобновляет свою работу

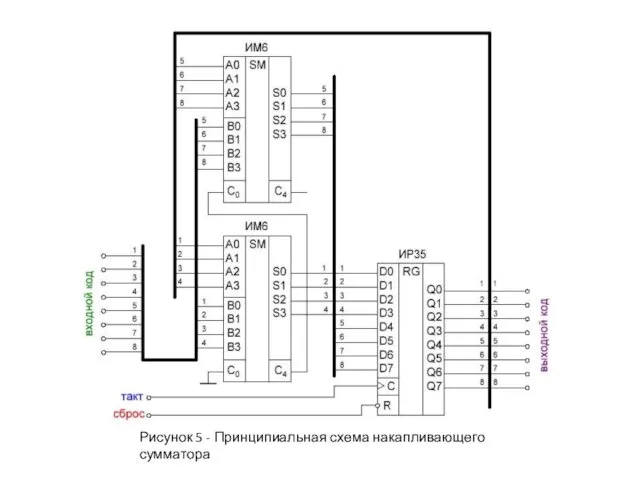

- 7. Рисунок 5 - Принципиальная схема накапливающего сумматора

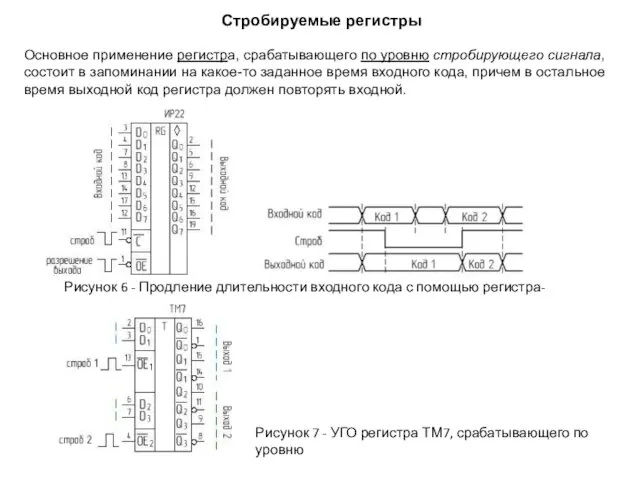

- 8. Рисунок 6 - Продление длительности входного кода с помощью регистра-защелки Основное применение регистра, срабатывающего по уровню

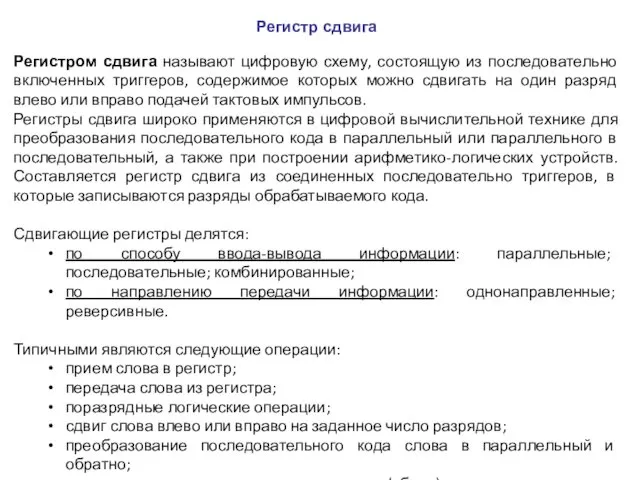

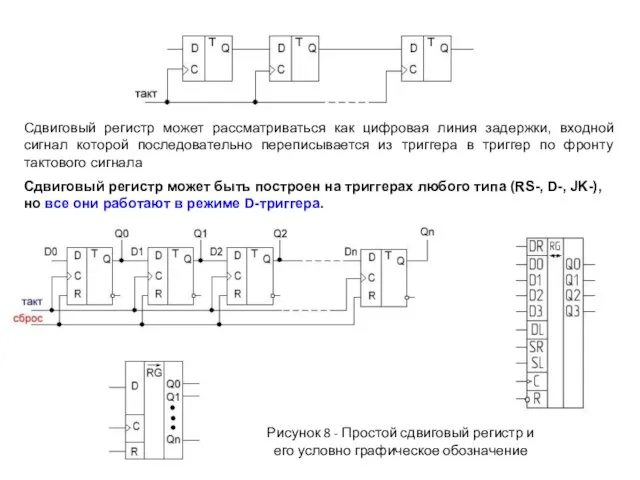

- 9. Регистром сдвига называют цифровую схему, состоящую из последовательно включенных триггеров, содержимое которых можно сдвигать на один

- 10. Сдвиговый регистр может рассматриваться как цифровая линия задержки, входной сигнал которой последовательно переписывается из триггера в

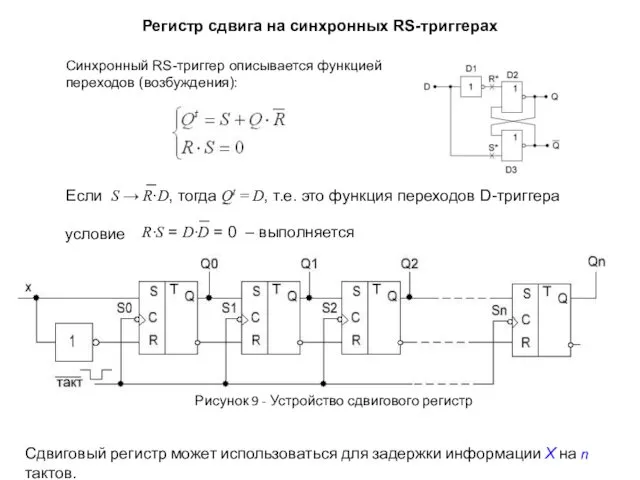

- 11. Если S → R∙D, тогда Qt = D, т.е. это функция переходов D-триггера R∙S = D∙D

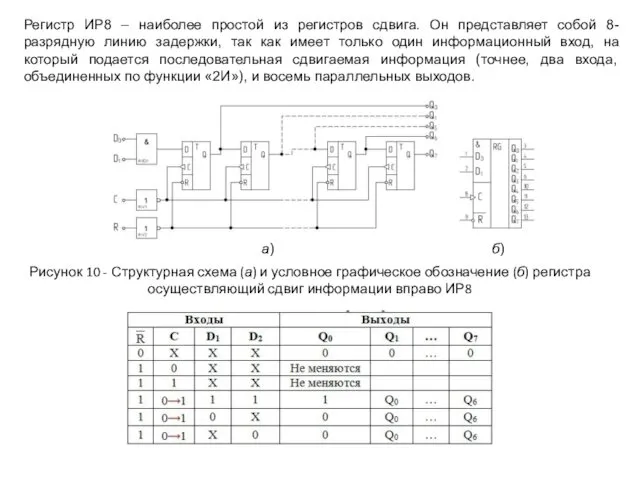

- 12. Рисунок 10 - Структурная схема (а) и условное графическое обозначение (б) регистра осуществляющий сдвиг информации вправо

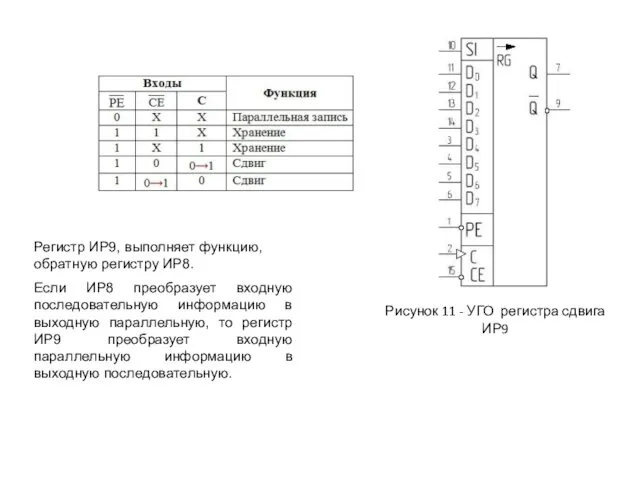

- 13. Рисунок 11 - УГО регистра сдвига ИР9 Регистр ИР9, выполняет функцию, обратную регистру ИР8. Если ИР8

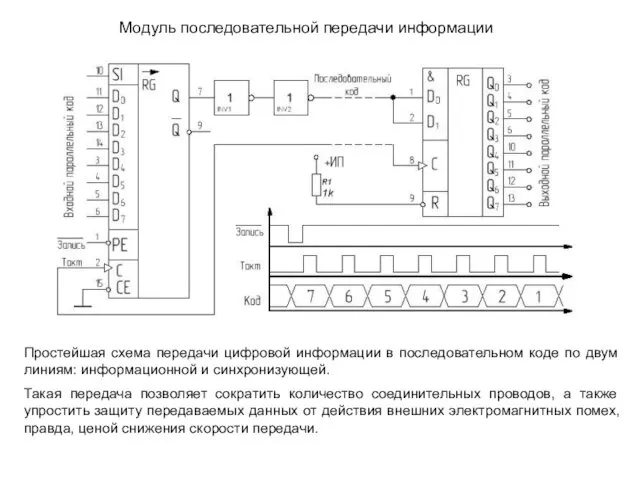

- 14. Модуль последовательной передачи информации Простейшая схема передачи цифровой информации в последовательном коде по двум линиям: информационной

- 15. Рисунок 12 - Увеличение разрядности сдвигового регистра ИР8 Рисунок 13 - Увеличение разрядности сдвигового регистра ИР9

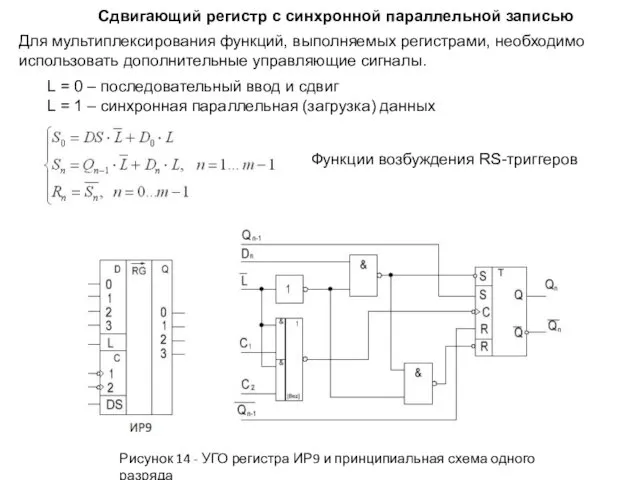

- 16. Сдвигающий регистр с синхронной параллельной записью Для мультиплексирования функций, выполняемых регистрами, необходимо использовать дополнительные управляющие сигналы.

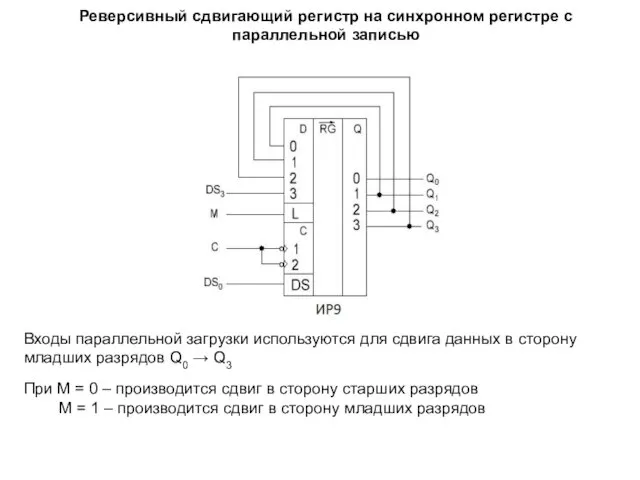

- 17. Реверсивный сдвигающий регистр на синхронном регистре с параллельной записью Входы параллельной загрузки используются для сдвига данных

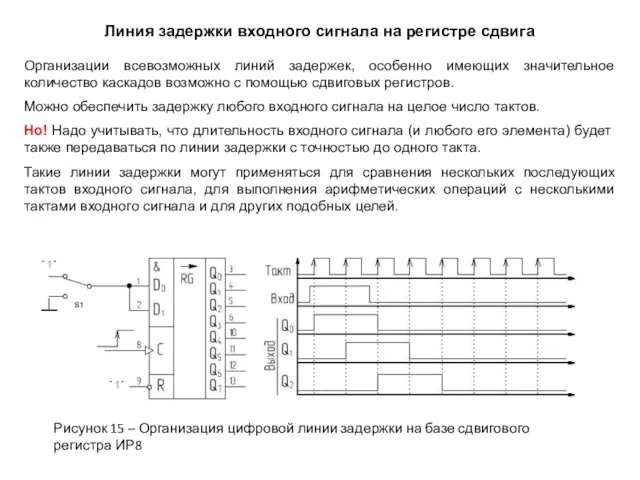

- 18. Линия задержки входного сигнала на регистре сдвига Организации всевозможных линий задержек, особенно имеющих значительное количество каскадов

- 20. Скачать презентацию

Методы приёма оптических сигналов

Методы приёма оптических сигналов Из опыта работы городской творческой группы учителей истории 2011-2015 гг

Из опыта работы городской творческой группы учителей истории 2011-2015 гг Конструктивные элементы здания гостиницы

Конструктивные элементы здания гостиницы Традиционное народное творчество

Традиционное народное творчество Общеобязательные нормы, установленные государством. Право

Общеобязательные нормы, установленные государством. Право Классификация дефектов трубопровода

Классификация дефектов трубопровода Память МПС

Память МПС Протоколы взаимодействия по системе №7 МККТТ

Протоколы взаимодействия по системе №7 МККТТ Особенности гендерной социализации в игровой деятельности дошкольников

Особенности гендерной социализации в игровой деятельности дошкольников Правопорушення та юридична відповідальність

Правопорушення та юридична відповідальність Надмолекулярные структуры полимеров (НС)

Надмолекулярные структуры полимеров (НС) Презентация по технологии Новогодняя игрушка

Презентация по технологии Новогодняя игрушка Аварийно-спасательные работы в зоне наводнения

Аварийно-спасательные работы в зоне наводнения Интерактивные игры в образовательном процессе ДОУ

Интерактивные игры в образовательном процессе ДОУ 20231118_vidy_sil_7_klass

20231118_vidy_sil_7_klass Котельные установки

Котельные установки Кирилл Иерусалимский (315-386). Поучение предогласительное, или предисловие к огласительным поучениям

Кирилл Иерусалимский (315-386). Поучение предогласительное, или предисловие к огласительным поучениям 04-VDI-JS-HyperV

04-VDI-JS-HyperV Контекстное обучение взрослых

Контекстное обучение взрослых Сварные соединения и швы

Сварные соединения и швы Пассивный доход

Пассивный доход Женские имена в летописи химии

Женские имена в летописи химии Внешняя политика в 20-е годы

Внешняя политика в 20-е годы Лево Луи - французский архитектор, один из основоположников французского классицизма

Лево Луи - французский архитектор, один из основоположников французского классицизма Самопрезентация учителя английского языка

Самопрезентация учителя английского языка Использование развивающей технологии В.В.Воскобовича в детском саду

Использование развивающей технологии В.В.Воскобовича в детском саду В мире животных

В мире животных Презентация Тряпичная кукла Диск

Презентация Тряпичная кукла Диск