Содержание

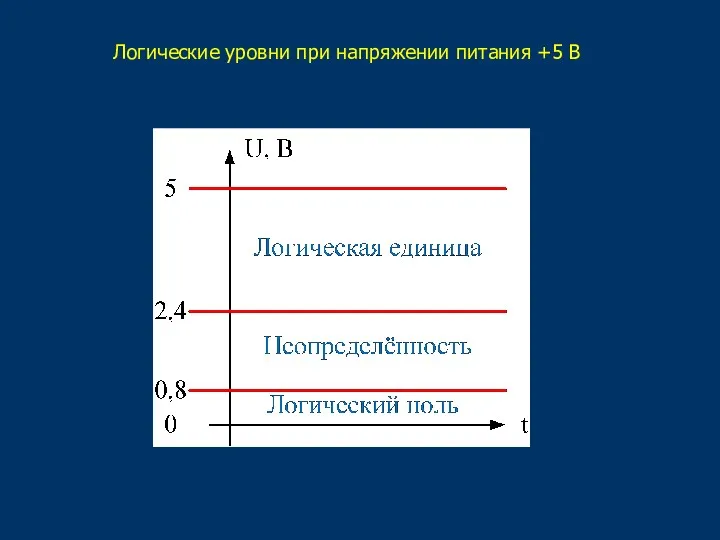

- 2. Логические уровни при напряжении питания +5 В

- 3. Двоичный и шестнадцатеричный коды

- 4. Целые двоичные числа без знака

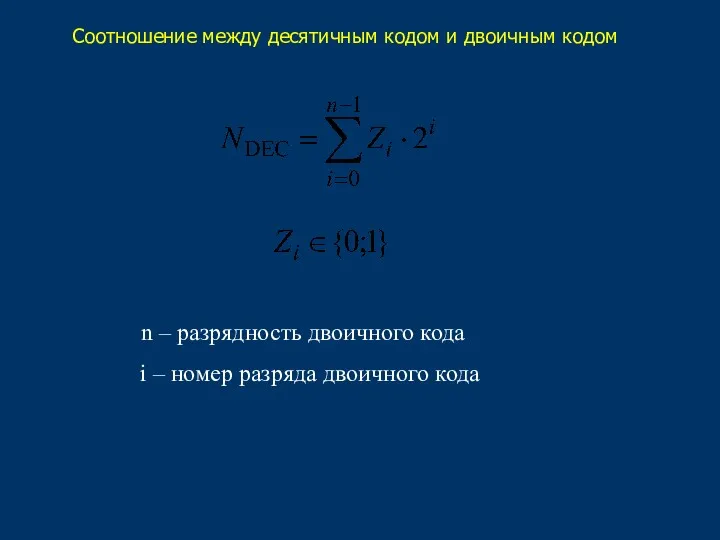

- 5. n – разрядность двоичного кода i – номер разряда двоичного кода Соотношение между десятичным кодом и

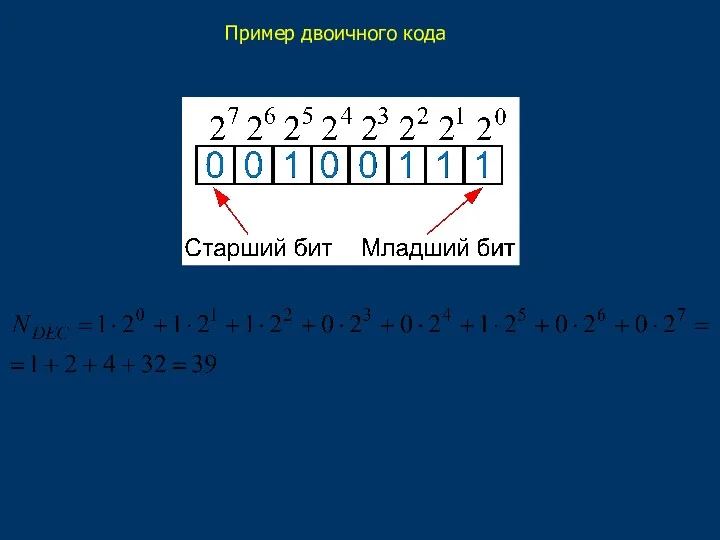

- 6. Пример двоичного кода

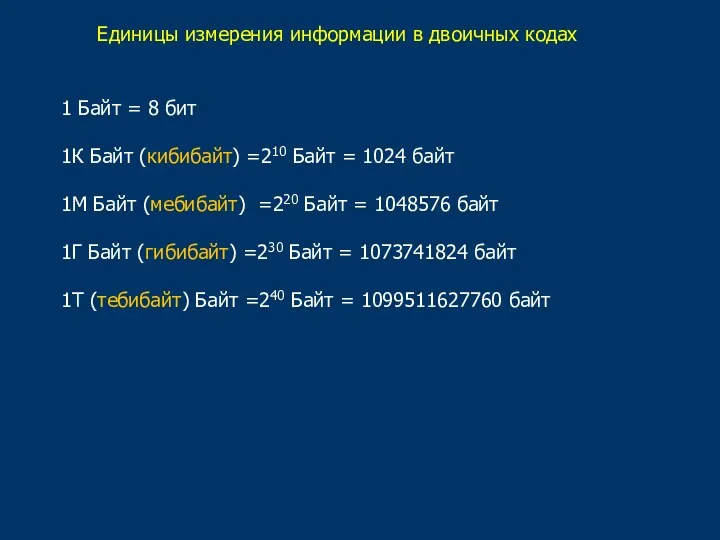

- 7. Единицы измерения информации в двоичных кодах 1 Байт = 8 бит 1К Байт (кибибайт) =210 Байт

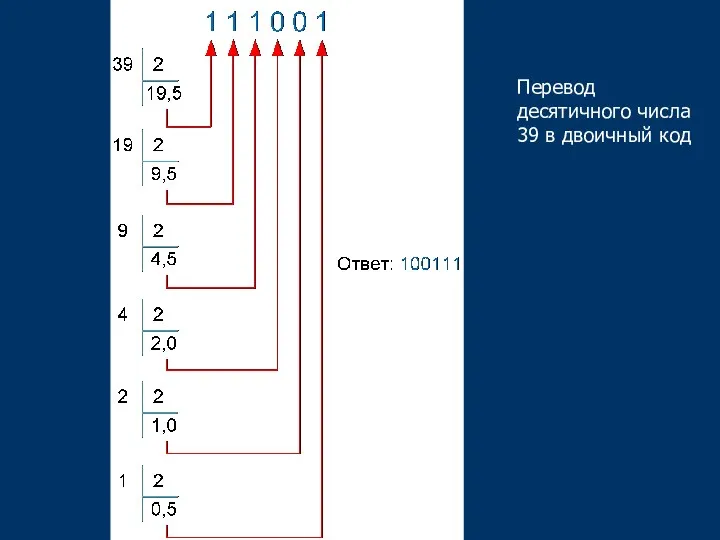

- 8. Перевод десятичного числа 39 в двоичный код

- 9. Целые двоичные числа со знаком

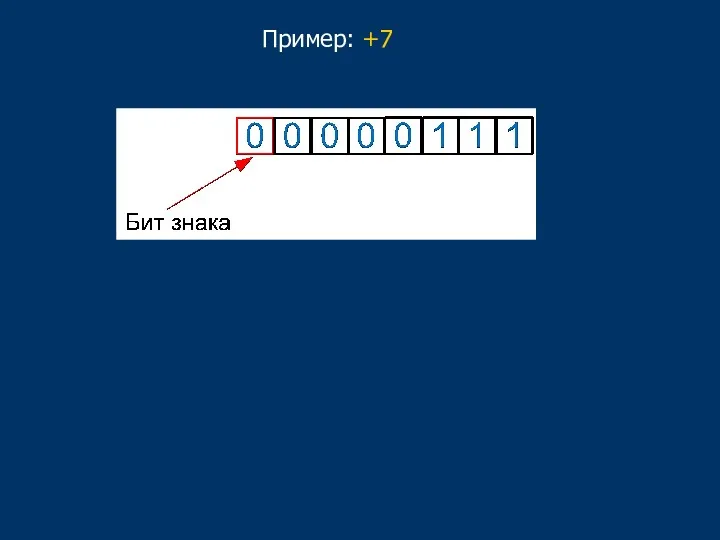

- 10. Пример: +7

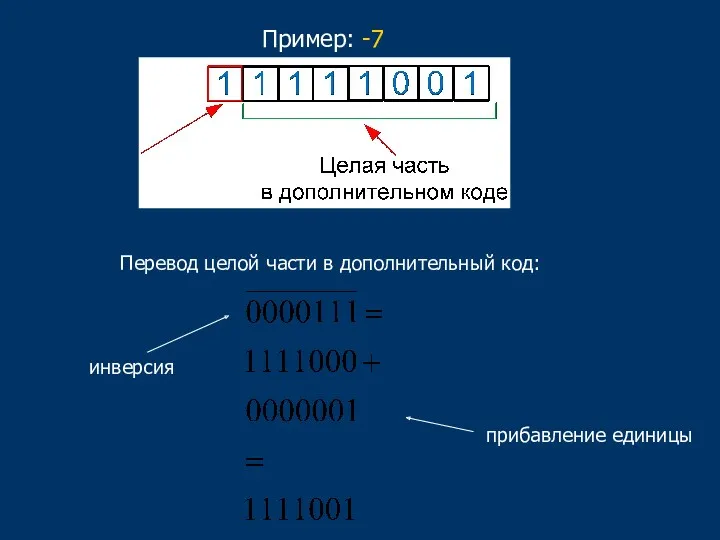

- 11. Пример: -7 Перевод целой части в дополнительный код: инверсия прибавление единицы

- 12. Двоичные числа с фиксированной запятой (точкой) (fixed point)

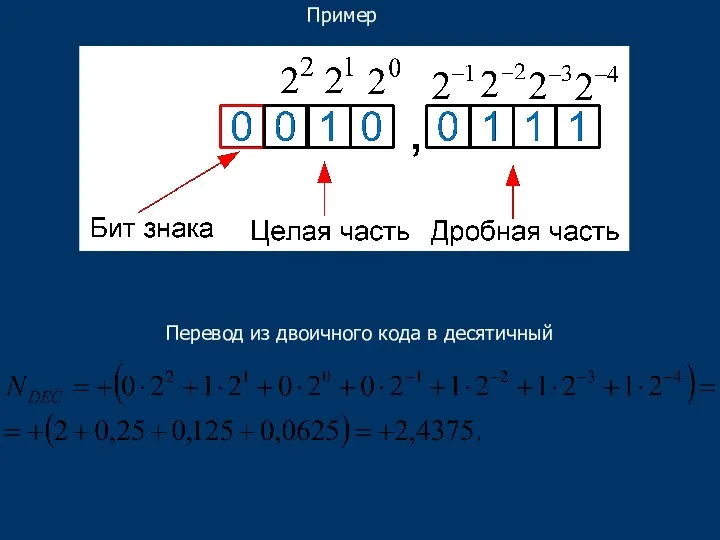

- 13. Пример Перевод из двоичного кода в десятичный

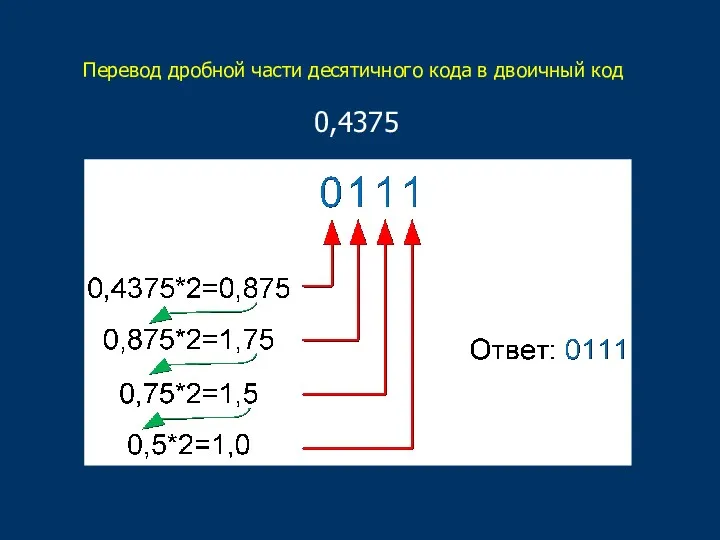

- 14. Перевод дробной части десятичного кода в двоичный код 0,4375

- 15. Двоичные числа плавающей запятой (точкой) (floating point)

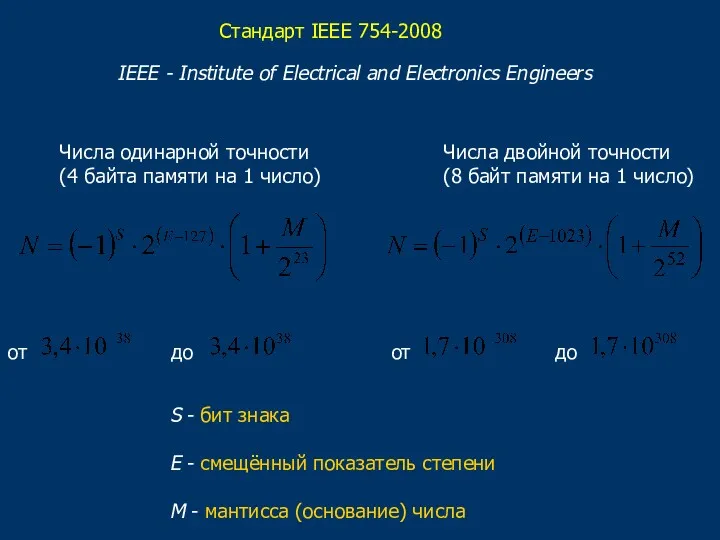

- 16. Стандарт IEEE 754-2008 IEEE - Institute of Electrical and Electronics Engineers Числа двойной точности (8 байт

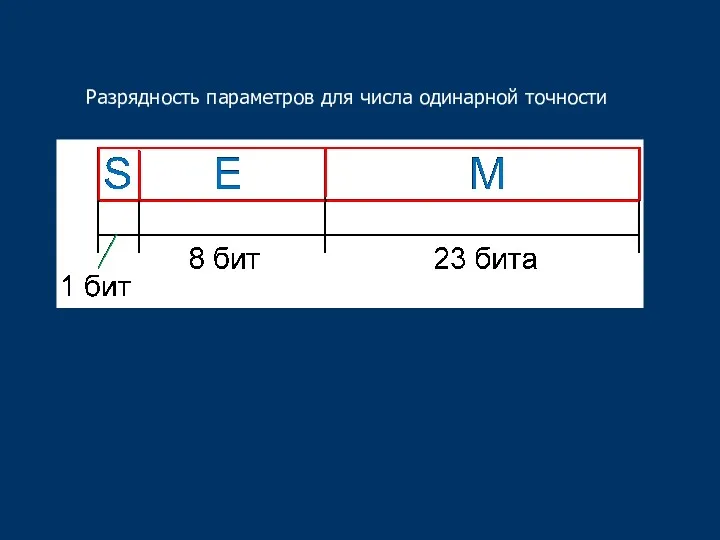

- 17. Разрядность параметров для числа одинарной точности

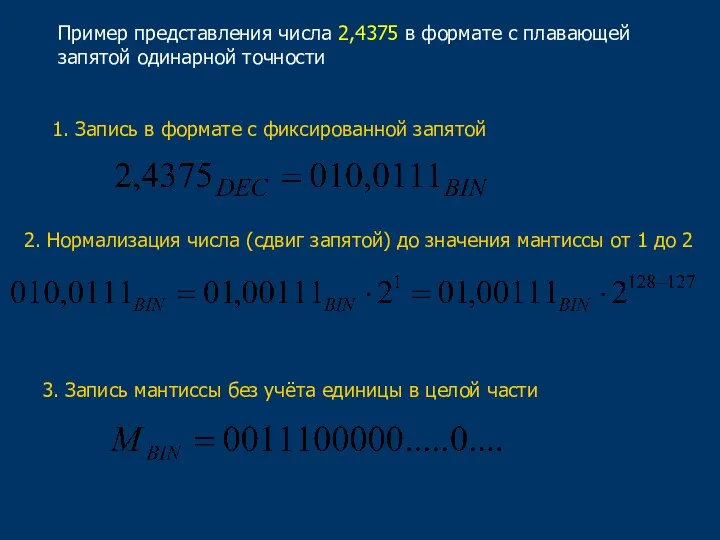

- 18. Пример представления числа 2,4375 в формате с плавающей запятой одинарной точности 1. Запись в формате с

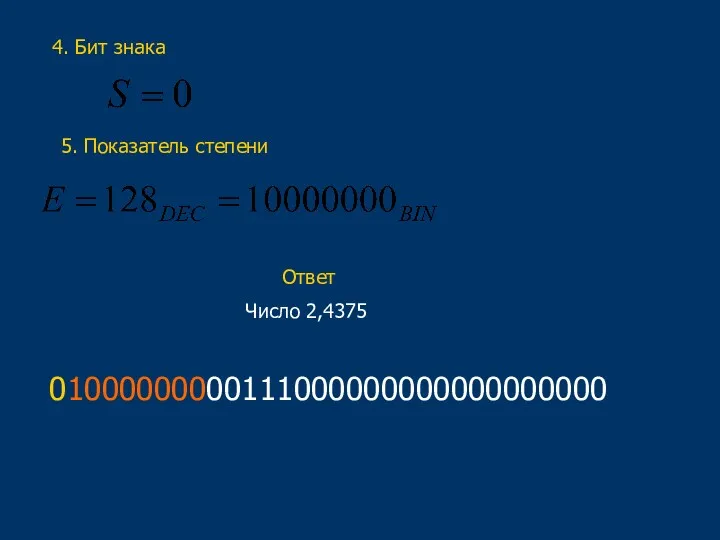

- 19. 4. Бит знака 5. Показатель степени Ответ 01000000000111000000000000000000 Число 2,4375

- 20. Шестнадцатеричный код (hexadecimal - HEX)

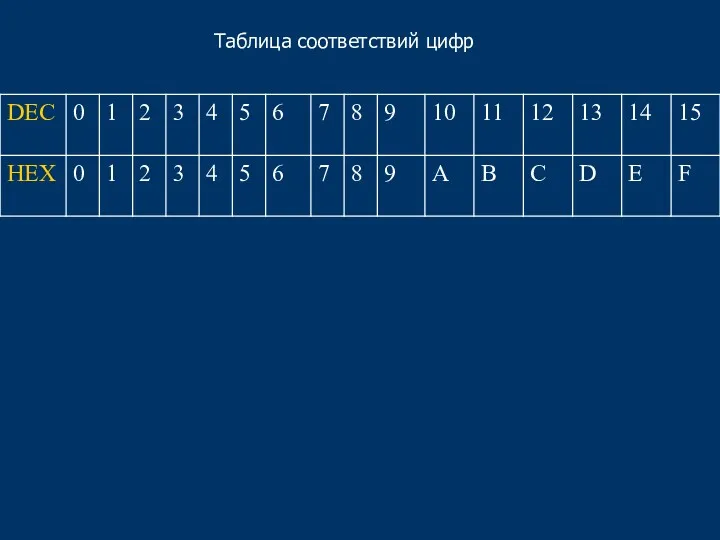

- 21. Таблица соответствий цифр

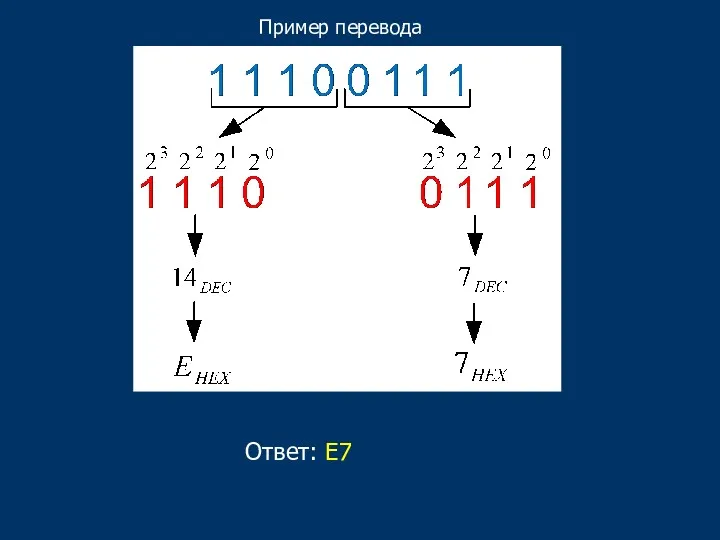

- 22. Пример перевода Ответ: Е7

- 23. Простейшие арифметические операции с двоичными числами без знака

- 24. Правила арифметического сложения двоичных чисел 0 + 0 = 0 0 + 1 = 1 1

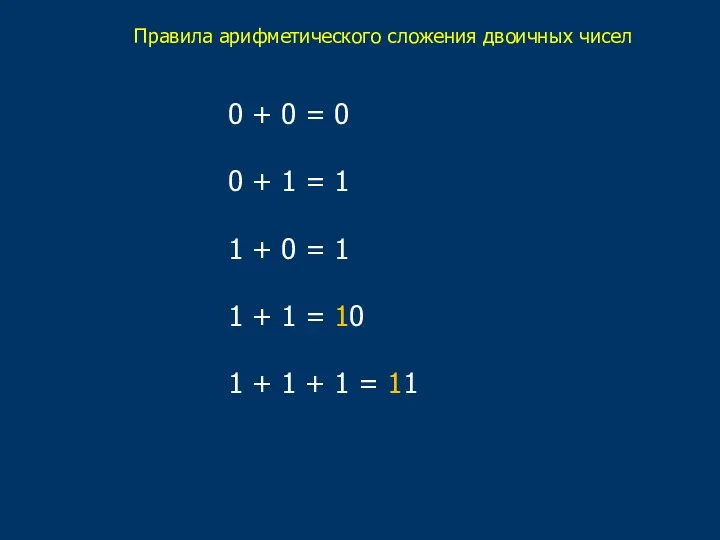

- 25. Пример арифметического сложения двоичных чисел 1 1 0 0 1 1 1 1 1 1 1

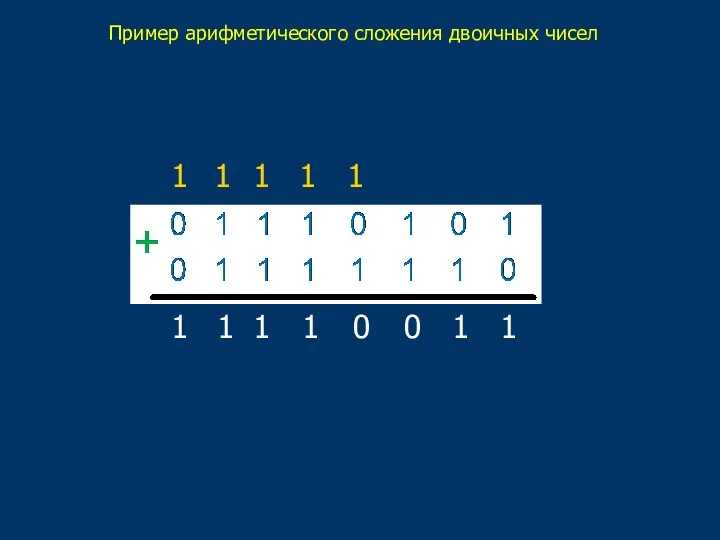

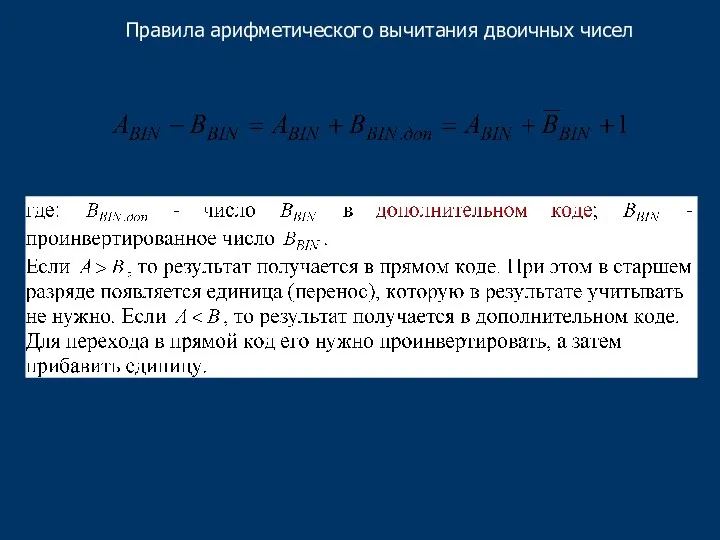

- 26. Правила арифметического вычитания двоичных чисел

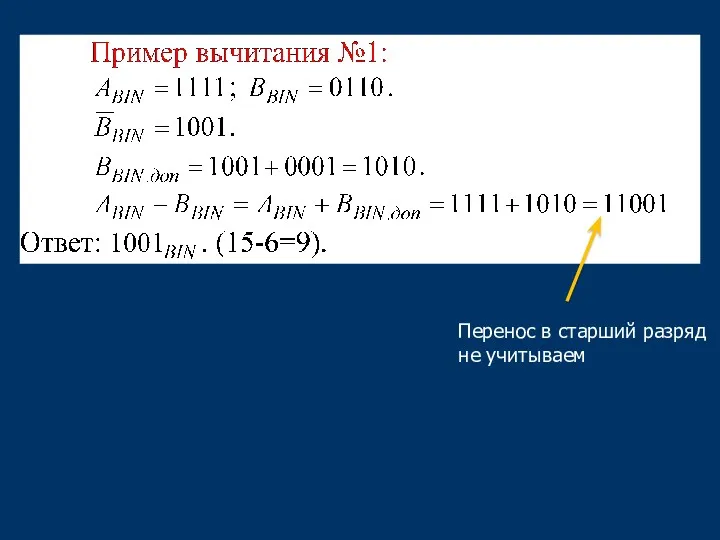

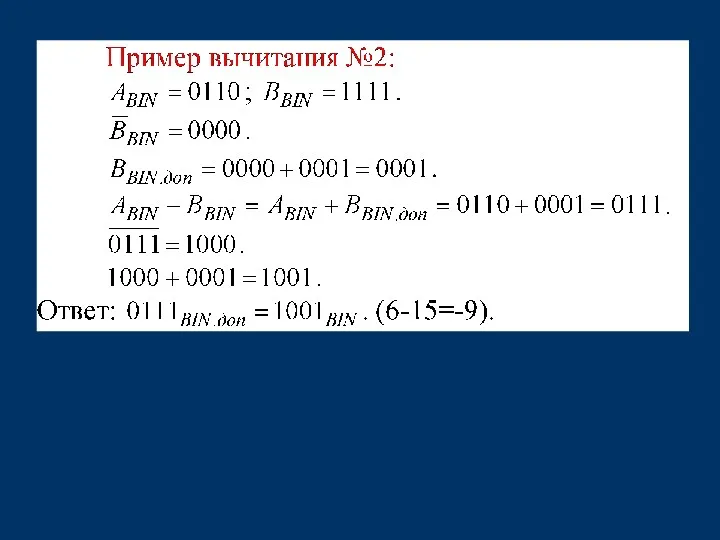

- 27. Перенос в старший разряд не учитываем

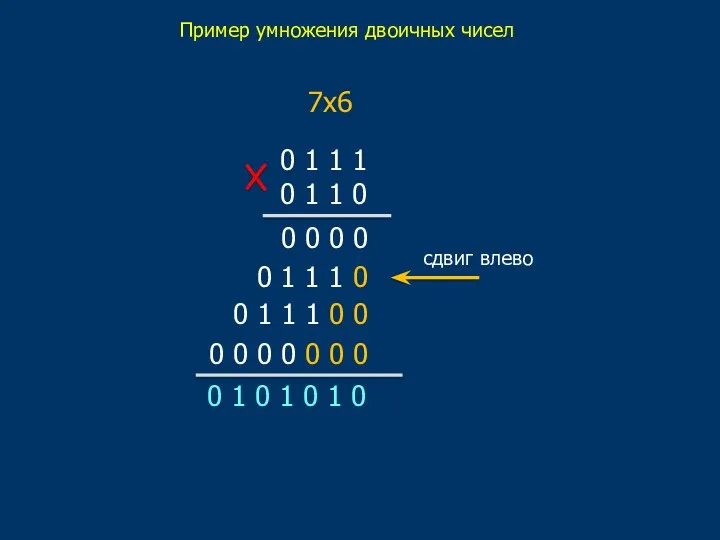

- 29. Пример умножения двоичных чисел 0 1 1 1 0 1 1 0 7х6 0 0 0

- 30. Логические операции в цифровой электронике

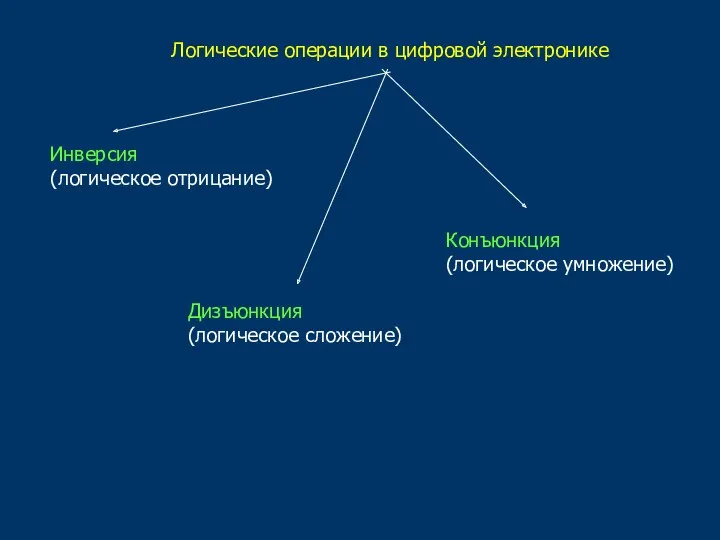

- 31. Логические операции в цифровой электронике Инверсия (логическое отрицание) Дизъюнкция (логическое сложение) Конъюнкция (логическое умножение)

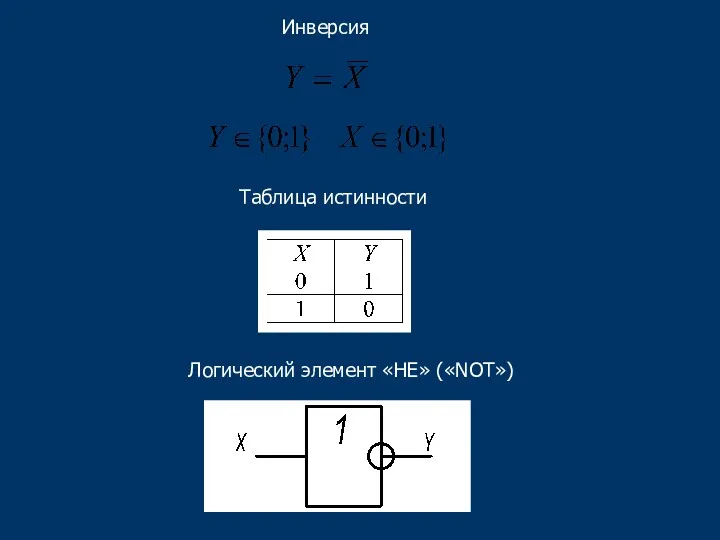

- 32. Инверсия Таблица истинности Логический элемент «НЕ» («NOT»)

- 33. Дизъюнкция Таблица истинности Логический элемент «ИЛИ» («OR») Анимация

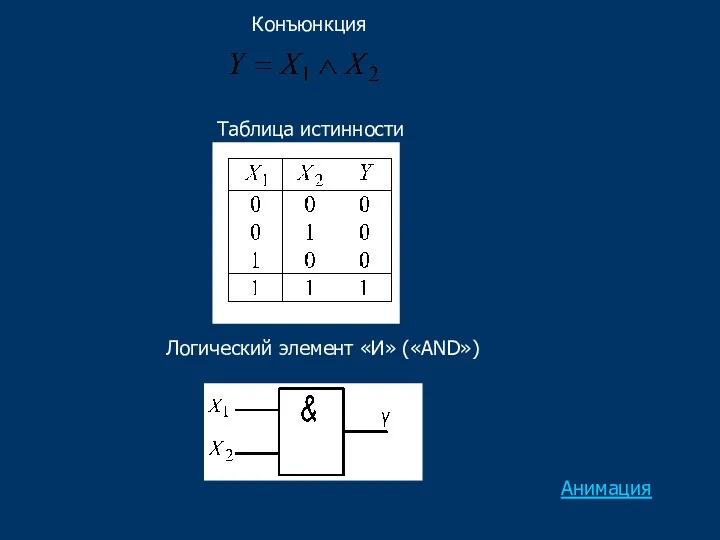

- 34. Конъюнкция Таблица истинности Логический элемент «И» («AND») Анимация

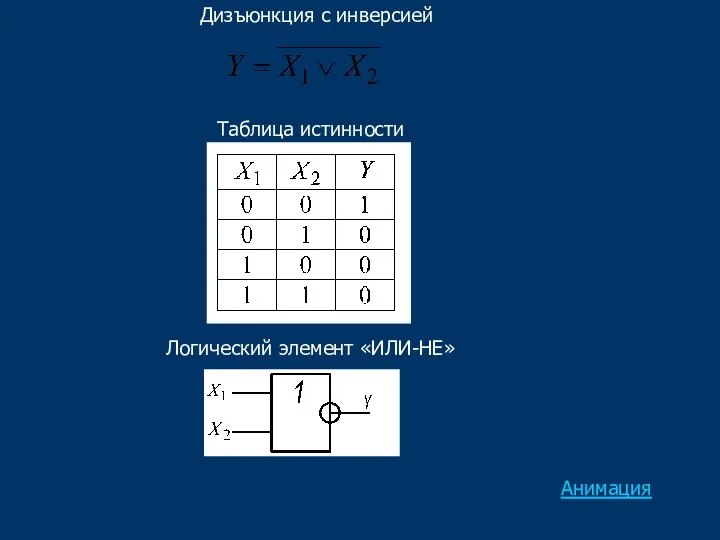

- 35. Дизъюнкция с инверсией Таблица истинности Логический элемент «ИЛИ-НЕ» Анимация

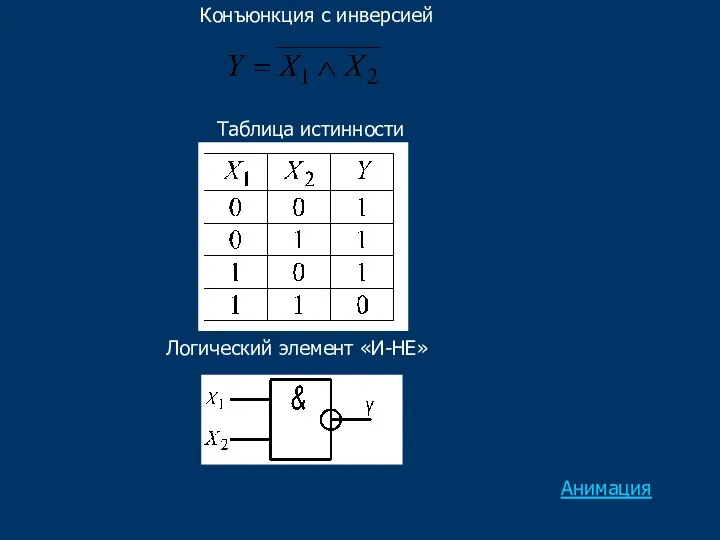

- 36. Конъюнкция с инверсией Таблица истинности Логический элемент «И-НЕ» Анимация

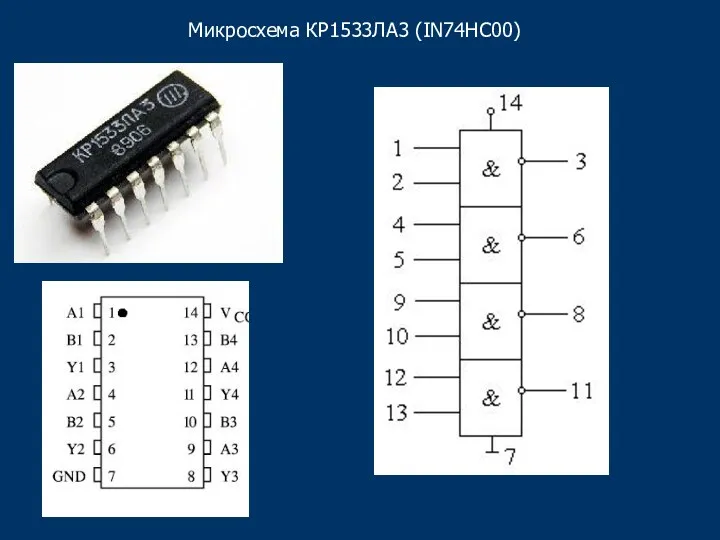

- 37. Микросхема КP1533ЛА3 (IN74HC00)

- 38. Цифровые триггеры

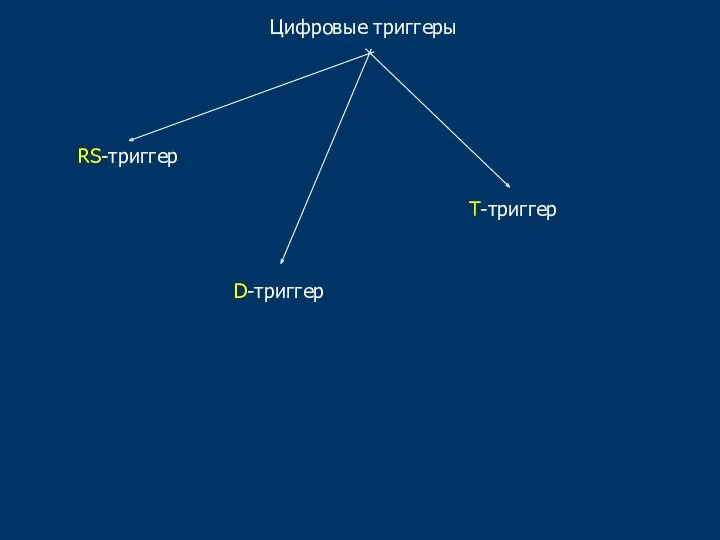

- 39. Цифровые триггеры RS-триггер D-триггер Т-триггер

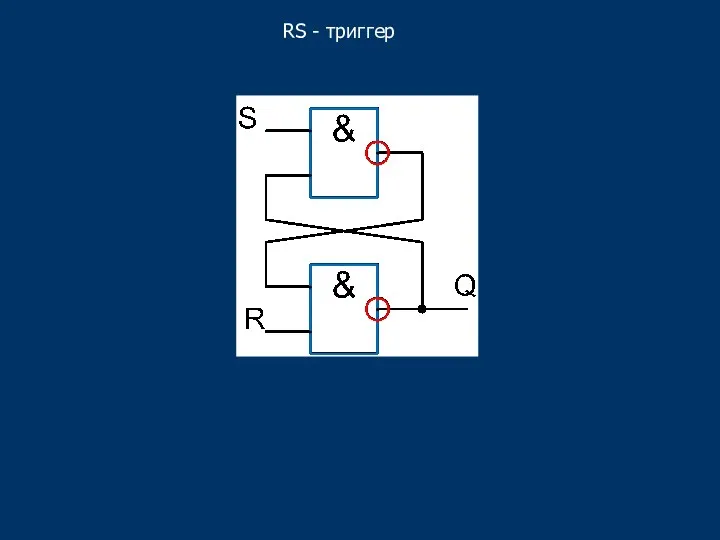

- 40. RS - триггер

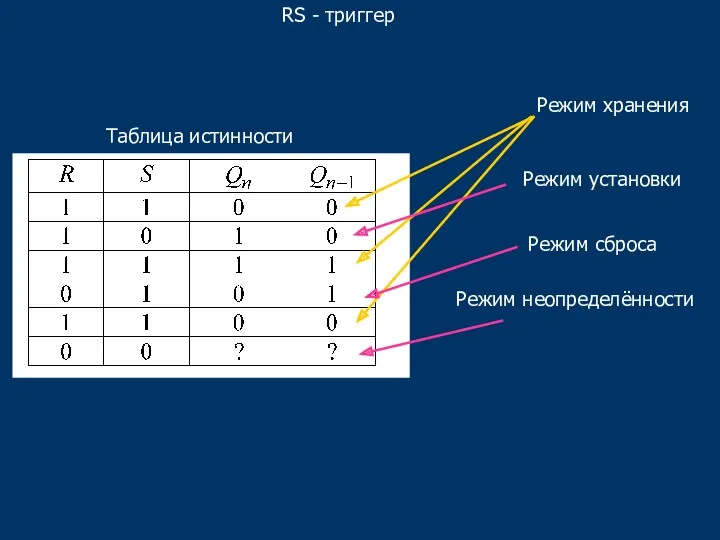

- 41. RS - триггер Таблица истинности Режим хранения Режим установки Режим сброса Режим неопределённости

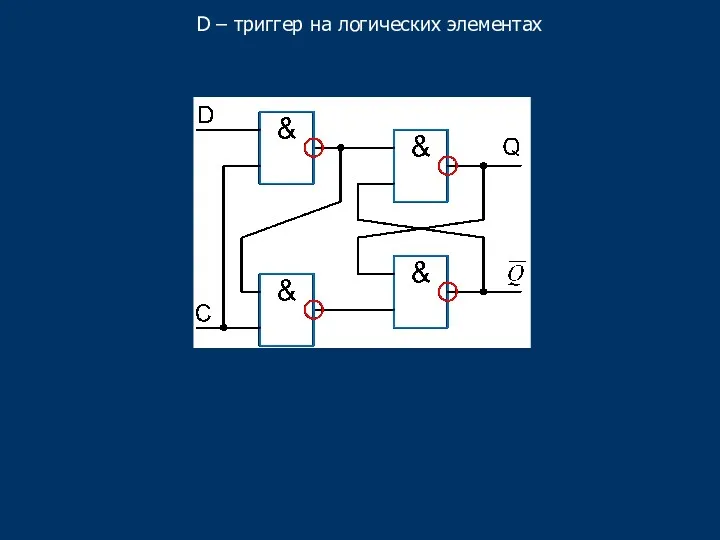

- 42. D – триггер на логических элементах

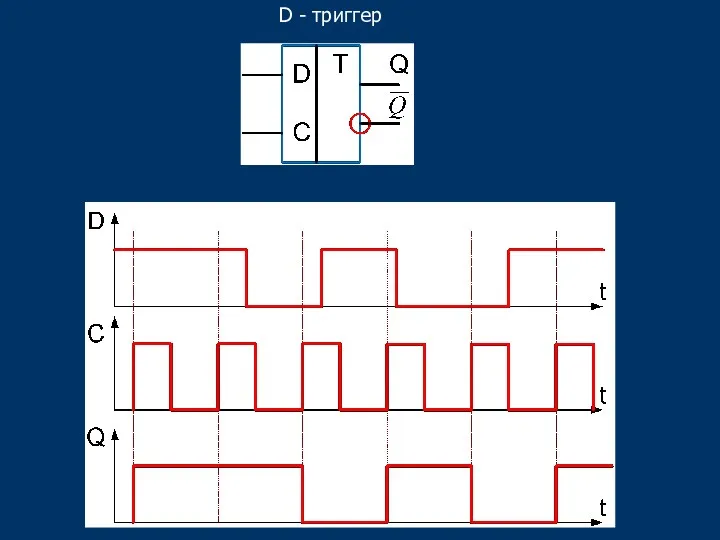

- 43. D - триггер

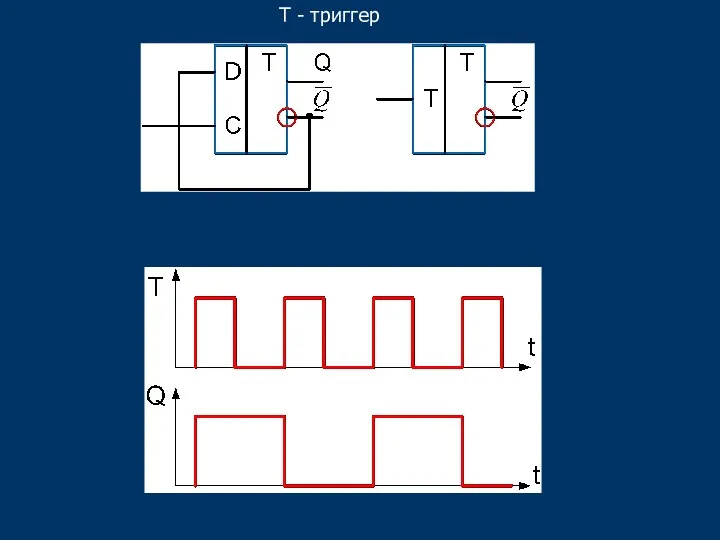

- 44. T - триггер

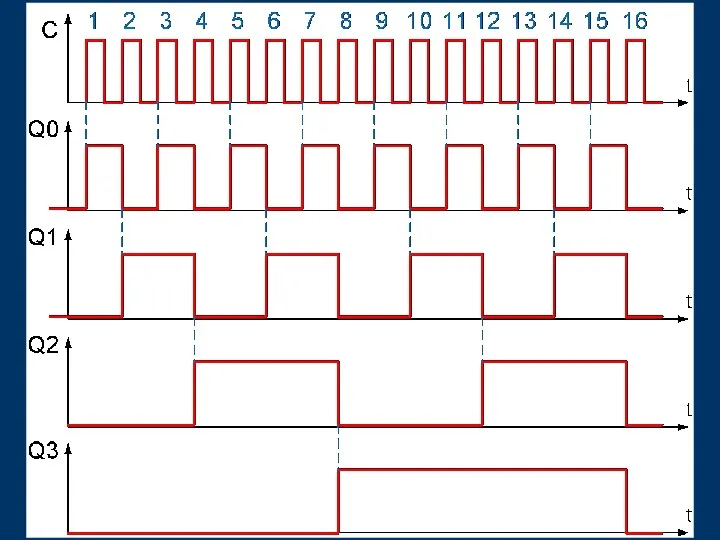

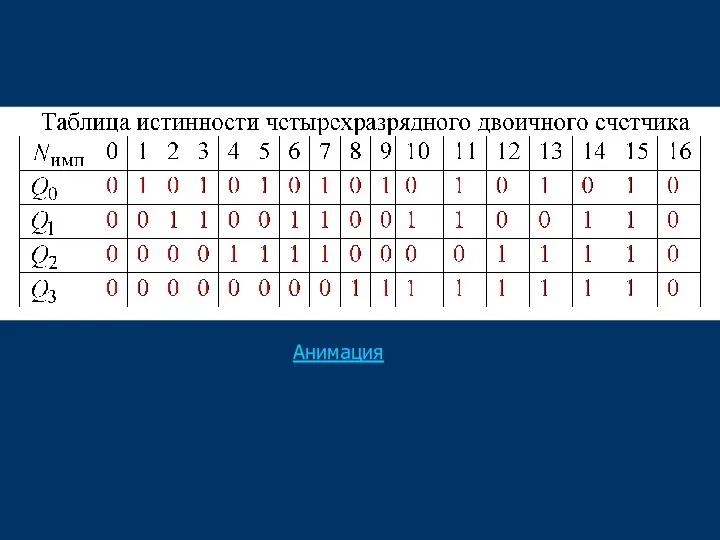

- 45. Двоичные счётчики

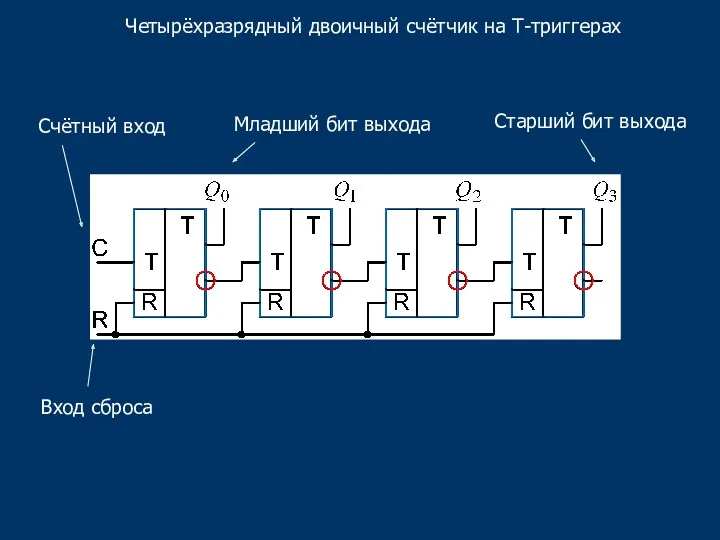

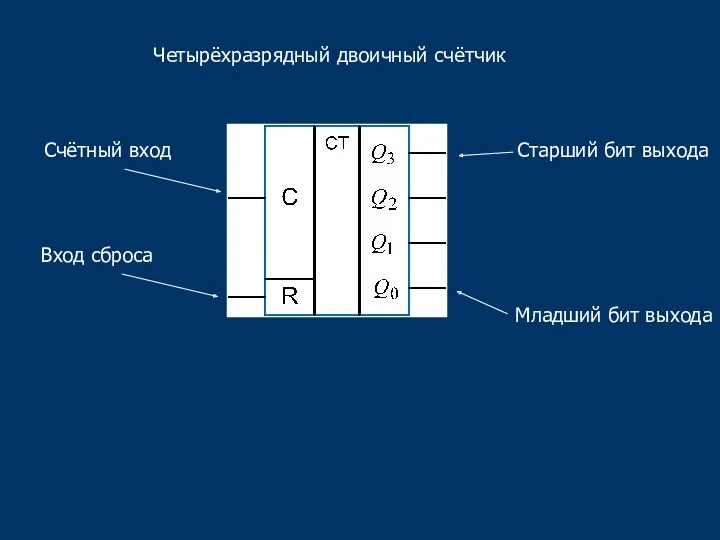

- 46. Четырёхразрядный двоичный счётчик на Т-триггерах Счётный вход Вход сброса Младший бит выхода Старший бит выхода

- 48. Четырёхразрядный двоичный счётчик Счётный вход Вход сброса Младший бит выхода Старший бит выхода

- 49. Анимация

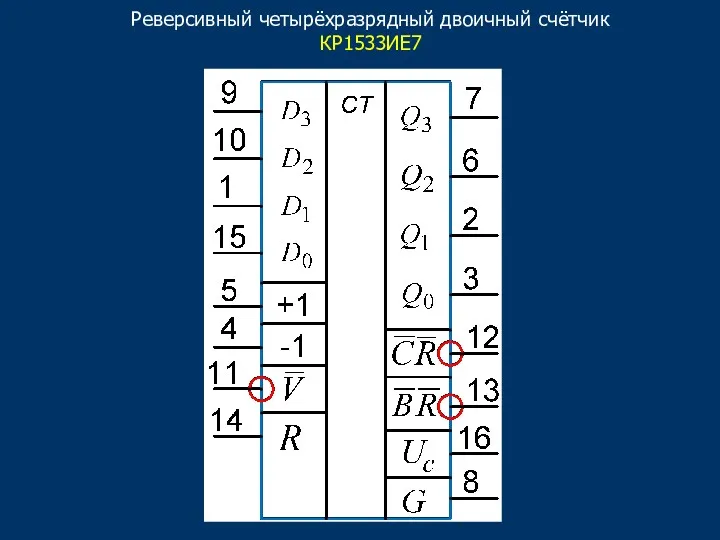

- 50. Реверсивный четырёхразрядный двоичный счётчик КР1533ИЕ7

- 51. Цифровые регистры

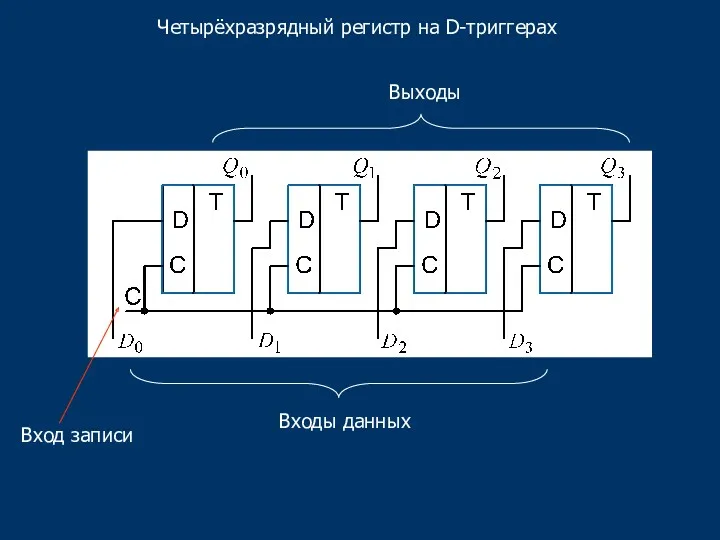

- 52. Четырёхразрядный регистр на D-триггерах Входы данных Выходы Вход записи

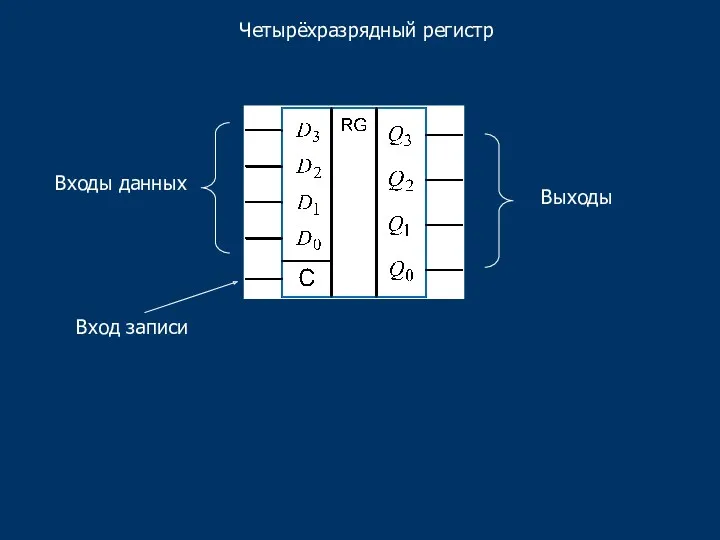

- 53. Четырёхразрядный регистр Входы данных Выходы Вход записи

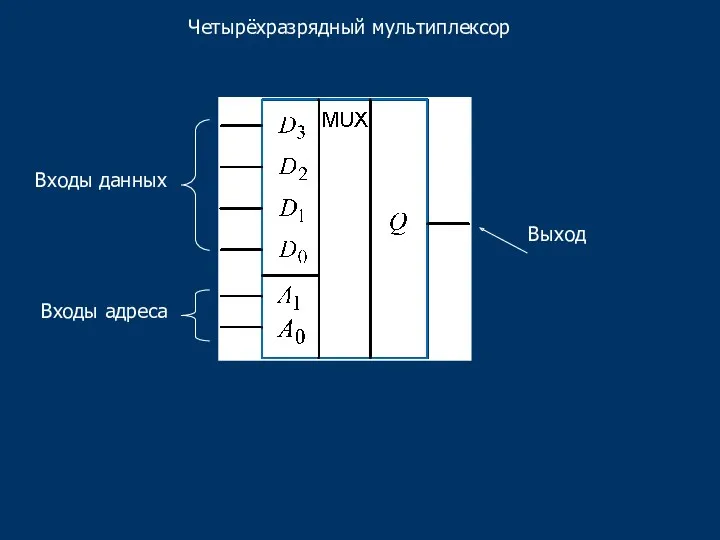

- 54. Цифровые мультиплексоры

- 55. Четырёхразрядный мультиплексор Входы данных Входы адреса Выход

- 57. Скачать презентацию

Демо версия 2009 ЕГЭ по химии

Демо версия 2009 ЕГЭ по химии Цветная металлургия мира

Цветная металлургия мира Русь у ХІ-ХІІІ століттях. Період усобиць, роздробленості та занепаду

Русь у ХІ-ХІІІ століттях. Період усобиць, роздробленості та занепаду Психологические основы творчества. Решение педагогических ситуаций

Психологические основы творчества. Решение педагогических ситуаций Родительское собрание Мир подростка

Родительское собрание Мир подростка ВИКТОРИНА ДЛЯ НАСТОЯЩИХ И БУДУЩИХ УЧИТЕЛЕЙ

ВИКТОРИНА ДЛЯ НАСТОЯЩИХ И БУДУЩИХ УЧИТЕЛЕЙ Технология написания сочинения по заданному тексту. ЕГЭ 2020

Технология написания сочинения по заданному тексту. ЕГЭ 2020 Реформы управления Петра I

Реформы управления Петра I Звук [Ч]. Буква Ч

Звук [Ч]. Буква Ч День защитника Отечества Диск

День защитника Отечества Диск Параметры Excel

Параметры Excel ПАЛЬЦЕХОД - логопособие своими руками.

ПАЛЬЦЕХОД - логопособие своими руками. Пилюлялар дәрілік түр ретінде. Пилюлялар дайындау үшін қолданылатын көмекші заттар

Пилюлялар дәрілік түр ретінде. Пилюлялар дайындау үшін қолданылатын көмекші заттар Air conditioning system (HD)

Air conditioning system (HD) Показательные уравнения. 10 класс

Показательные уравнения. 10 класс Подготовка природных газов к переработке

Подготовка природных газов к переработке Методы диагностики ИБС в амбулаторных условиях

Методы диагностики ИБС в амбулаторных условиях Комбинаторика. Перестановки. Размещение. Сочетание

Комбинаторика. Перестановки. Размещение. Сочетание Глобализация, её проявления и последствия

Глобализация, её проявления и последствия Топографическая анатомия и оперативная хирургия органов таза и забрюшинного пространства

Топографическая анатомия и оперативная хирургия органов таза и забрюшинного пространства Международные организации.

Международные организации. Желудок и поджелудочная железа. Очищение

Желудок и поджелудочная железа. Очищение Қытай. Мемлекеттегі темір жол көлігі және оның ерекшеліктері

Қытай. Мемлекеттегі темір жол көлігі және оның ерекшеліктері Смысловые типы текста

Смысловые типы текста Класс Насекомые. Внешнее строение насекомых. Внутреннее строение майского жука

Класс Насекомые. Внешнее строение насекомых. Внутреннее строение майского жука Презентация Педагогическая этика воспитателя

Презентация Педагогическая этика воспитателя Критерии подобия. Подобие течений неоднородных жидкостей в пористой среде при линейном законе сопротивления

Критерии подобия. Подобие течений неоднородных жидкостей в пористой среде при линейном законе сопротивления Легализация (отмывание) денежных средств. Современное состояние и предупреждение

Легализация (отмывание) денежных средств. Современное состояние и предупреждение