Содержание

- 2. Общие принципы функционирования КП Кэш-память – представляет собой организованную в виде ассоциативного запоминающего устройства, быстродействующую буферную

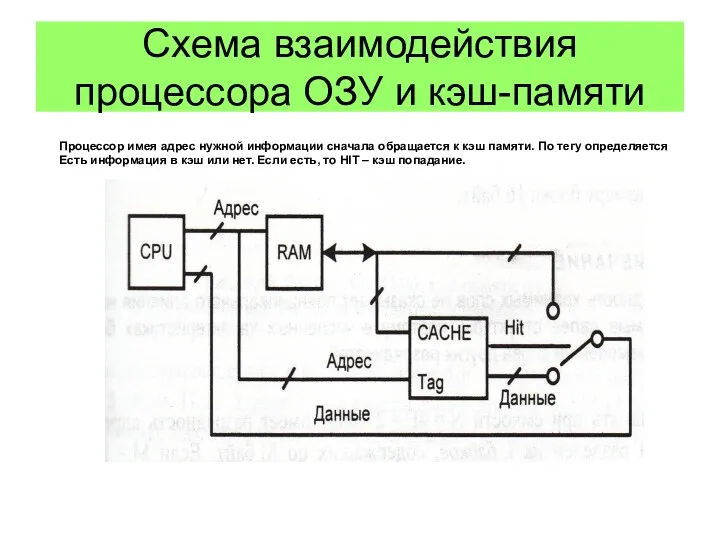

- 3. Схема взаимодействия процессора ОЗУ и кэш-памяти Процессор имея адрес нужной информации сначала обращается к кэш памяти.

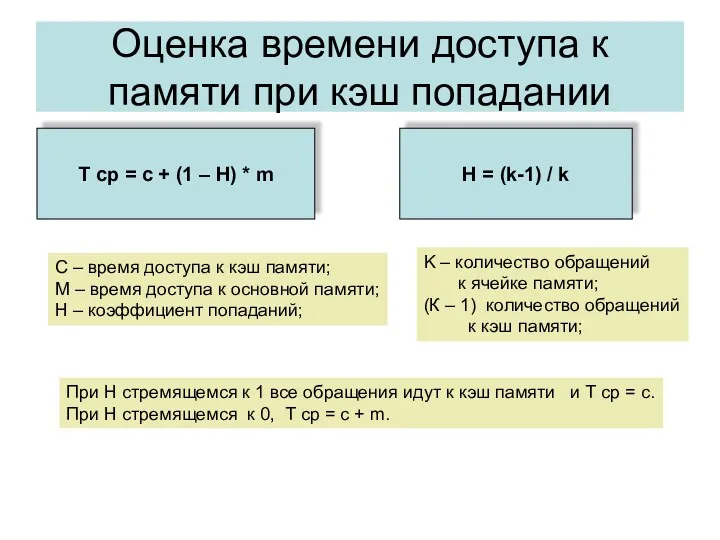

- 4. Оценка времени доступа к памяти при кэш попадании Т ср = с + (1 – Н)

- 5. Факторы влияющие на эффективность применения кэш памяти Емкость кэш-памяти. Формат строки. Способ отображения основной памяти на

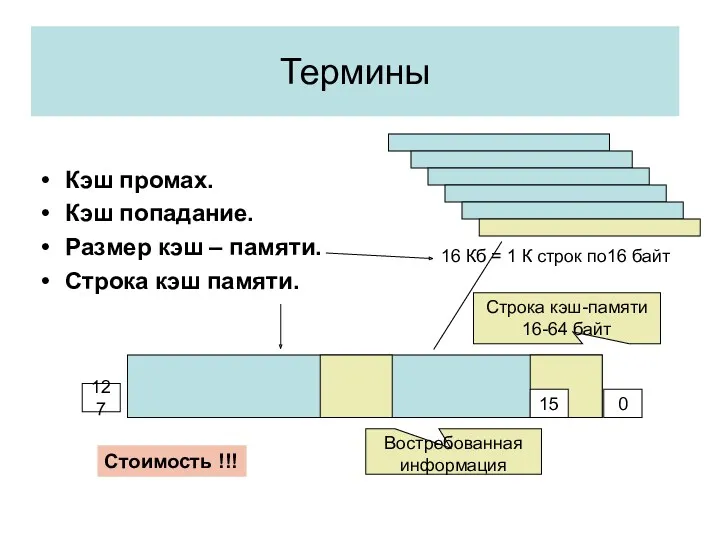

- 6. Термины Кэш промах. Кэш попадание. Размер кэш – памяти. Строка кэш памяти. Строка кэш-памяти 16-64 байт

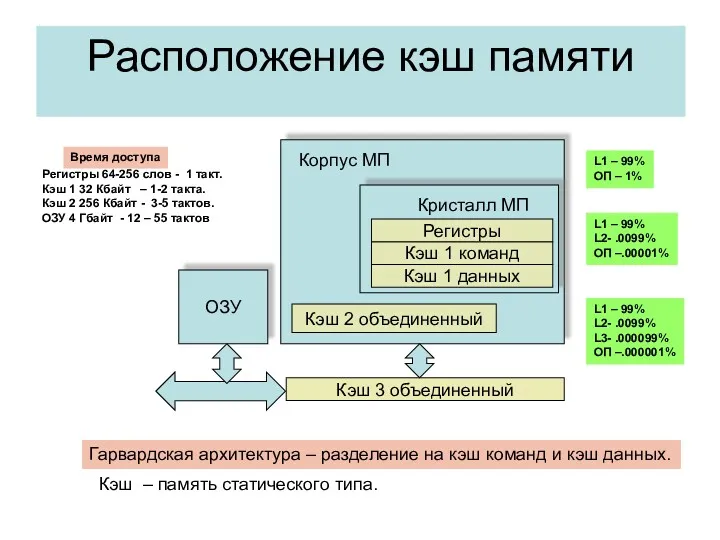

- 7. Расположение кэш памяти Кристалл МП Корпус МП Кэш 1 команд Кэш 2 объединенный Кэш 3 объединенный

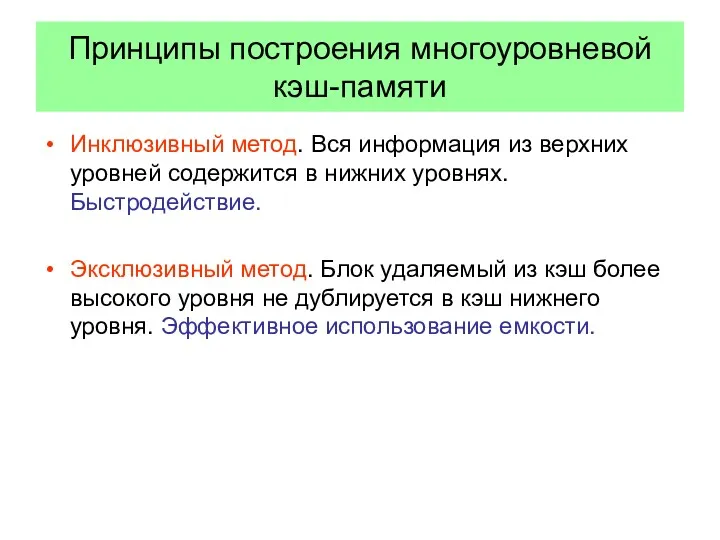

- 8. Принципы построения многоуровневой кэш-памяти Инклюзивный метод. Вся информация из верхних уровней содержится в нижних уровнях. Быстродействие.

- 9. Классификация КЭШ по способу отображения основной памяти Кэш память прямого отображения. Кэш память ассоциативная с множественным

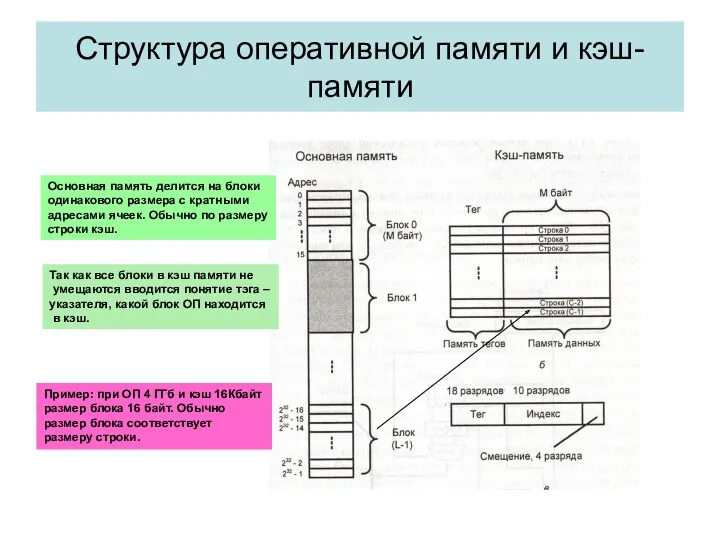

- 10. Структура оперативной памяти и кэш-памяти Основная память делится на блоки одинакового размера с кратными адресами ячеек.

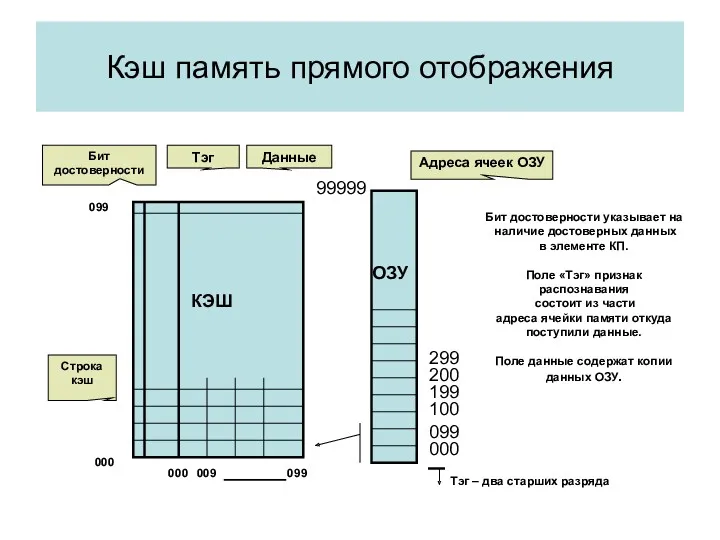

- 11. Кэш память прямого отображения Строка кэш Бит достоверности Тэг Данные Адреса ячеек ОЗУ Бит достоверности указывает

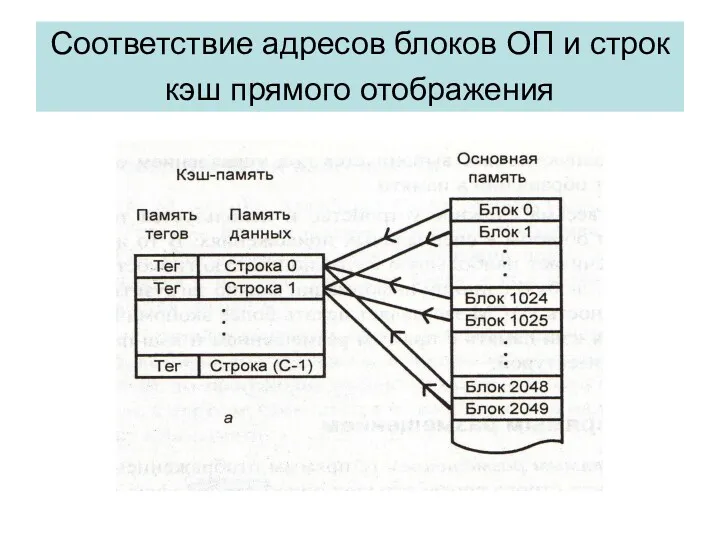

- 12. Соответствие адресов блоков ОП и строк кэш прямого отображения

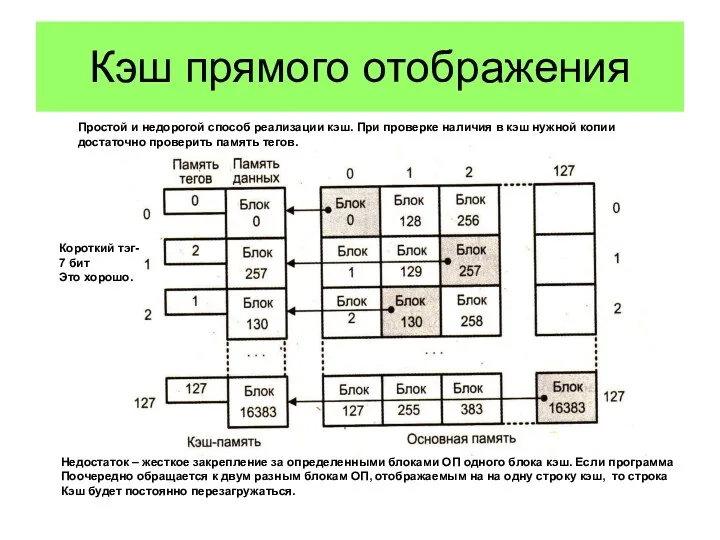

- 13. Кэш прямого отображения Простой и недорогой способ реализации кэш. При проверке наличия в кэш нужной копии

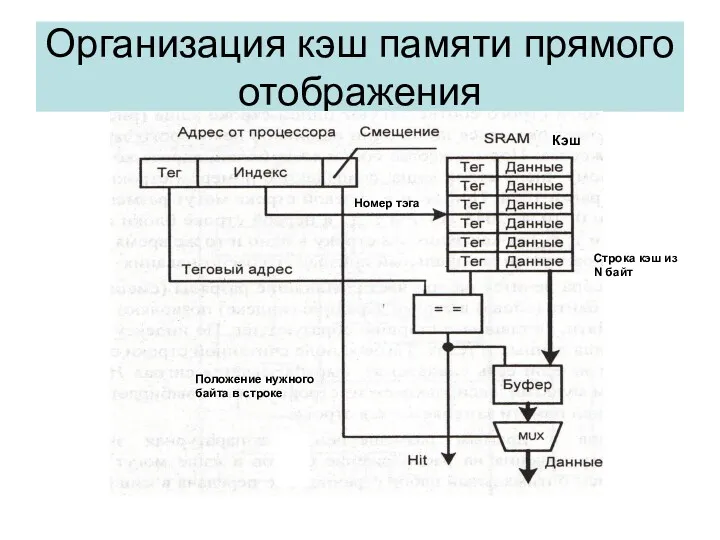

- 14. Организация кэш памяти прямого отображения Кэш Номер тэга Положение нужного байта в строке Строка кэш из

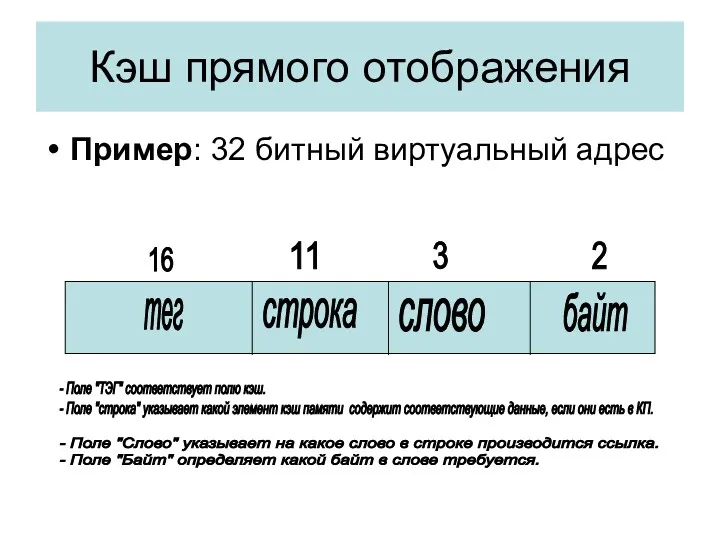

- 15. Кэш прямого отображения Пример: 32 битный виртуальный адрес тег строка слово байт 16 11 3 2

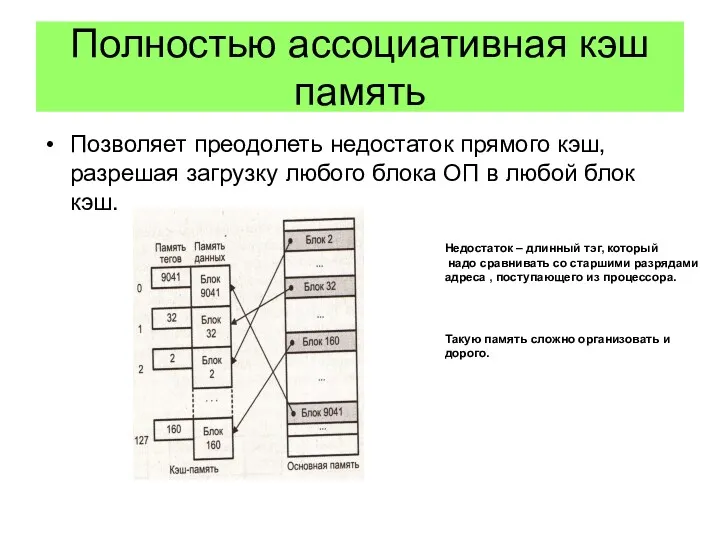

- 16. Полностью ассоциативная кэш память Позволяет преодолеть недостаток прямого кэш, разрешая загрузку любого блока ОП в любой

- 17. Организация полностью ассоциативной кэш памяти Любая ячейка ОЗУ может находится в любом месте КЭШа. Сложная структура,

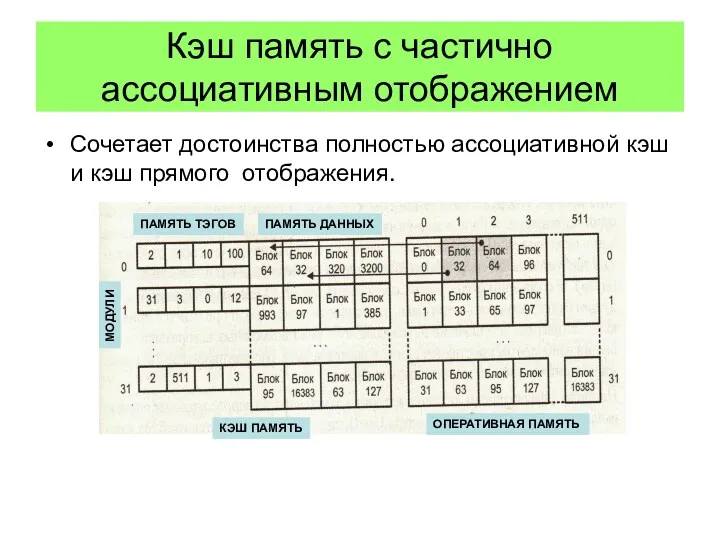

- 18. Кэш память с частично ассоциативным отображением Сочетает достоинства полностью ассоциативной кэш и кэш прямого отображения. КЭШ

- 19. Соответствие блоков ОП и строк частично-ассоциативной кэш

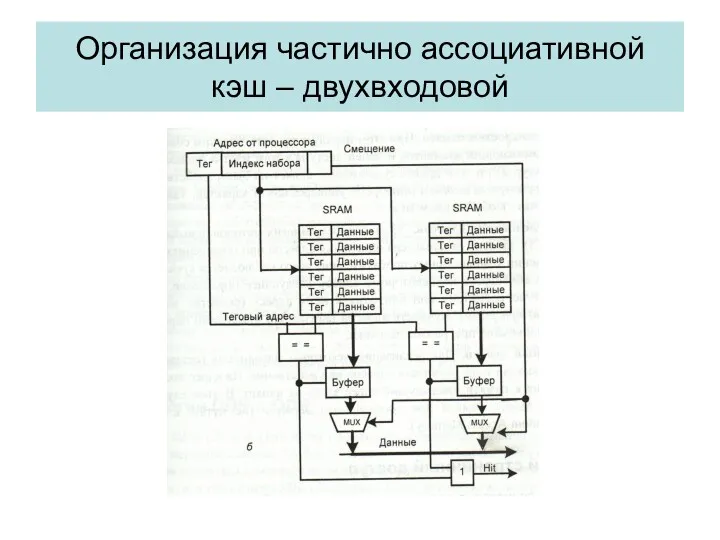

- 20. Организация частично ассоциативной кэш – двухвходовой

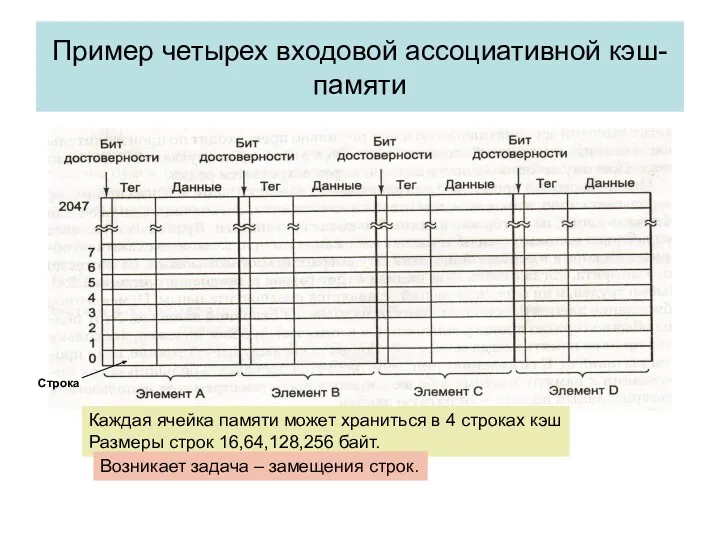

- 21. Пример четырех входовой ассоциативной кэш-памяти Каждая ячейка памяти может храниться в 4 строках кэш Размеры строк

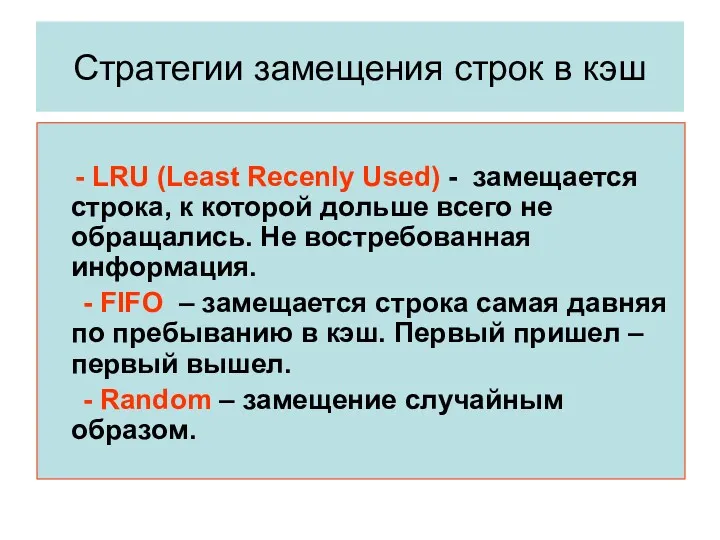

- 22. Стратегии замещения строк в кэш - LRU (Least Recenly Used) - замещается строка, к которой дольше

- 23. Структура внутренней Кэш памяти МП i486 B0 B1 B2 V0 V1 V2 V3 1 1 1

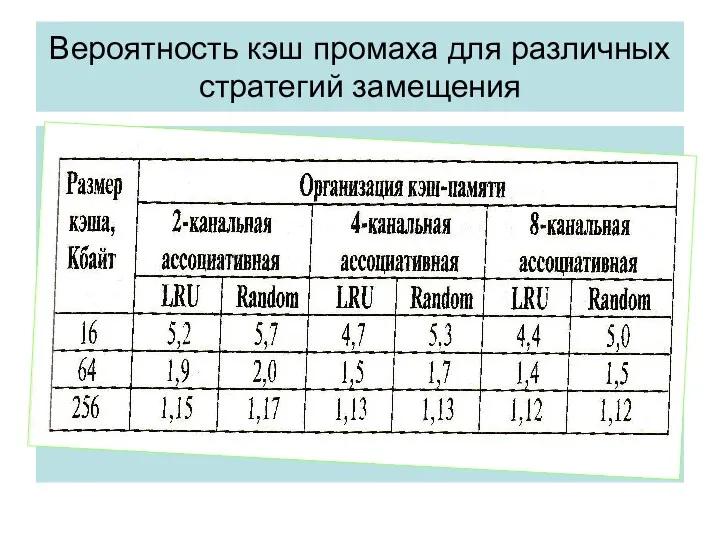

- 24. Вероятность кэш промаха для различных стратегий замещения

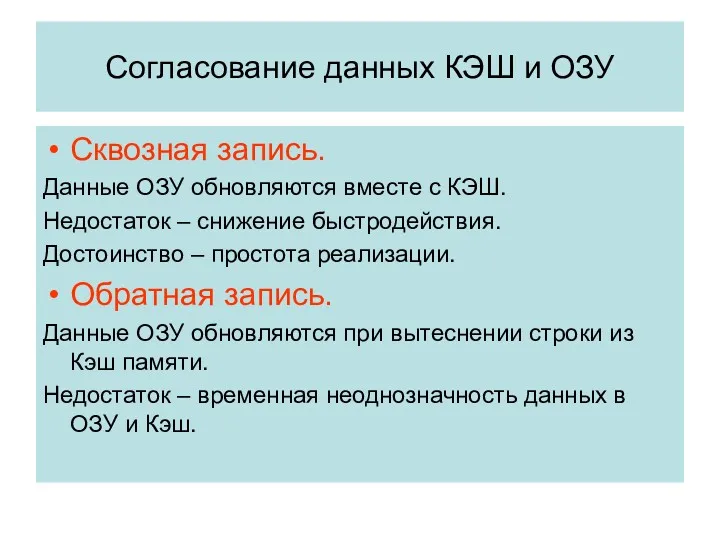

- 25. Согласование данных КЭШ и ОЗУ Сквозная запись. Данные ОЗУ обновляются вместе с КЭШ. Недостаток – снижение

- 26. Режим работы кэш Задается программной установкой разрядов CD (запрет кэширования) и NW (запрет сквозной записи) в

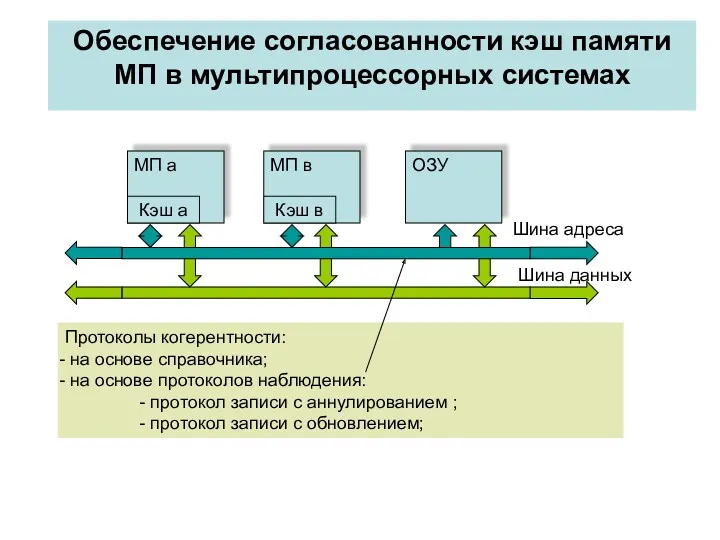

- 27. Обеспечение согласованности кэш памяти МП в мультипроцессорных системах МП а МП в ОЗУ Кэш а Кэш

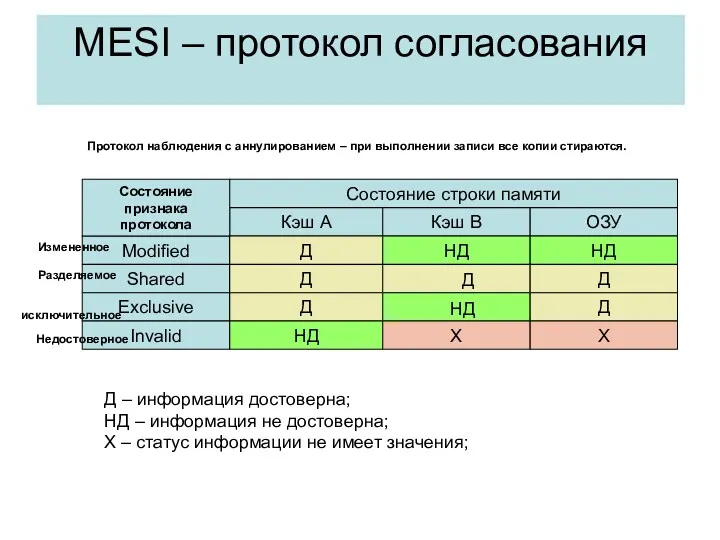

- 28. MESI – протокол согласования Кэш А Д Д Д НД Кэш В НД Х ОЗУ НД

- 30. Скачать презентацию

12 апреля. День космонавтики.

12 апреля. День космонавтики. Financier - is a specialist managing money

Financier - is a specialist managing money Аппликация кораблик. Поэтапное изготовление

Аппликация кораблик. Поэтапное изготовление Проходження практики на підприємстві Оризон-Навігація

Проходження практики на підприємстві Оризон-Навігація Взаимное расположение прямой и окружности на плоскости

Взаимное расположение прямой и окружности на плоскости Меланин түзуші ұлпаның,жүйке ұлпасының ісіктері,күрделі ісіктер

Меланин түзуші ұлпаның,жүйке ұлпасының ісіктері,күрделі ісіктер Урок по Географии Алтайского края 8 класс тема: Растительность Алтайского края

Урок по Географии Алтайского края 8 класс тема: Растительность Алтайского края Презентация к родительскому собранию Агрессия. Игры на снижение агрессии.

Презентация к родительскому собранию Агрессия. Игры на снижение агрессии. Объемные изображение в скульптуре

Объемные изображение в скульптуре Монтаж строительных конструкций

Монтаж строительных конструкций Вены большого круга кровообращения

Вены большого круга кровообращения Состояние травматизма в организациях Лысьвенского городского округа

Состояние травматизма в организациях Лысьвенского городского округа Исторические аспекты коррупции в России. Тема 2

Исторические аспекты коррупции в России. Тема 2 Автоматизация звука Ж (1-2 класс).

Автоматизация звука Ж (1-2 класс). Закупочная логистика. Сущность и задачи закупочной логистики

Закупочная логистика. Сущность и задачи закупочной логистики Трехфазные цепи переменного синусоидального тока

Трехфазные цепи переменного синусоидального тока Наиболее типичные заболевания и травмы в игровых видах спорта. Методика массажа

Наиболее типичные заболевания и травмы в игровых видах спорта. Методика массажа Выращивание кристаллов в домашних условиях

Выращивание кристаллов в домашних условиях Основные средства предприятия

Основные средства предприятия Баскетбол

Баскетбол Экономическая точность обработки. Методология разработки технологических процессов

Экономическая точность обработки. Методология разработки технологических процессов Презентация 38 1 группа

Презентация 38 1 группа Event-менеджмент

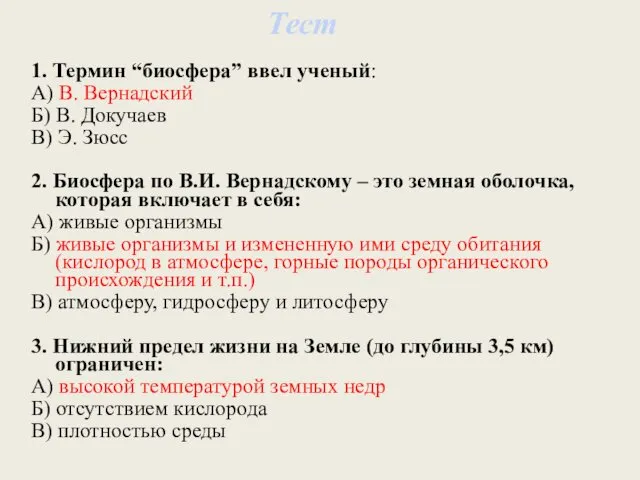

Event-менеджмент Биосфера Земли. Тест

Биосфера Земли. Тест Проектная деятельность в ДОУ

Проектная деятельность в ДОУ Презентация Здравствуй, лето! (Загадки)

Презентация Здравствуй, лето! (Загадки) Тренинг Искусство быть счастливой

Тренинг Искусство быть счастливой Основные понятия химии высокомолекулярных соединений (ВМС)

Основные понятия химии высокомолекулярных соединений (ВМС)