Содержание

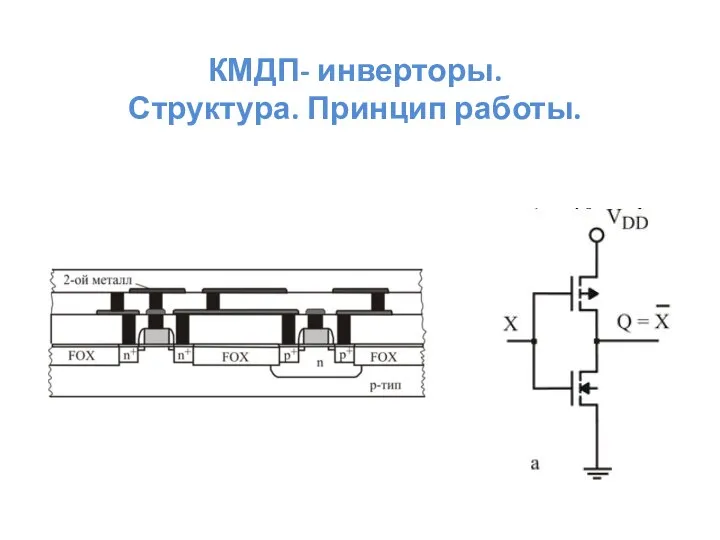

- 2. КМДП- инверторы. Структура. Принцип работы.

- 3. ОСНОВНЫЕ ДОСТОИНСТВА КМДП-СХЕМ Потребление мощности в статическом состоянии пренебрежимо мало Высокая помехоустойчивость (т.к. U0= 0, U1

- 4. Передаточная характеристика в КМДП-схеме Задачи Дано: KP, W, L, Uип Определить выходной ток МДП-транзистора в любой

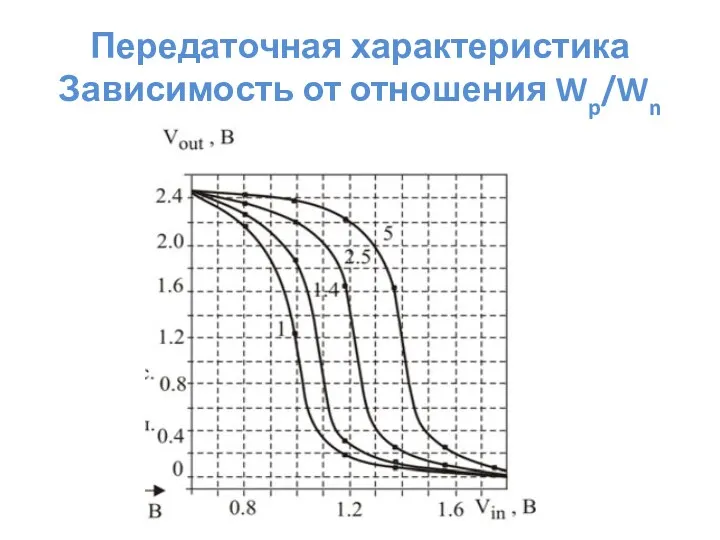

- 5. Передаточная характеристика Зависимость от отношения Wp/Wn

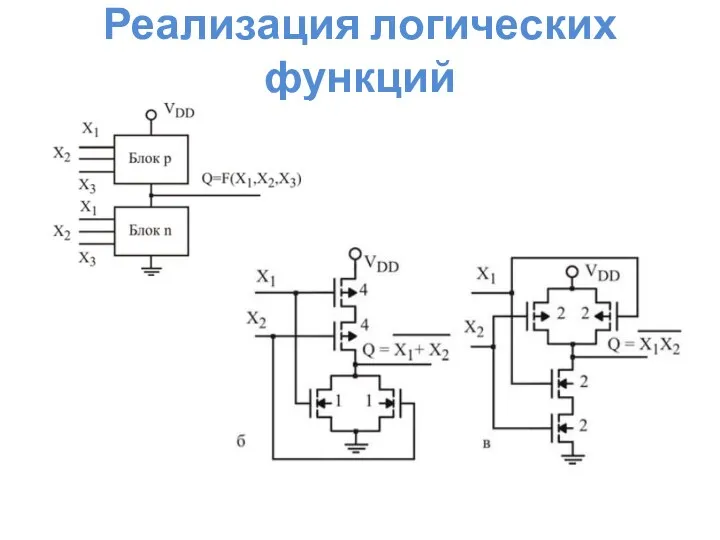

- 6. Реализация логических функций

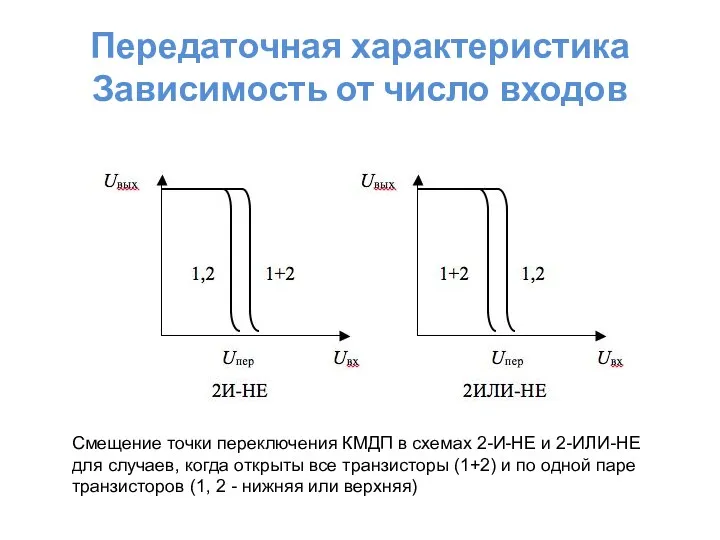

- 7. Передаточная характеристика Зависимость от число входов Смещение точки переключения КМДП в схемах 2-И-НЕ и 2-ИЛИ-НЕ для

- 8. Эффект защелки в КМДП- схемах

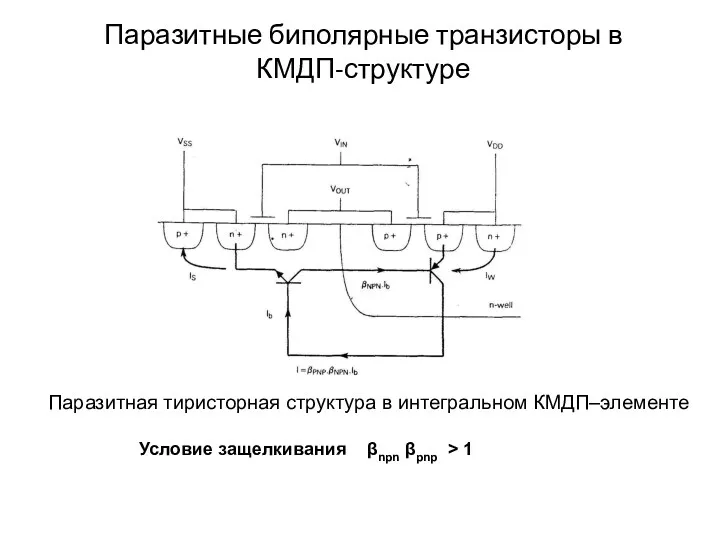

- 9. Паразитные биполярные транзисторы в КМДП-структуре Паразитная тиристорная структура в интегральном КМДП–элементе Условие защелкивания βnpn βpnp >

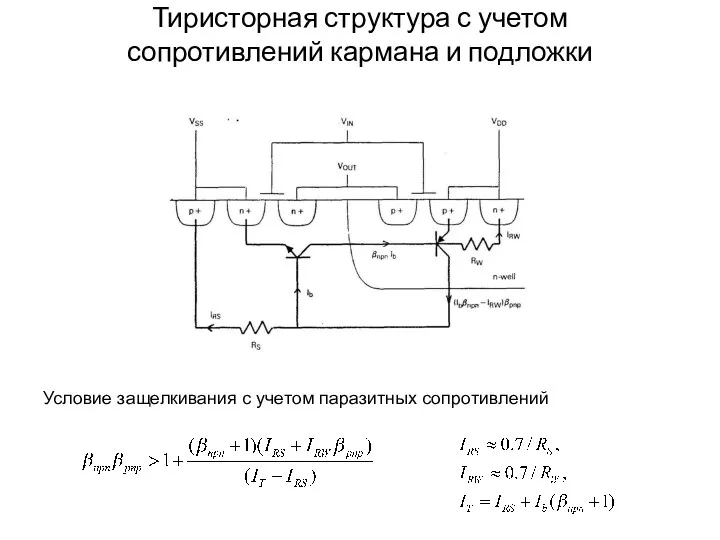

- 10. Тиристорная структура с учетом сопротивлений кармана и подложки Условие защелкивания с учетом паразитных сопротивлений

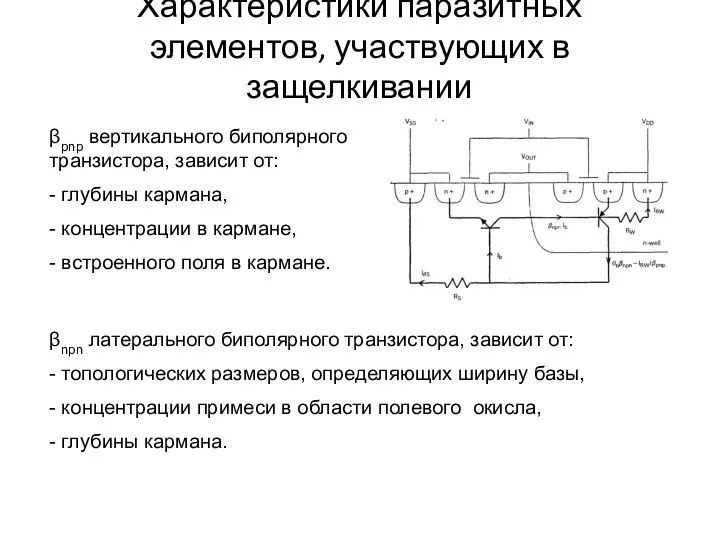

- 11. Характеристики паразитных элементов, участвующих в защелкивании βpnp вертикального биполярного транзистора, зависит от: - глубины кармана, -

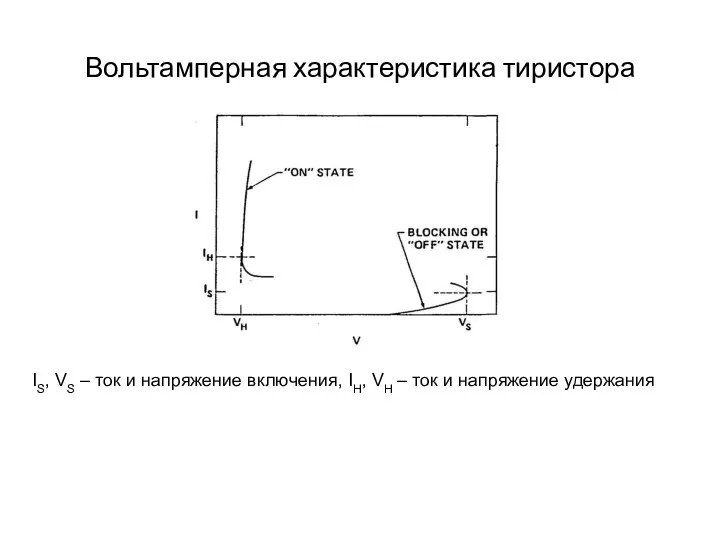

- 12. Вольтамперная характеристика тиристора IS, VS – ток и напряжение включения, IH, VH – ток и напряжение

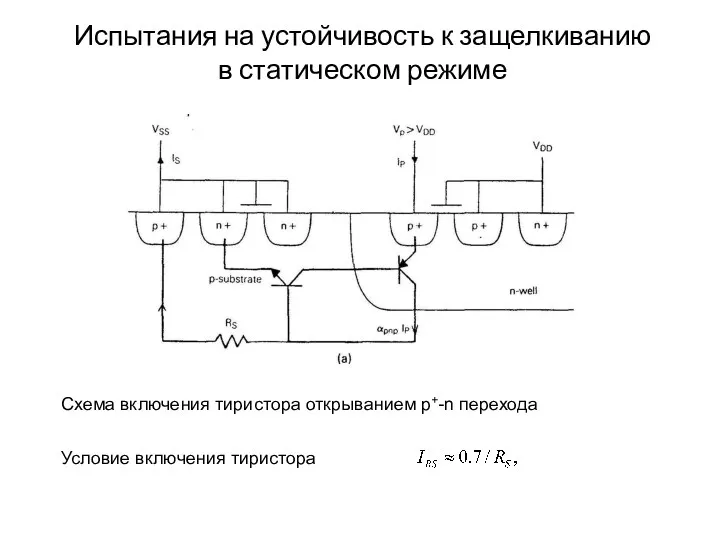

- 13. Испытания на устойчивость к защелкиванию в статическом режиме Схема включения тиристора открыванием p+-n перехода Условие включения

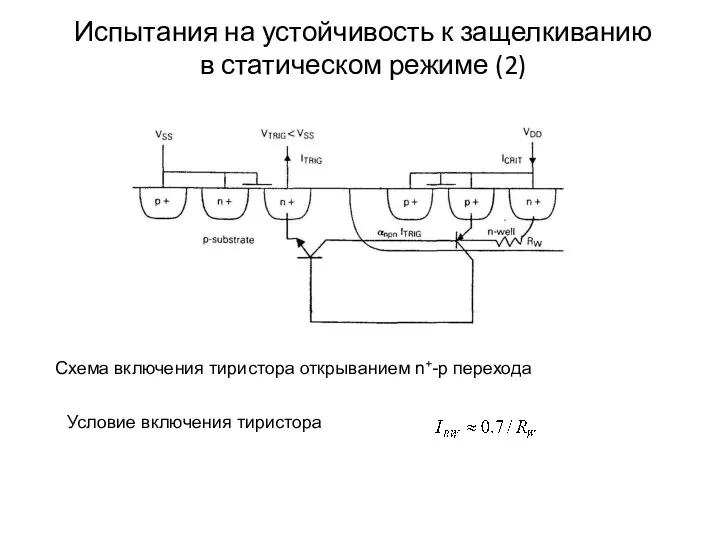

- 14. Испытания на устойчивость к защелкиванию в статическом режиме (2) Схема включения тиристора открыванием n+-p перехода Условие

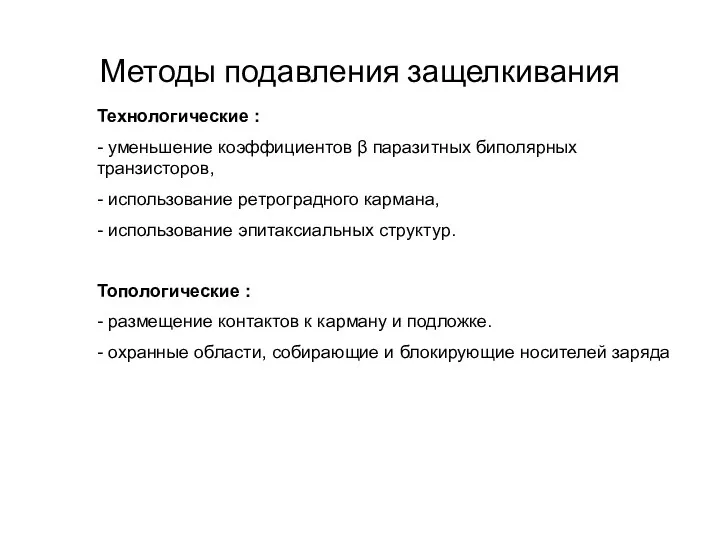

- 15. Методы подавления защелкивания Технологические : - уменьшение коэффициентов β паразитных биполярных транзисторов, - использование ретроградного кармана,

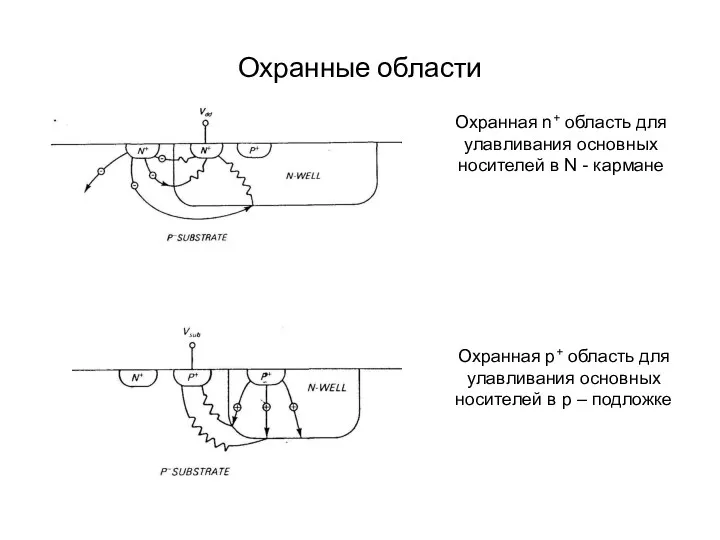

- 16. Охранные области Охранная n+ область для улавливания основных носителей в N - кармане Охранная p+ область

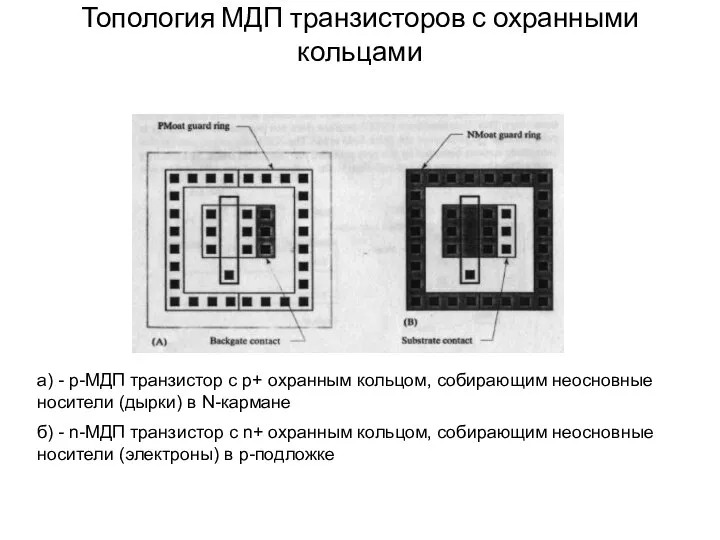

- 17. Топология МДП транзисторов с охранными кольцами а) - p-МДП транзистор с p+ охранным кольцом, собирающим неосновные

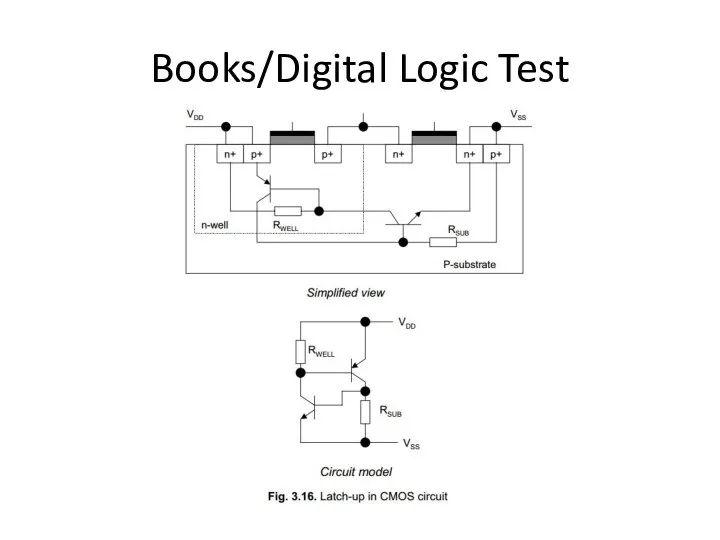

- 18. Books/Digital Logic Test

- 19. Схемотехнические модели МДП-транзисторов

- 20. Эквивалентная схема PSPIСE модели МДП транзистора LEVEL=1, 2, 3…

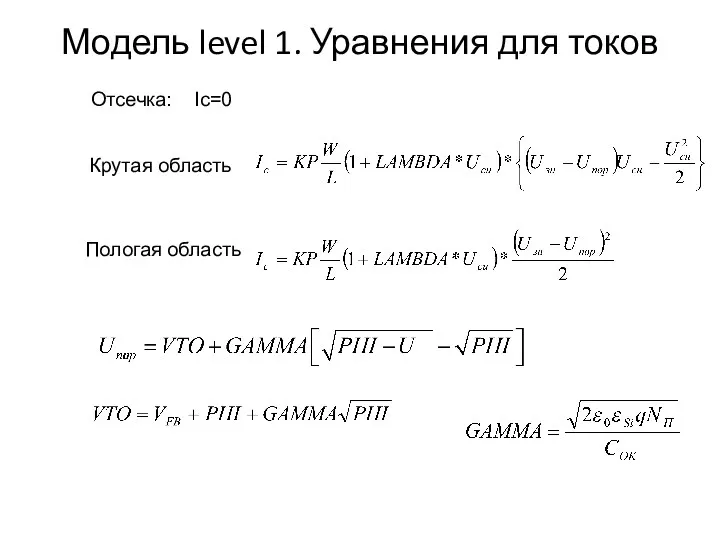

- 21. Модель level 1. Уравнения для токов Отсечка: Ic=0 Крутая область Пологая область

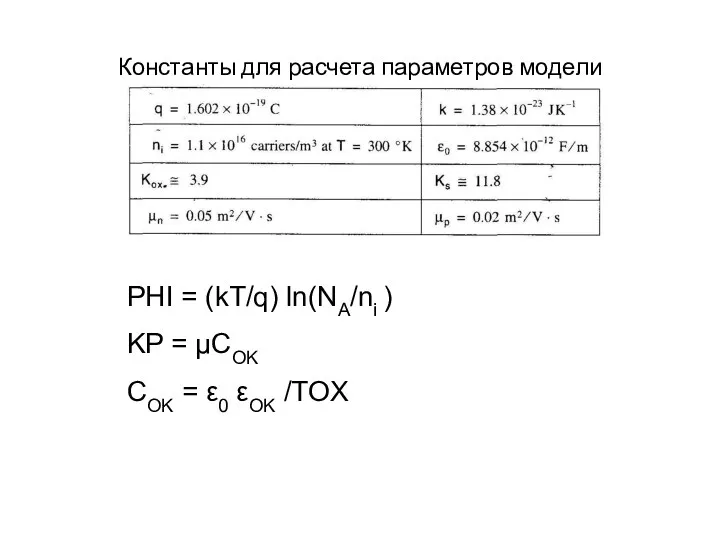

- 22. Константы для расчета параметров модели PHI = (kT/q) ln(NA/ni ) KP = μCOK COK = ε0

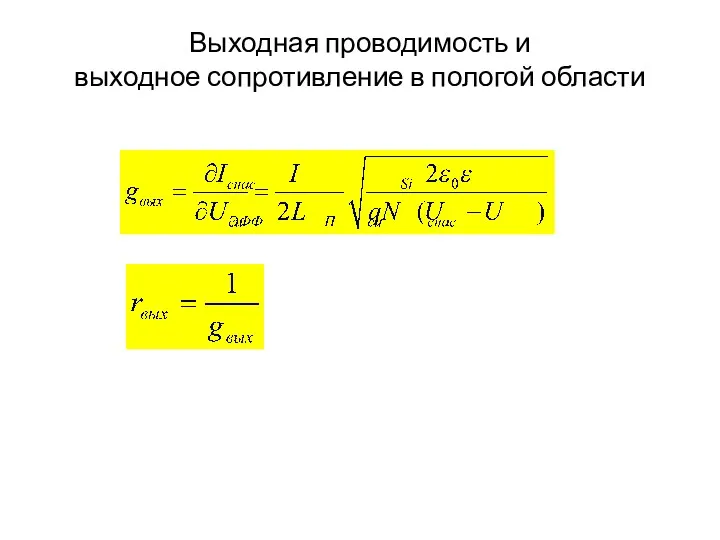

- 23. Выходная проводимость и выходное сопротивление в пологой области

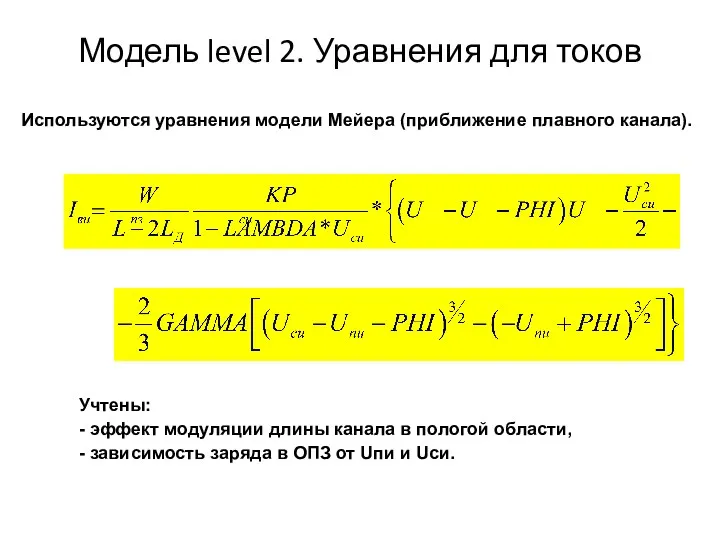

- 24. Модель level 2. Уравнения для токов Используются уравнения модели Мейера (приближение плавного канала). Учтены: - эффект

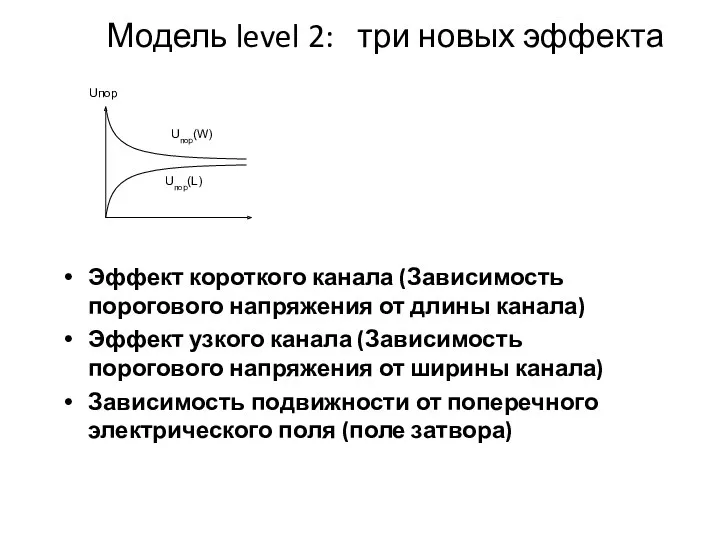

- 25. Модель level 2: три новых эффекта Эффект короткого канала (Зависимость порогового напряжения от длины канала) Эффект

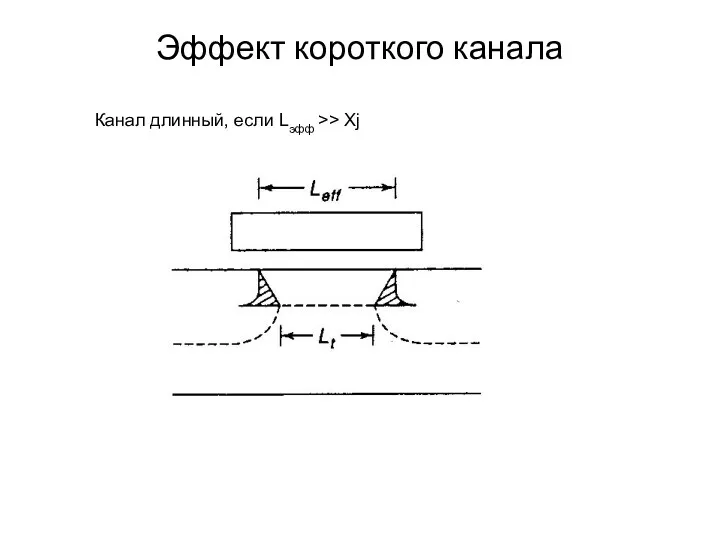

- 26. Эффект короткого канала Канал длинный, если Lэфф >> Xj

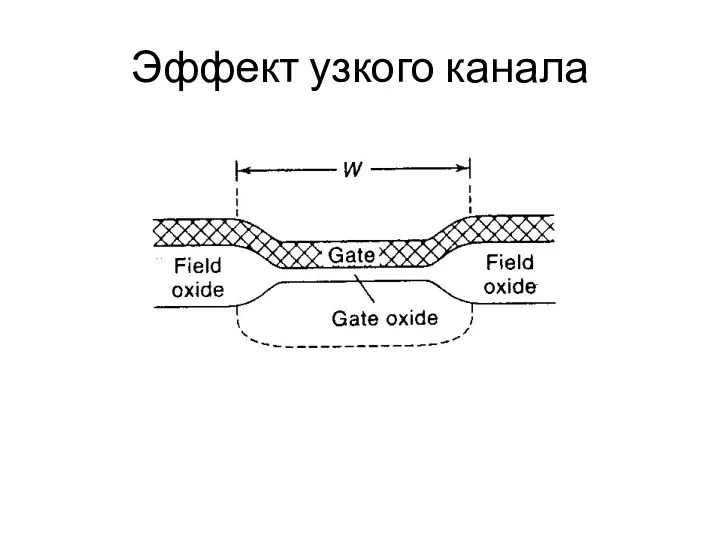

- 27. Эффект узкого канала

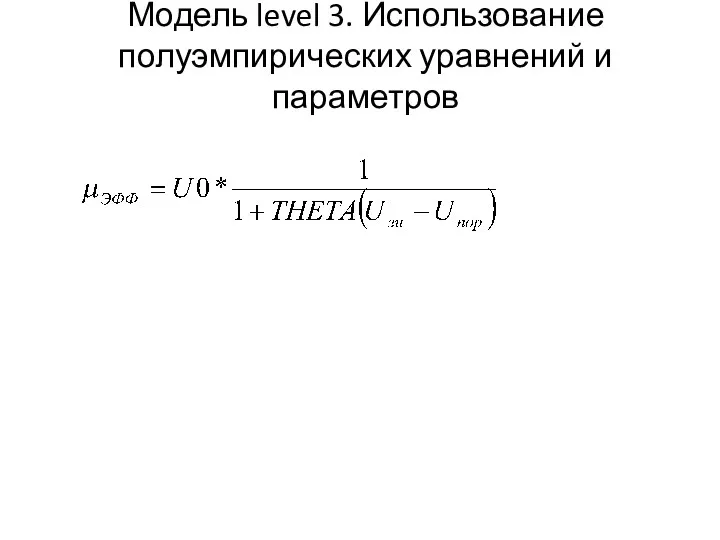

- 28. Модель level 3. Использование полуэмпирических уравнений и параметров

- 30. Скачать презентацию

Дизайн и архитектура моего сада. 7 класс

Дизайн и архитектура моего сада. 7 класс Разработка и экономическое обоснование экскурсионного маршрута

Разработка и экономическое обоснование экскурсионного маршрута Профессия - полицейский.

Профессия - полицейский. Кафе быстрого обслуживания Dio Cafe

Кафе быстрого обслуживания Dio Cafe Строение атома

Строение атома Общие особенности античной философии

Общие особенности античной философии Урок технологии швейного дела

Урок технологии швейного дела Что такое учебный проект

Что такое учебный проект Биохимические методы исследования,используемые в эндокринологии,в норме и в патологии,иетерпретация результатов

Биохимические методы исследования,используемые в эндокринологии,в норме и в патологии,иетерпретация результатов День профессий 2022

День профессий 2022 Пасха. Светлое Христово Воскресение

Пасха. Светлое Христово Воскресение Четыре замечательные точки треугольника

Четыре замечательные точки треугольника Портфолио Андрея Джеджулы

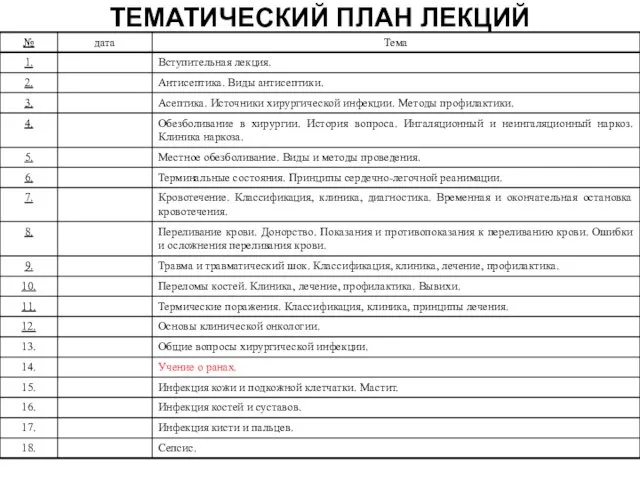

Портфолио Андрея Джеджулы Раны. Раневой процесс

Раны. Раневой процесс Component Enabler for .NET

Component Enabler for .NET Организационные формы обучения

Организационные формы обучения Успехи в освоении технологии за 6 класс

Успехи в освоении технологии за 6 класс ПОУ СКУИТ Северодвинский колледж управления и информационных технологий

ПОУ СКУИТ Северодвинский колледж управления и информационных технологий Мастер-класс для родителей Артикуляционная гимнастика

Мастер-класс для родителей Артикуляционная гимнастика сценарий и презентация праздника ко дню Победы. Я еще не хочу умирать

сценарий и презентация праздника ко дню Победы. Я еще не хочу умирать праздник Осени во 2 классе

праздник Осени во 2 классе презентация к занятию Земля - наш общий дом!

презентация к занятию Земля - наш общий дом! Шахта лифта в панельных зданиях. Опирание перекрытий на шахту лифта. (Тест 3.1)

Шахта лифта в панельных зданиях. Опирание перекрытий на шахту лифта. (Тест 3.1) Презентация Индийский океан

Презентация Индийский океан Русская Православная церковь. Страницы истории. Обзор

Русская Православная церковь. Страницы истории. Обзор Знатоки правил дорожного движения

Знатоки правил дорожного движения Международный валютный рынок

Международный валютный рынок Натюрморт в технике гризайль

Натюрморт в технике гризайль