Содержание

- 2. Логические операции «И», «ИЛИ», «НЕ» лежат в основе работы преобразователей информации любого компьютера американский математик, доказал

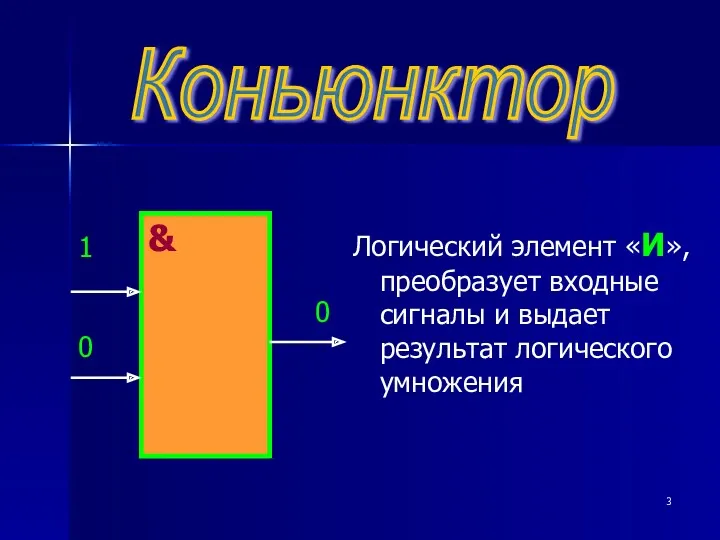

- 3. Коньюнктор Логический элемент «И», преобразует входные сигналы и выдает результат логического умножения

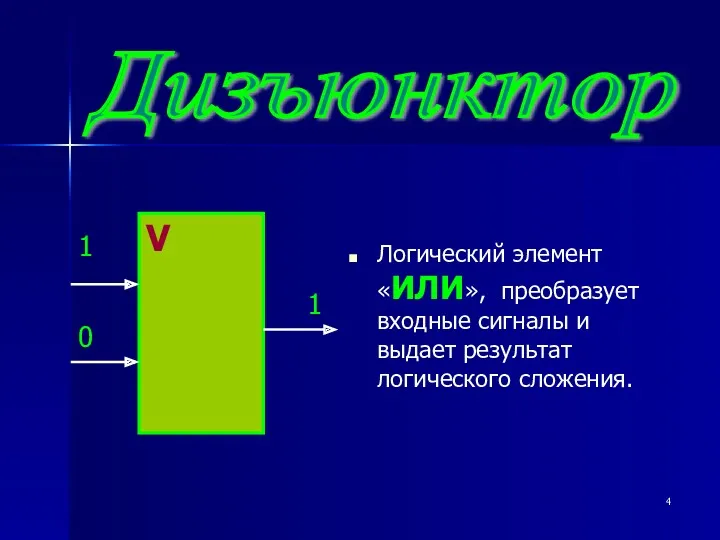

- 4. Дизъюнктор Логический элемент «ИЛИ», преобразует входные сигналы и выдает результат логического сложения.

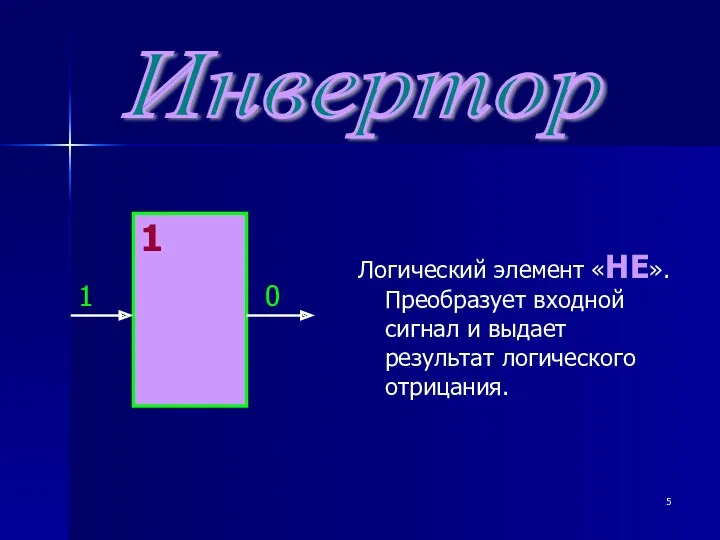

- 5. Инвертор Логический элемент «НЕ». Преобразует входной сигнал и выдает результат логического отрицания.

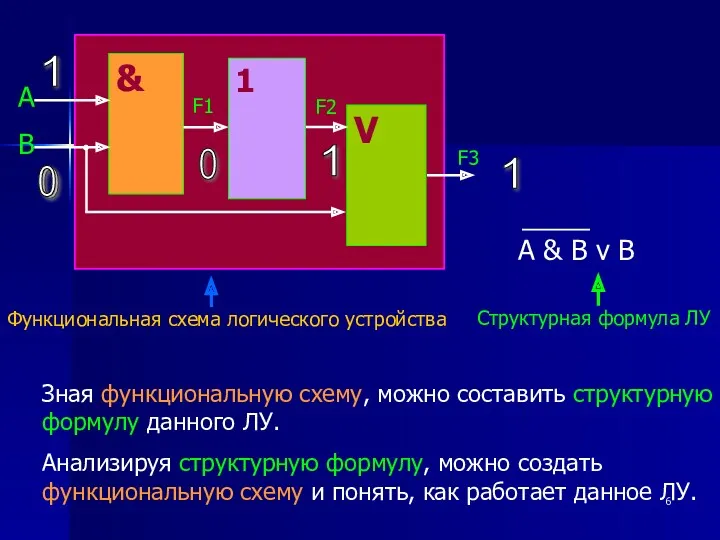

- 6. Функциональная схема логического устройства Структурная формула ЛУ & А В V 1 F1 F2 F3 Зная

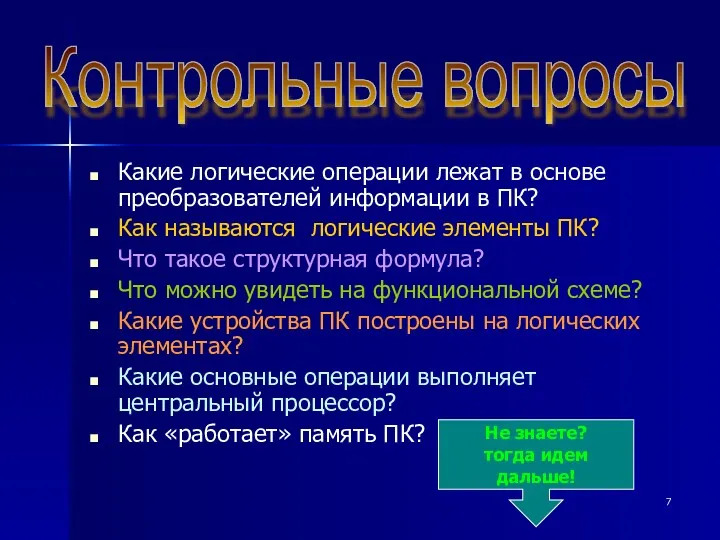

- 7. Какие логические операции лежат в основе преобразователей информации в ПК? Как называются логические элементы ПК? Что

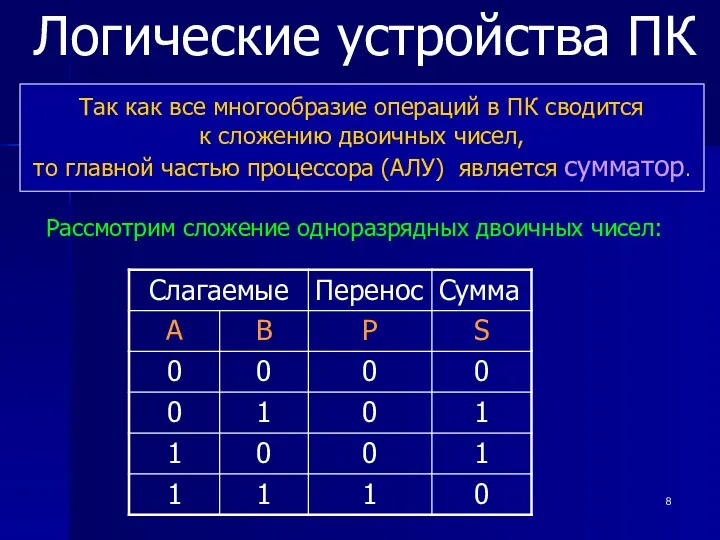

- 8. Так как все многообразие операций в ПК сводится к сложению двоичных чисел, то главной частью процессора

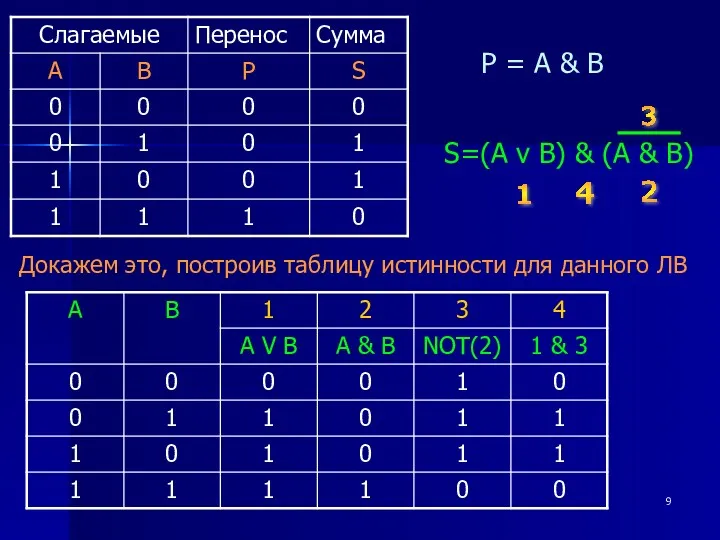

- 9. P = A & B Докажем это, построив таблицу истинности для данного ЛВ 1 2 3

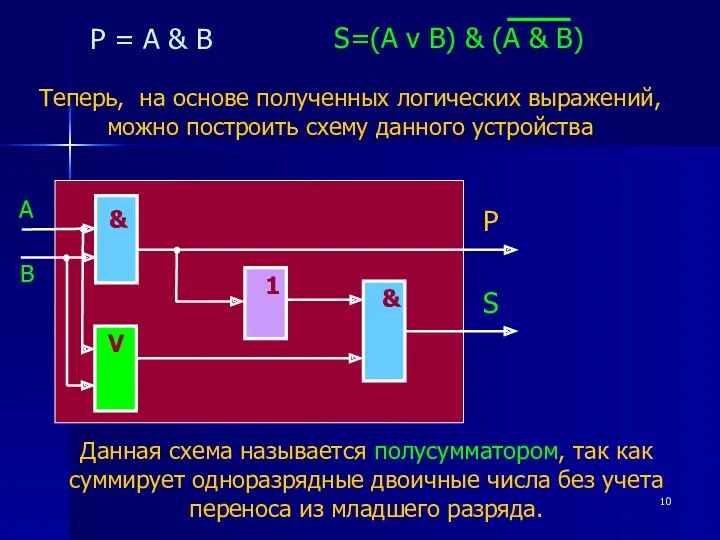

- 10. P = A & B Теперь, на основе полученных логических выражений, можно построить схему данного устройства

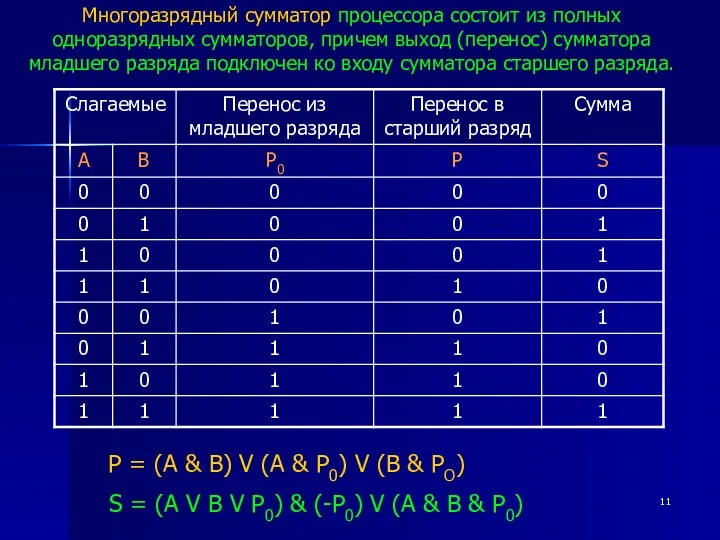

- 11. Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров, причем выход (перенос) сумматора младшего разряда подключен ко

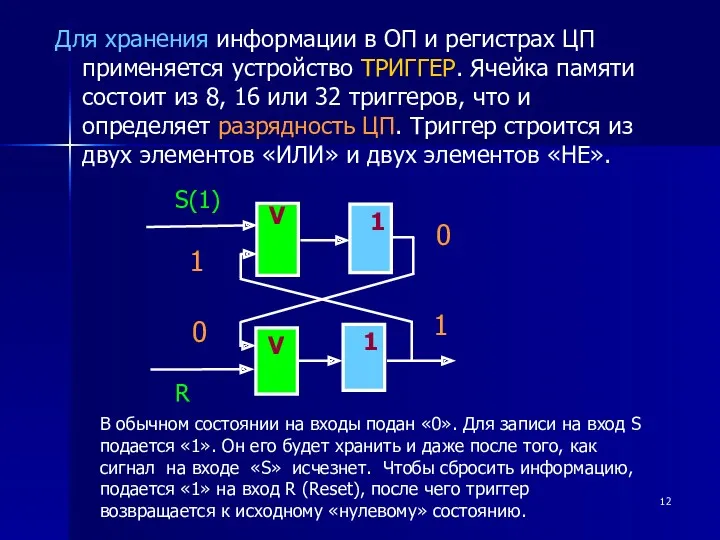

- 12. Для хранения информации в ОП и регистрах ЦП применяется устройство ТРИГГЕР. Ячейка памяти состоит из 8,

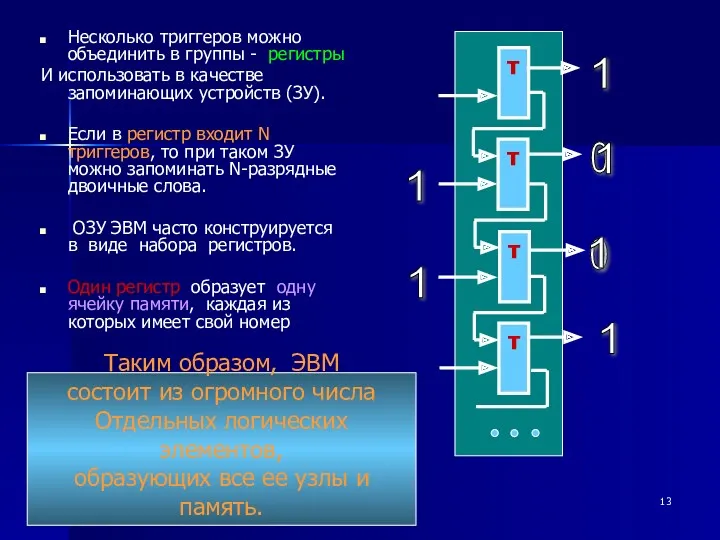

- 13. Несколько триггеров можно объединить в группы - регистры И использовать в качестве запоминающих устройств (ЗУ). Если

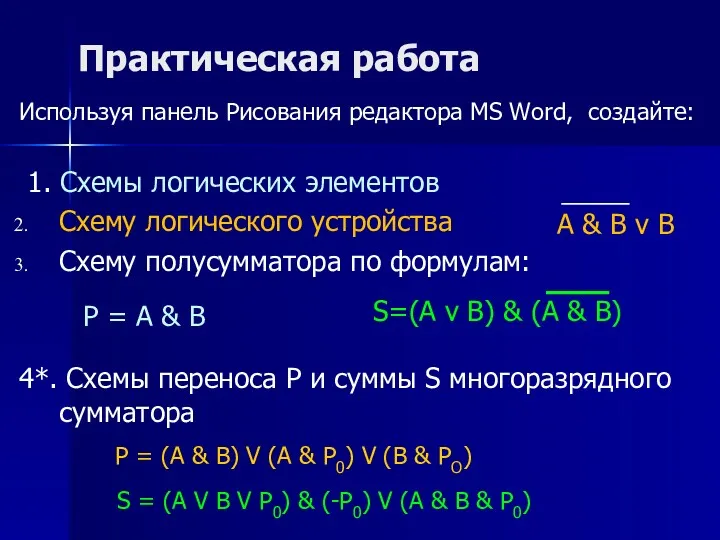

- 14. Практическая работа Используя панель Рисования редактора MS Word, создайте: 1. Схемы логических элементов Схему логического устройства

- 16. Скачать презентацию

Формирование социокультурных навыков школьников на уроках иностранного языка

Формирование социокультурных навыков школьников на уроках иностранного языка Напряженность электростатического поля

Напряженность электростатического поля Особенности туризма как объекта управления

Особенности туризма как объекта управления НАШ ДРУГ – Санкт- Петербург

НАШ ДРУГ – Санкт- Петербург Односоставное предложение

Односоставное предложение Скульптура – гімн людині

Скульптура – гімн людині Подарки своими руками

Подарки своими руками Археология палеолита. Псевдоартефакты, эолиты, артефакты

Археология палеолита. Псевдоартефакты, эолиты, артефакты акция засветись

акция засветись 1 класс Оригами. Котик, собака, домик

1 класс Оригами. Котик, собака, домик Базовые элементы настольного тенниса. Виды упражнений и способы обучения в группах начальной подготовки 1 года обучения.

Базовые элементы настольного тенниса. Виды упражнений и способы обучения в группах начальной подготовки 1 года обучения. презентация Цветы для мамы Диск

презентация Цветы для мамы Диск Основные устройства компьютера

Основные устройства компьютера Вагоны. Грузовые вагоны

Вагоны. Грузовые вагоны ВКР: Ремонт тормозной системы автомобиля Chevrolet Niva

ВКР: Ремонт тормозной системы автомобиля Chevrolet Niva Презентация к уроку химии по теме: Алюминий

Презентация к уроку химии по теме: Алюминий Сметно-нормативная (информационная) база ценообразования в строительстве

Сметно-нормативная (информационная) база ценообразования в строительстве 27 Spring - data

27 Spring - data Есенин Сергей Александрович (1895-1925) великий русский поэт

Есенин Сергей Александрович (1895-1925) великий русский поэт презентация по химии

презентация по химии Hseimun diplomacy club

Hseimun diplomacy club Вес тела, движущегося с ускорением

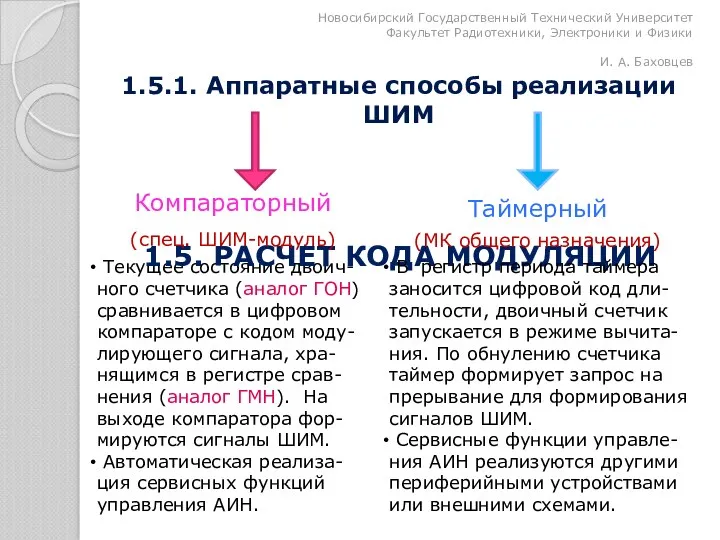

Вес тела, движущегося с ускорением Аппаратные способы реализации ШИМ

Аппаратные способы реализации ШИМ Презентация Правильные и полуправильные многогранники к внеклассному занятию по геометрии в старших классах

Презентация Правильные и полуправильные многогранники к внеклассному занятию по геометрии в старших классах Правоспособность и дееспособность гражданина

Правоспособность и дееспособность гражданина Программа деятельности Муниципального координационного центра Одаренные дети

Программа деятельности Муниципального координационного центра Одаренные дети 20230907_master-_klass

20230907_master-_klass Они подарили нам жизнь

Они подарили нам жизнь