Маршрут изготовления КМОП (комплементарная структура металл-оксид-полупроводник) по техпроцессу 90nm. (Лекция 10) презентация

Содержание

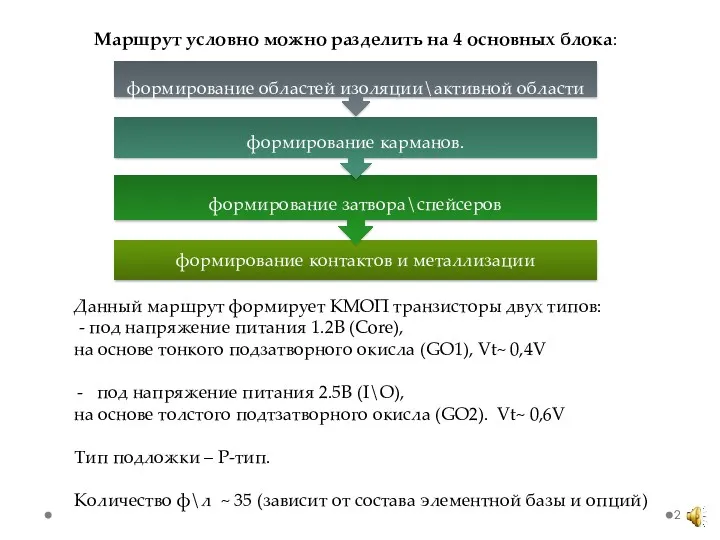

- 2. Маршрут условно можно разделить на 4 основных блока: Данный маршрут формирует КМОП транзисторы двух типов: -

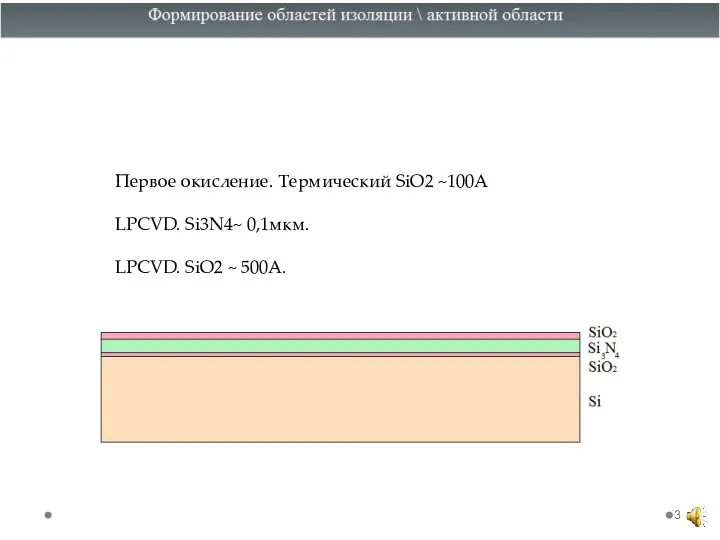

- 3. Первое окисление. Термический SiO2 ~100А LPCVD. Si3N4~ 0,1мкм. LPCVD. SiO2 ~ 500A.

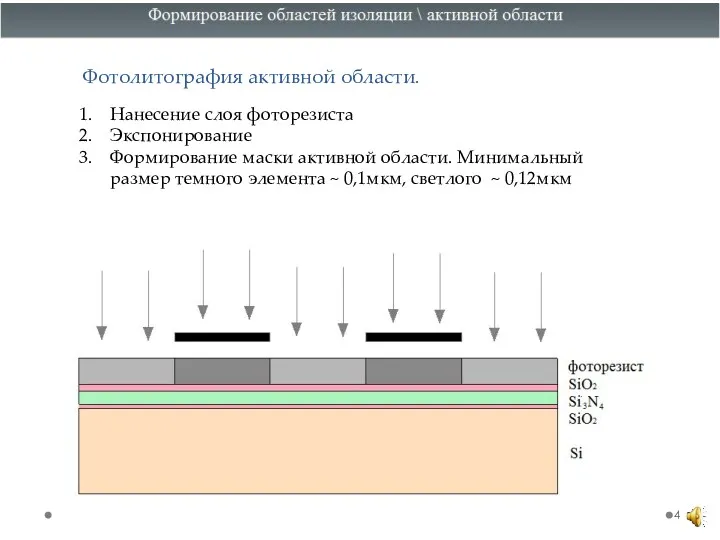

- 4. Фотолитография активной области. Нанесение слоя фоторезиста Экспонирование Формирование маски активной области. Минимальный размер темного элемента ~

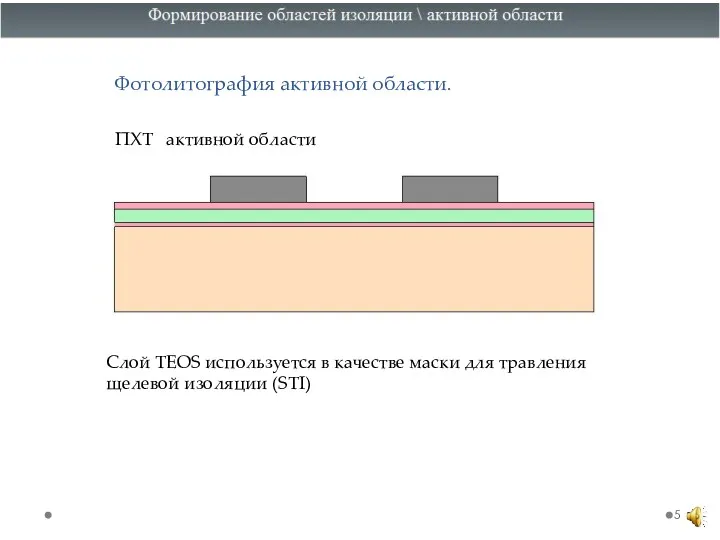

- 5. Фотолитография активной области. ПХТ активной области Слой TEOS используется в качестве маски для травления щелевой изоляции

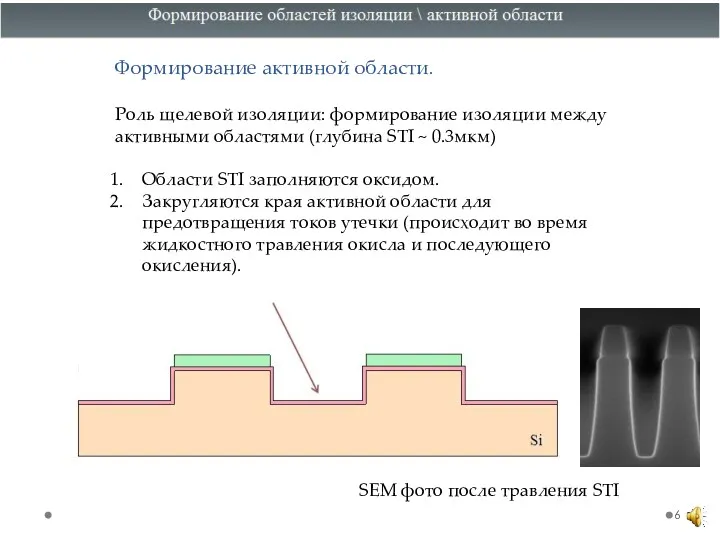

- 6. Формирование активной области. Роль щелевой изоляции: формирование изоляции между активными областями (глубина STI ~ 0.3мкм) Области

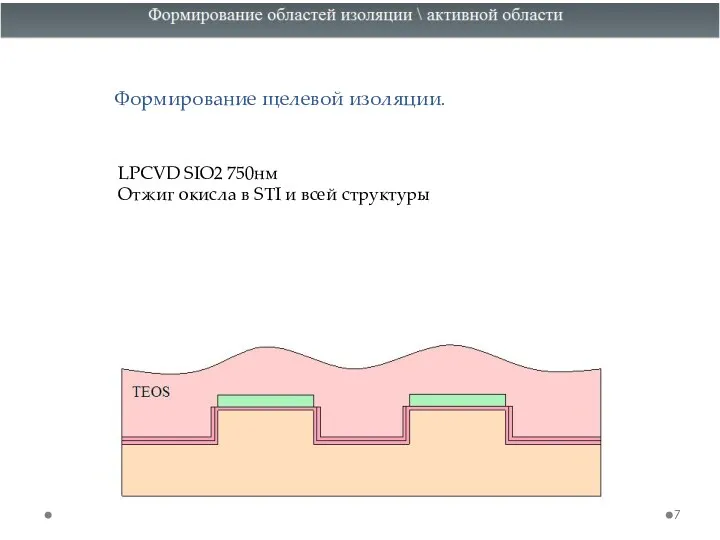

- 7. Формирование щелевой изоляции. LPCVD SIO2 750нм Отжиг окисла в STI и всей структуры

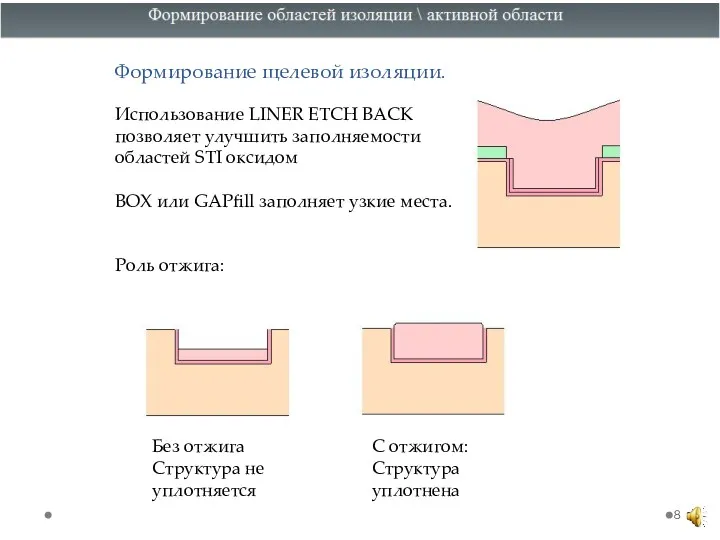

- 8. Формирование щелевой изоляции. Использование LINER ETCH BACK позволяет улучшить заполняемости областей STI оксидом BOX или GAPfill

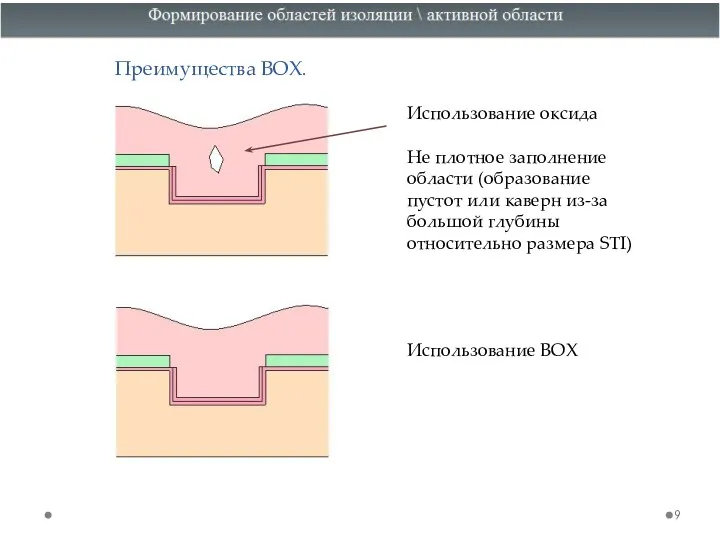

- 9. Преимущества BOX. Использование оксида Не плотное заполнение области (образование пустот или каверн из-за большой глубины относительно

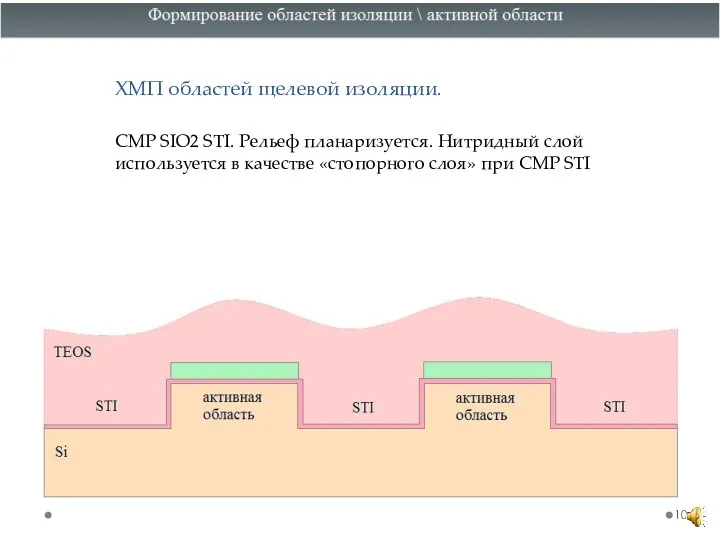

- 10. ХМП областей щелевой изоляции. CMP SIO2 STI. Рельеф планаризуется. Нитридный слой используется в качестве «стопорного слоя»

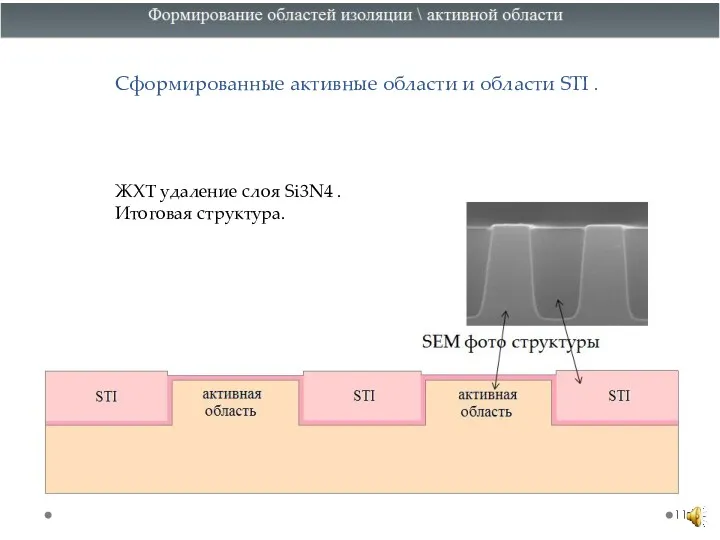

- 11. Сформированные активные области и области STI . ЖХТ удаление слоя Si3N4 . Итоговая структура.

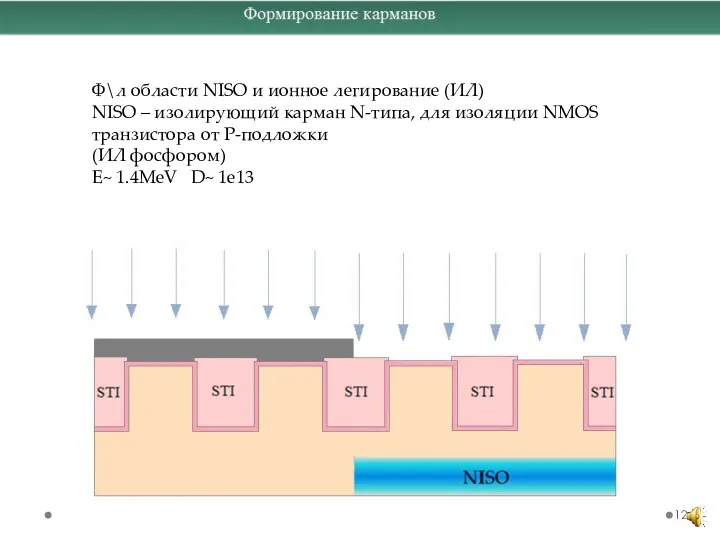

- 12. Ф\л области NISO и ионное легирование (ИЛ) NISO – изолирующий карман N-типа, для изоляции NMOS транзистора

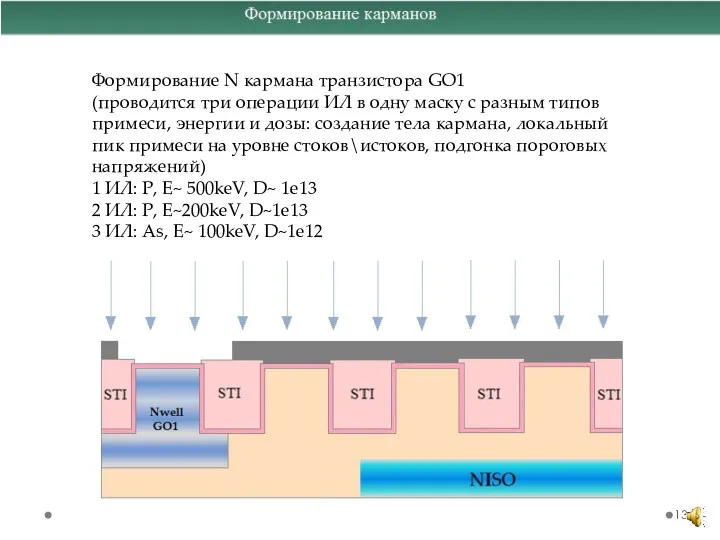

- 13. Формирование N кармана транзистора GO1 (проводится три операции ИЛ в одну маску с разным типов примеси,

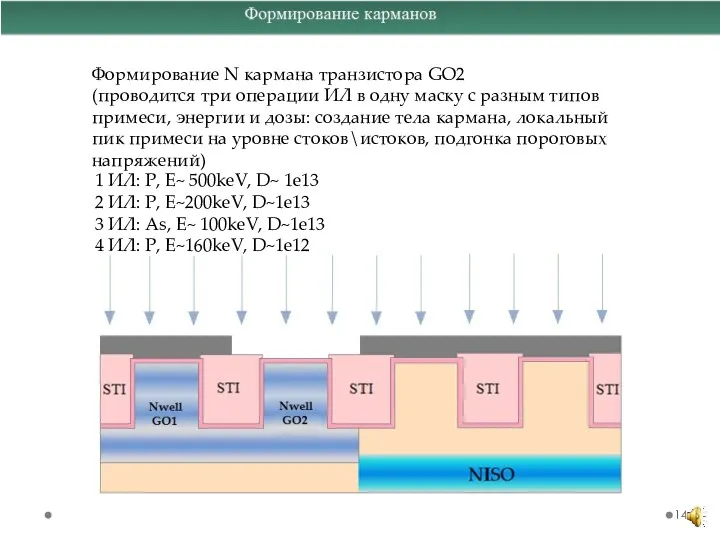

- 14. Формирование N кармана транзистора GO2 (проводится три операции ИЛ в одну маску с разным типов примеси,

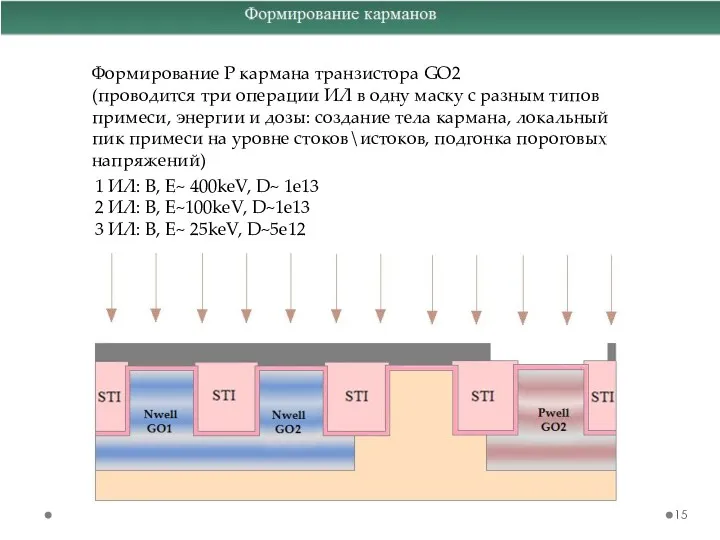

- 15. Формирование P кармана транзистора GO2 (проводится три операции ИЛ в одну маску с разным типов примеси,

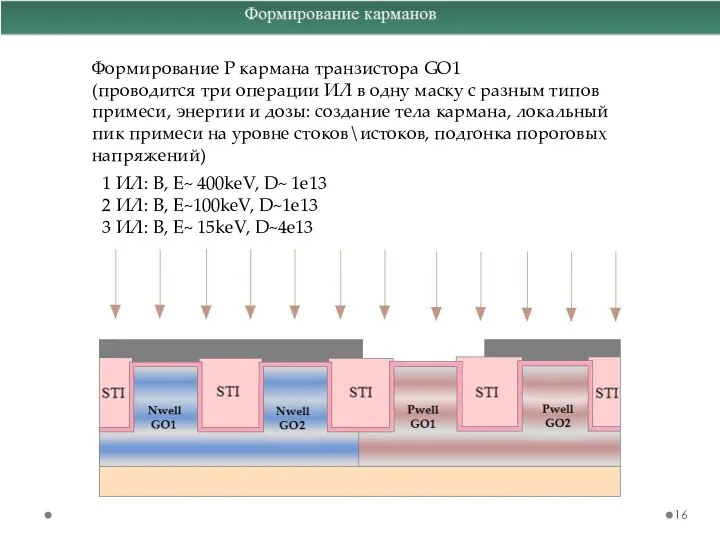

- 16. Формирование P кармана транзистора GO1 (проводится три операции ИЛ в одну маску с разным типов примеси,

- 17. Активация примеси и отжиг дефектов структуры RTP ~ 1000C

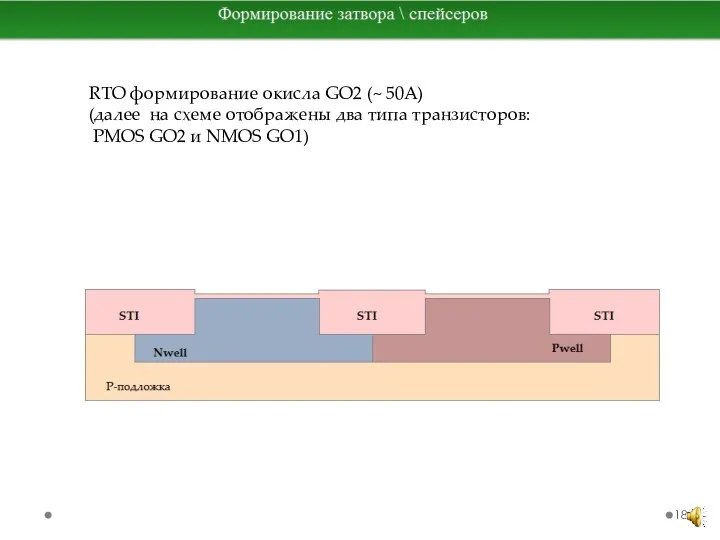

- 18. RTO формирование окисла GO2 (~ 50A) (далее на схеме отображены два типа транзисторов: PMOS GO2 и

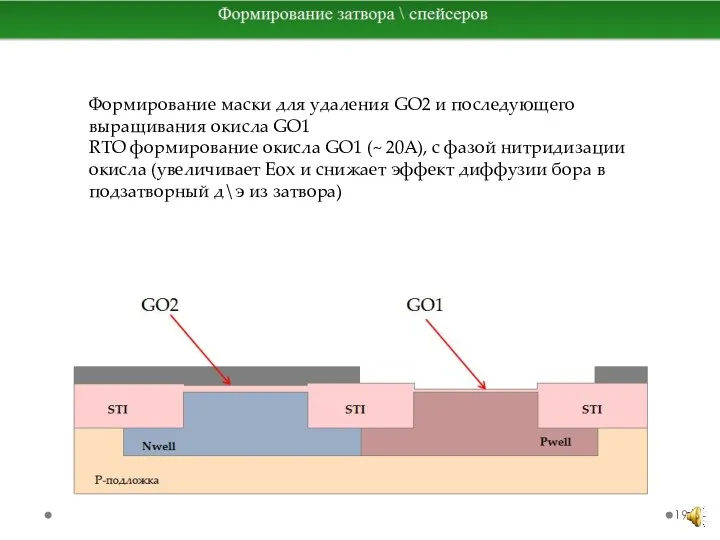

- 19. Формирование маски для удаления GO2 и последующего выращивания окисла GO1 RTO формирование окисла GO1 (~ 20A),

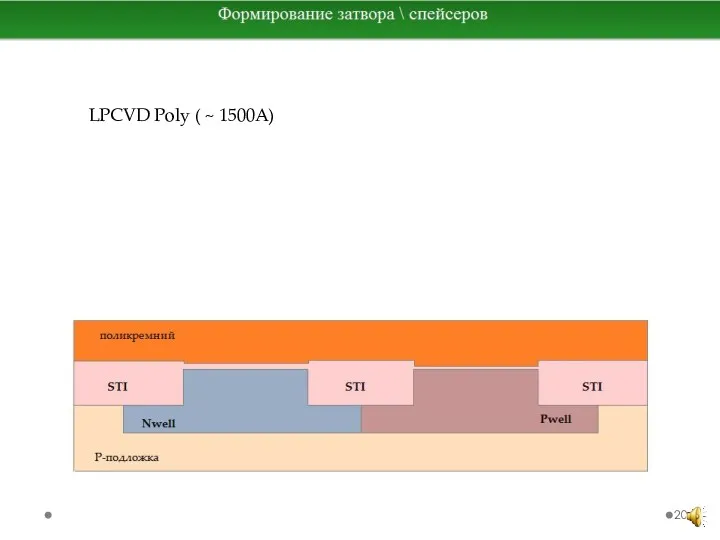

- 20. LPCVD Poly ( ~ 1500A)

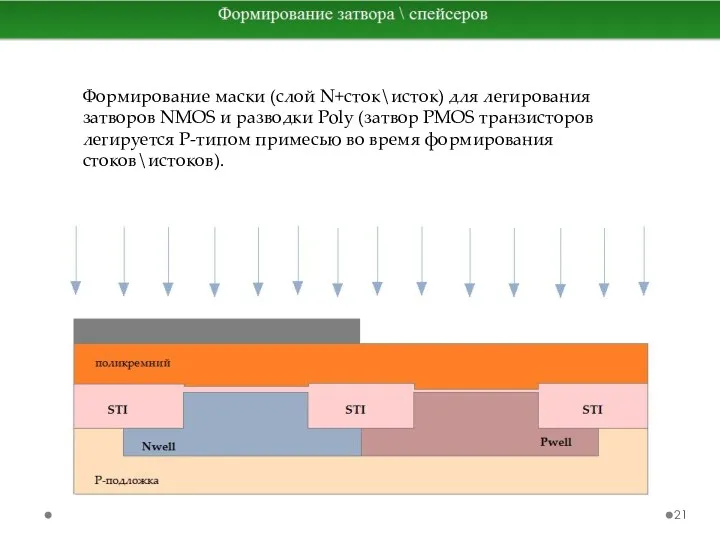

- 21. Формирование маски (слой N+сток\исток) для легирования затворов NMOS и разводки Poly (затвор PMOS транзисторов легируется Р-типом

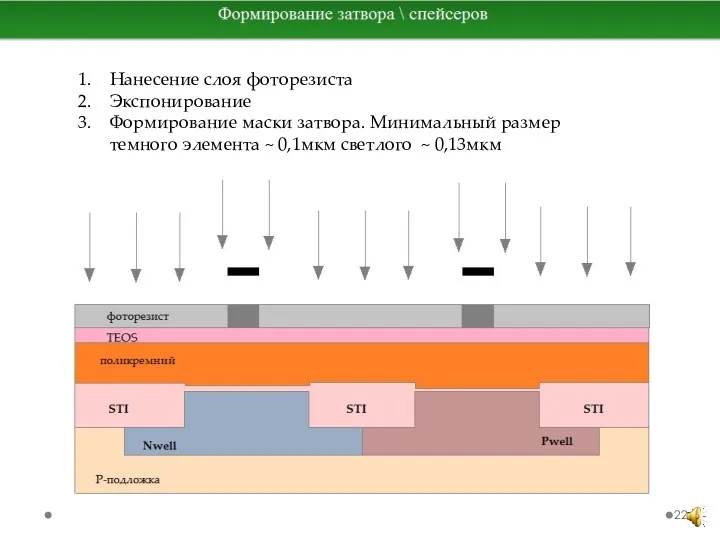

- 22. Нанесение слоя фоторезиста Экспонирование Формирование маски затвора. Минимальный размер темного элемента ~ 0,1мкм светлого ~ 0,13мкм

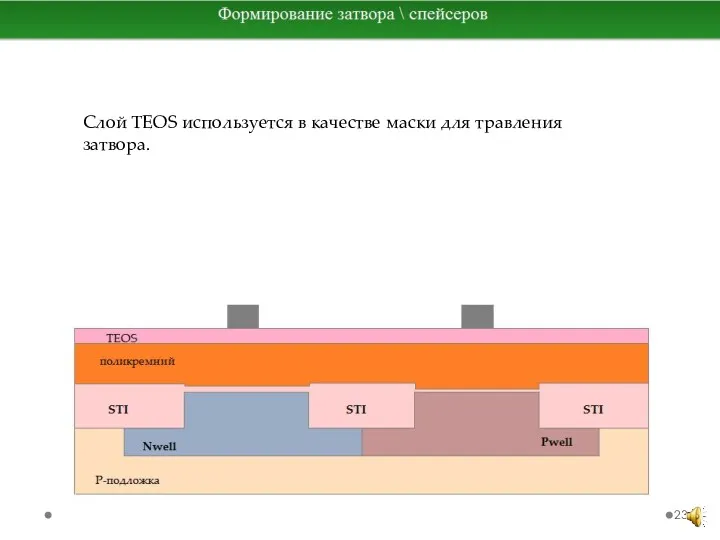

- 23. Слой TEOS используется в качестве маски для травления затвора.

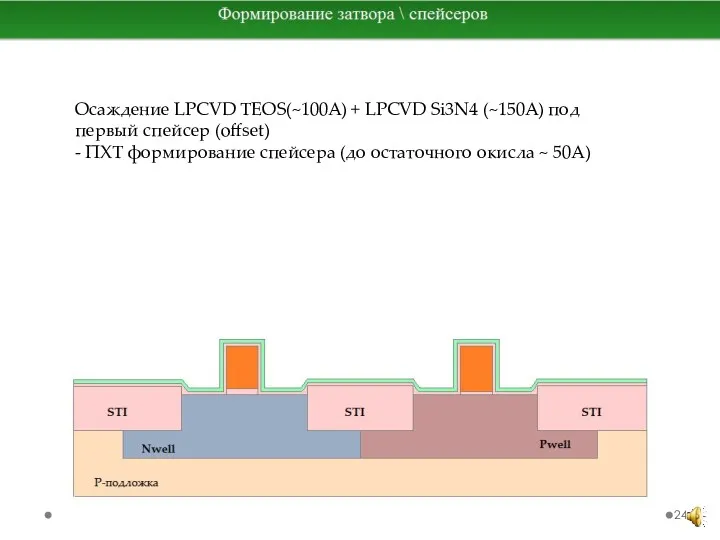

- 24. Осаждение LPCVD TEOS(~100A) + LPCVD Si3N4 (~150A) под первый спейсер (offset) - ПХТ формирование спейсера (до

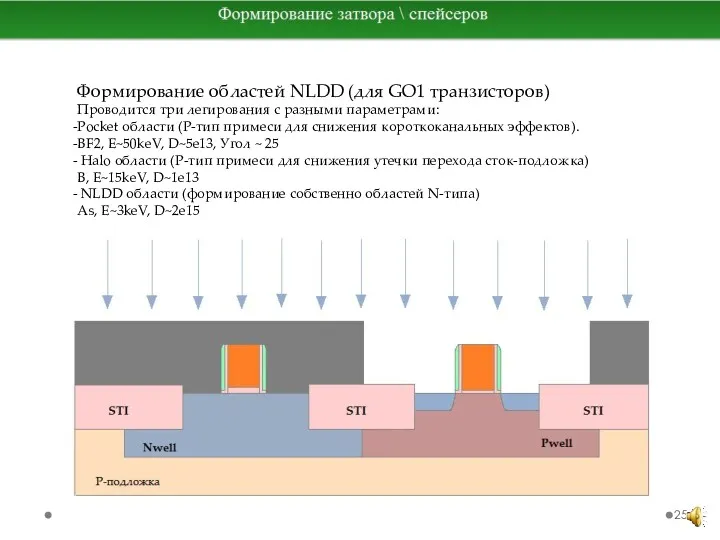

- 25. Формирование областей NLDD (для GO1 транзисторов) Проводится три легирования c разными параметрами: Pocket области (Р-тип примеси

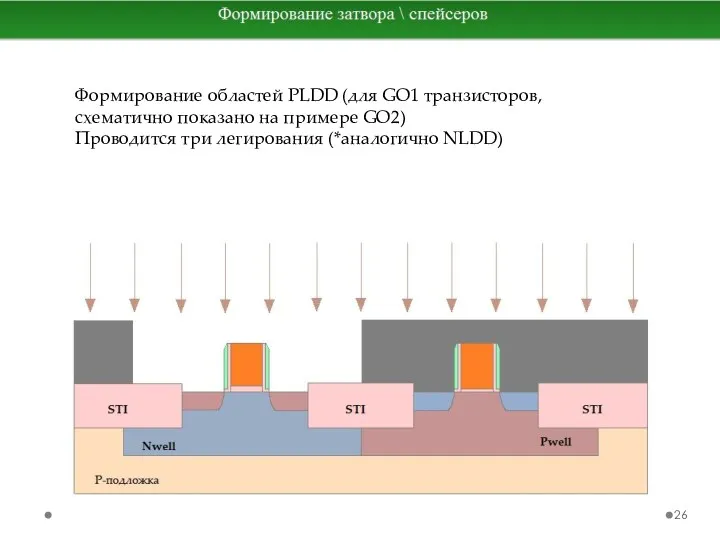

- 26. Формирование областей PLDD (для GO1 транзисторов, схематично показано на примере GO2) Проводится три легирования (*аналогично NLDD)

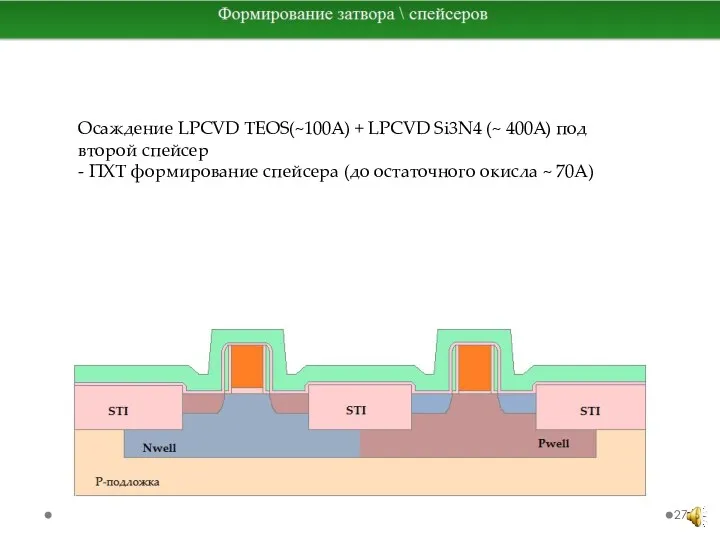

- 27. Осаждение LPCVD TEOS(~100A) + LPCVD Si3N4 (~ 400A) под второй спейсер - ПХТ формирование спейсера (до

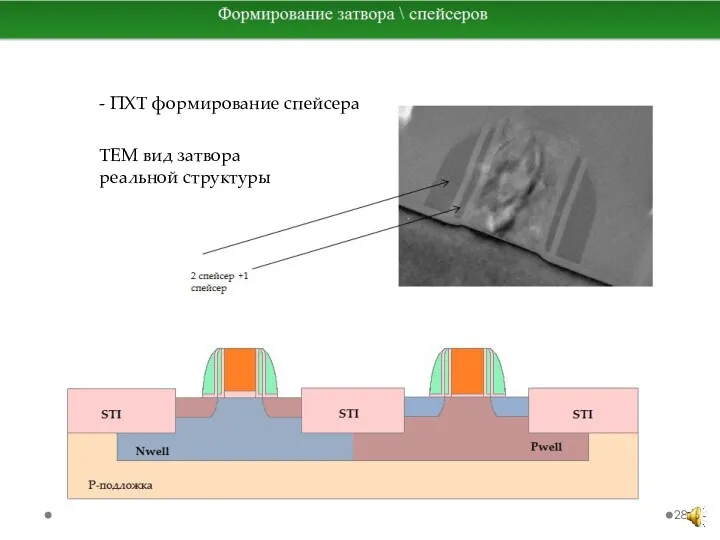

- 28. TEM вид затвора реальной структуры - ПХТ формирование спейсера

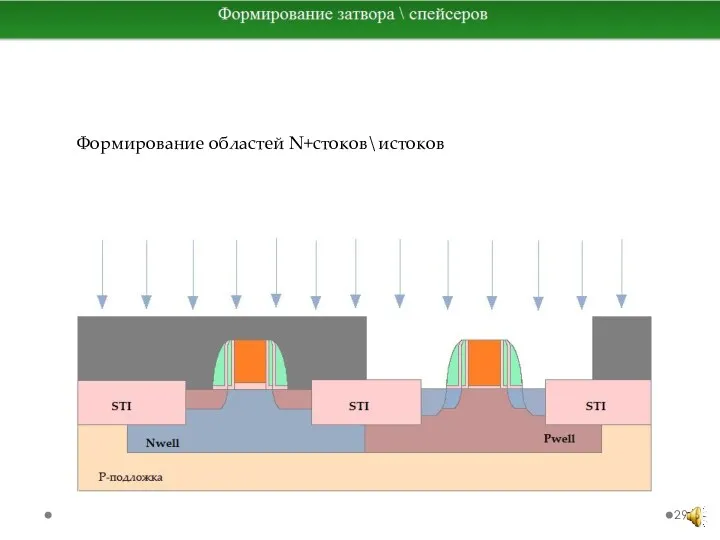

- 29. Формирование областей N+стоков\истоков

- 31. Скачать презентацию

С днем мамы

С днем мамы Семья пастора

Семья пастора Комплексные числа

Комплексные числа ФГОС в дошкольном образовании

ФГОС в дошкольном образовании Пластиковые окна или старые деревянные

Пластиковые окна или старые деревянные Битва под Сталинградом

Битва под Сталинградом Устный журнал Путешествие по планете Памяти

Устный журнал Путешествие по планете Памяти Бойове застосування КЗА 86Ж6. Алгоритми обробки радiолокацiйної iнформацiї, виявлення та захоплення цiлей. (Тема 8.3)

Бойове застосування КЗА 86Ж6. Алгоритми обробки радiолокацiйної iнформацiї, виявлення та захоплення цiлей. (Тема 8.3) Саванны. Субэкваториальный климатический пояс

Саванны. Субэкваториальный климатический пояс Воспитательная система класса

Воспитательная система класса Презентация Семья и школа в формировании личности ребенка

Презентация Семья и школа в формировании личности ребенка Clothes and Fashion

Clothes and Fashion Ограничение облучения от природных источников

Ограничение облучения от природных источников Презентация к викторине У сказки тихий голосок.

Презентация к викторине У сказки тихий голосок. Сюжетно-ролевая игра

Сюжетно-ролевая игра Мастер моего села

Мастер моего села Блиц-опрос Я знаю лес

Блиц-опрос Я знаю лес Концепция педагогической деятельности

Концепция педагогической деятельности System administracji publicznej w Hondurasie

System administracji publicznej w Hondurasie GP USB DownLoad Manual (English_Version)

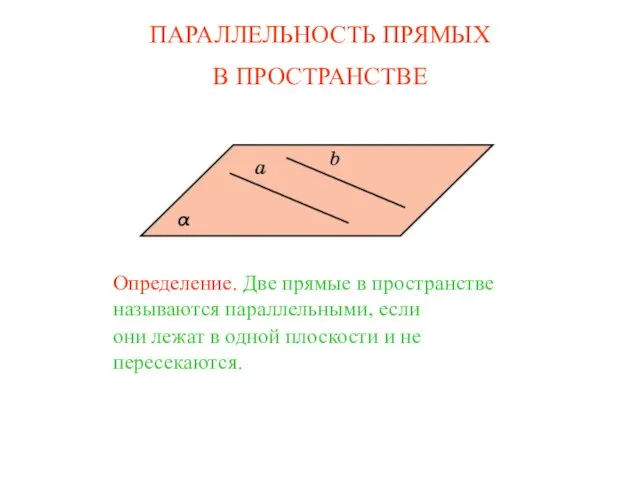

GP USB DownLoad Manual (English_Version) Параллельность прямых в пространстве

Параллельность прямых в пространстве Хранение дел организации. (Тема 4)

Хранение дел организации. (Тема 4) Формирование комфортной городской среды

Формирование комфортной городской среды PML30_SummerPractice2022_Presentation_Pattern

PML30_SummerPractice2022_Presentation_Pattern Декоративный пейзаж

Декоративный пейзаж Пищевая сода. Необычное в обычном

Пищевая сода. Необычное в обычном Как научить своего ребёнка жить в мире людей. Уроки этики поведения для детей и родителей

Как научить своего ребёнка жить в мире людей. Уроки этики поведения для детей и родителей Выдающиеся открытия в области химии

Выдающиеся открытия в области химии