Содержание

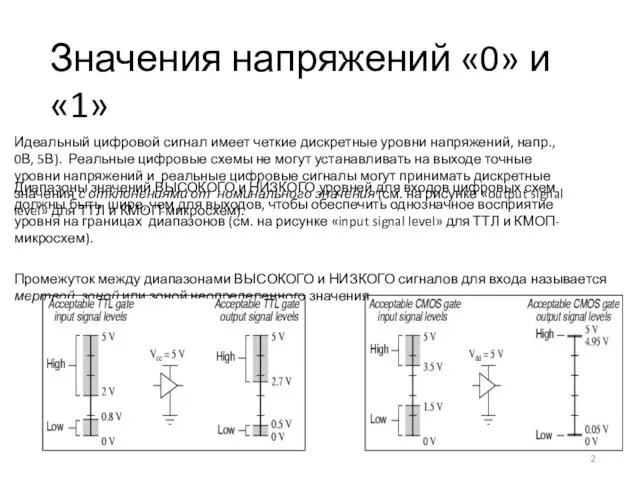

- 2. Значения напряжений «0» и «1» Идеальный цифровой сигнал имеет четкие дискретные уровни напряжений, напр., 0В, 5В).

- 3. Что дает кодирование уровней диапазонами напряжений Позволяет использовать цифровые элементы/схемы с достаточно значительными допусками параметров входных

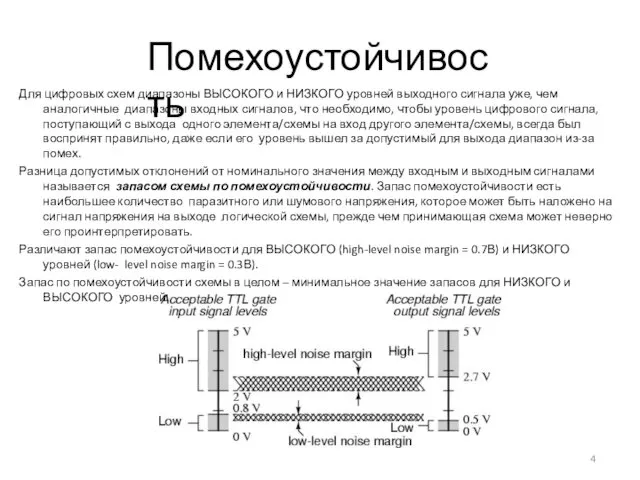

- 4. Помехоустойчивость Для цифровых схем диапазоны ВЫСОКОГО и НИЗКОГО уровней выходного сигнала уже, чем аналогичные диапазоны входных

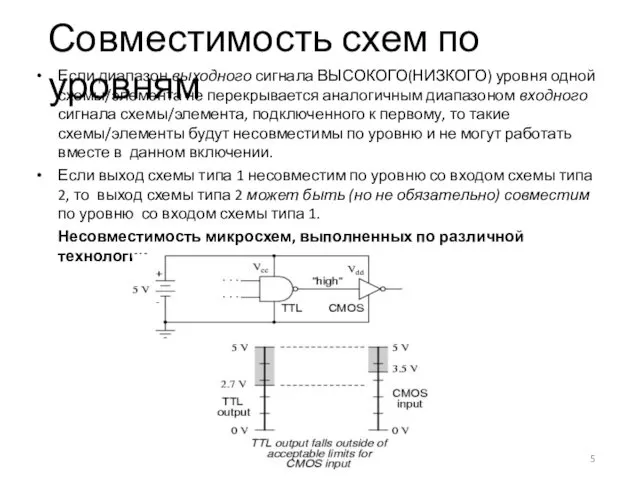

- 5. Совместимость схем по уровням Если диапазон выходного сигнала ВЫСОКОГО(НИЗКОГО) уровня одной схемы/элемента не перекрывается аналогичным диапазоном

- 6. Несовместимость схем с различным напряжением питания Возникает из-за смещения и/или изменения ширины диапазонов ВЫСОКОГО и НИЗКОГО

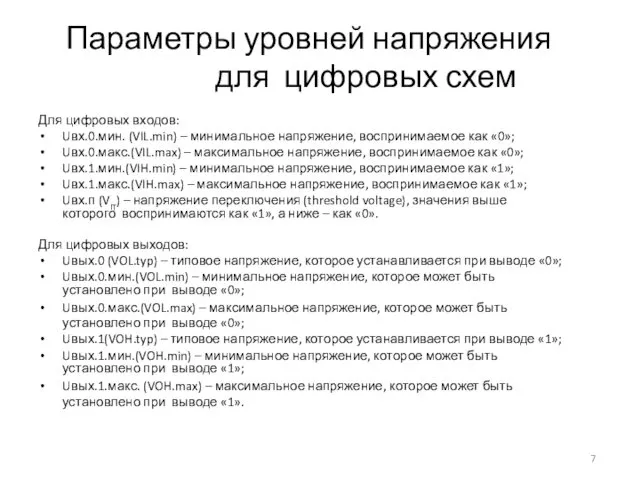

- 7. Параметры уровней напряжения для цифровых схем Для цифровых входов: Uвх.0.мин. (VIL.min) – минимальное напряжение, воспринимаемое как

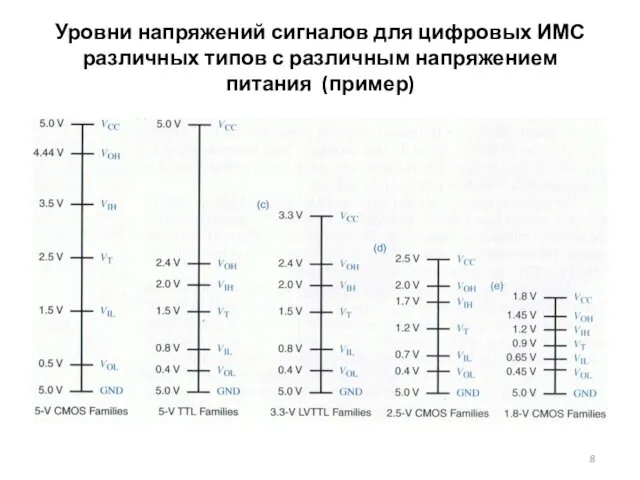

- 8. Уровни напряжений сигналов для цифровых ИМС различных типов с различным напряжением питания (пример)

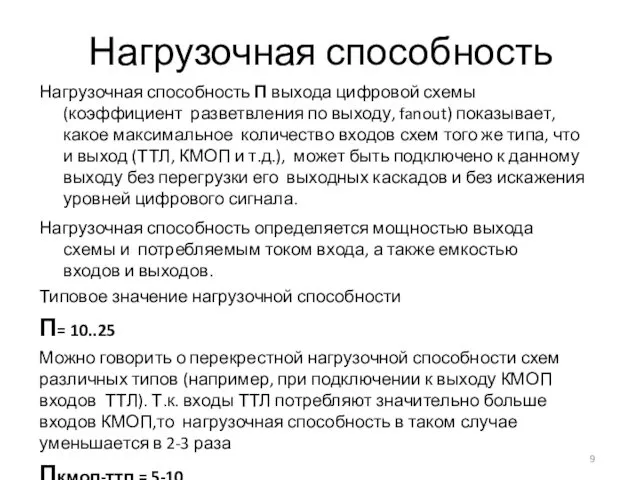

- 9. Нагрузочная способность Нагрузочная способность П выхода цифровой схемы (коэффициент разветвления по выходу, fanout) показывает, какое максимальное

- 10. Последствия перегрузки выходов Выходное напряжение НИЗКОГО уровня может превысить Uвх.0.макс. и НИЗКИЙ уровень будет определен как

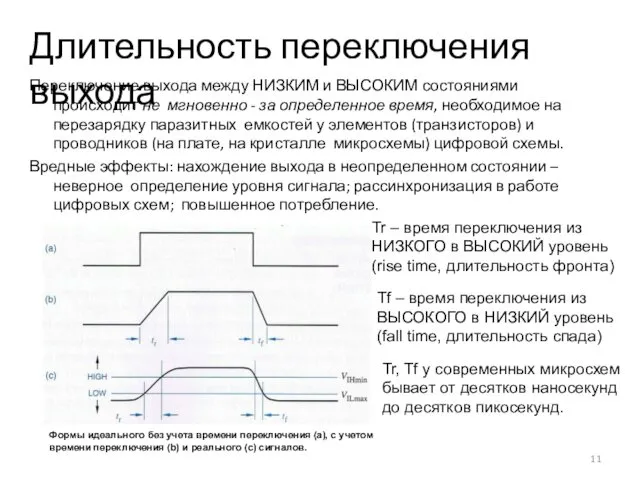

- 11. Длительность переключения выхода Переключение выхода между НИЗКИМ и ВЫСОКИМ состояниями происходит не мгновенно - за определенное

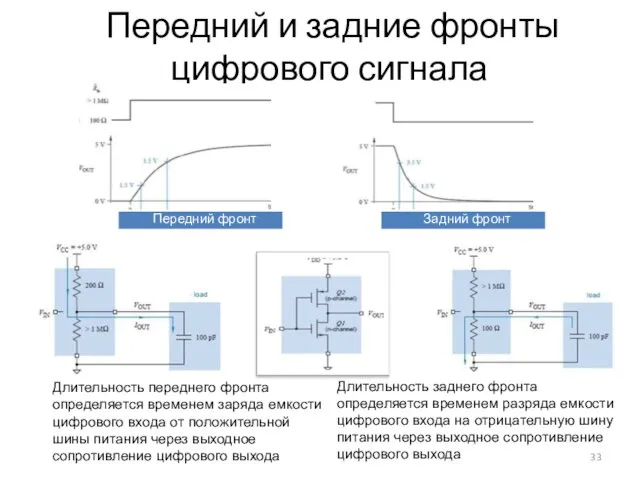

- 12. Передний и задние фронты цифрового сигнала Передний фронт Задний фронт Длительность переднего фронта определяется временем заряда

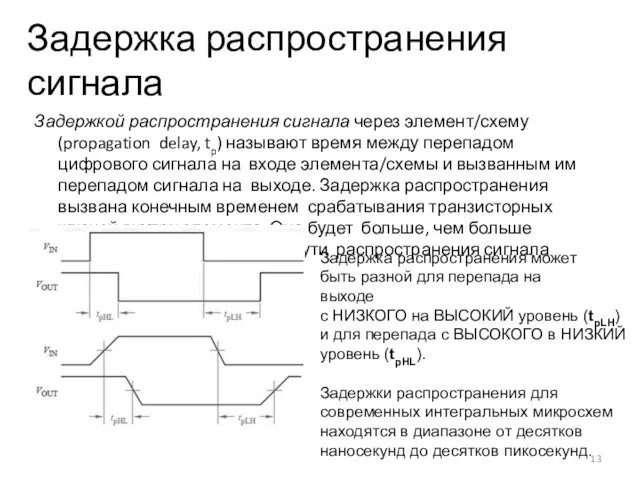

- 13. Задержка распространения сигнала Задержкой распространения сигнала через элемент/схему (propagation delay, tp) называют время между перепадом цифрового

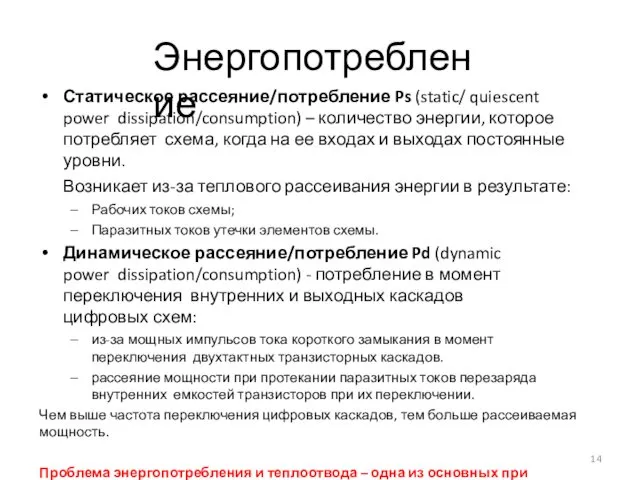

- 14. Энергопотребление Статическое рассеяние/потребление Ps (static/ quiescent power dissipation/consumption) – количество энергии, которое потребляет схема, когда на

- 15. ПОРТЫ ВВОДА И ВЫВОДА ЦИФРОВЫХ СХЕМ Порт – точка подключения к системе. Цифровой порт ввода и(или)

- 16. Порты вывода (выходы) цифровых схем Двухтактный на комплементарных транзисторах (с активной нагрузкой) Однотактный с пассивной нагрузкой

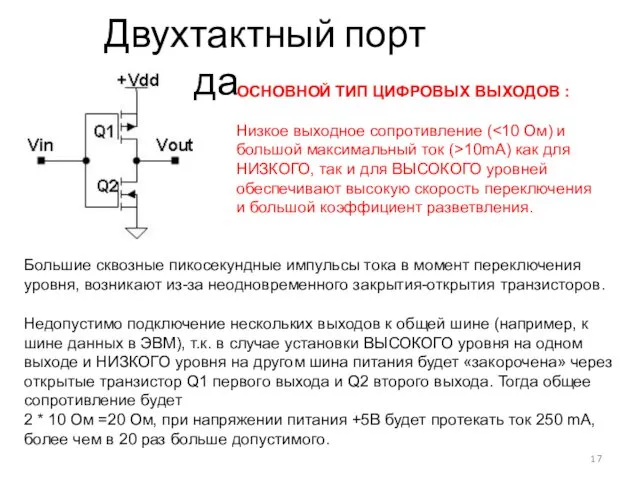

- 17. Двухтактный порт вывода ОСНОВНОЙ ТИП ЦИФРОВЫХ ВЫХОДОВ : Низкое выходное сопротивление ( 10mA) как для НИЗКОГО,

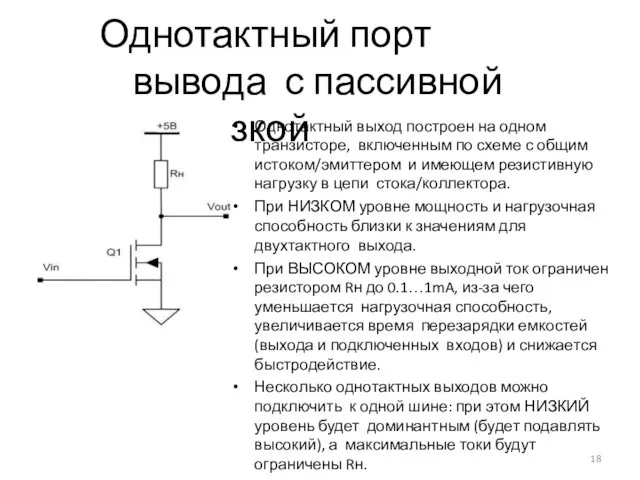

- 18. Однотактный порт вывода с пассивной нагрузкой Однотактный выход построен на одном транзисторе, включенным по схеме с

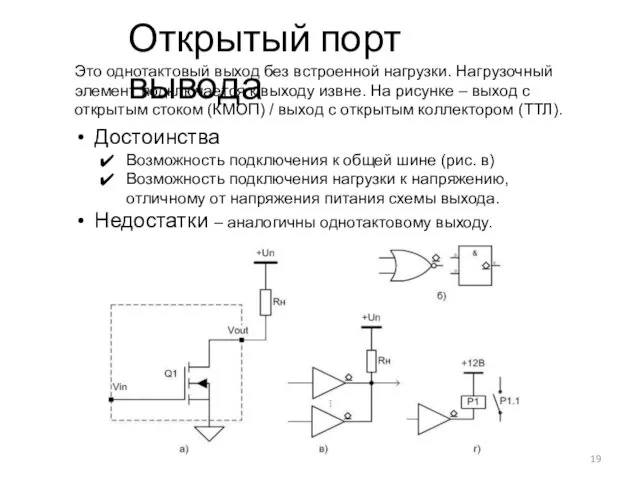

- 19. Открытый порт вывода Это однотактовый выход без встроенной нагрузки. Нагрузочный элемент подключается к выходу извне. На

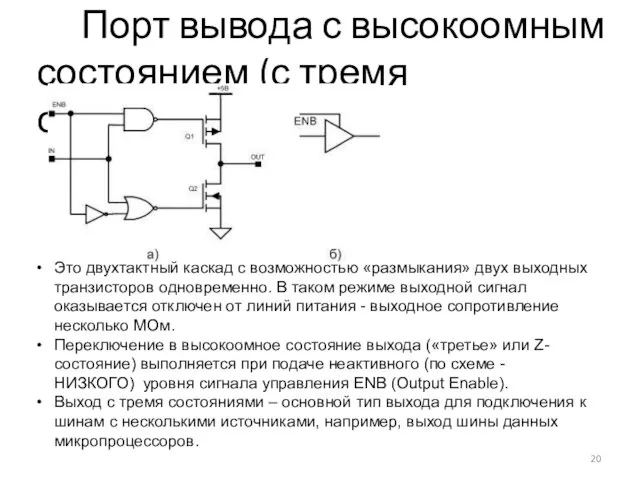

- 20. Порт вывода с высокоомным состоянием (с тремя состояниями) Это двухтактный каскад с возможностью «размыкания» двух выходных

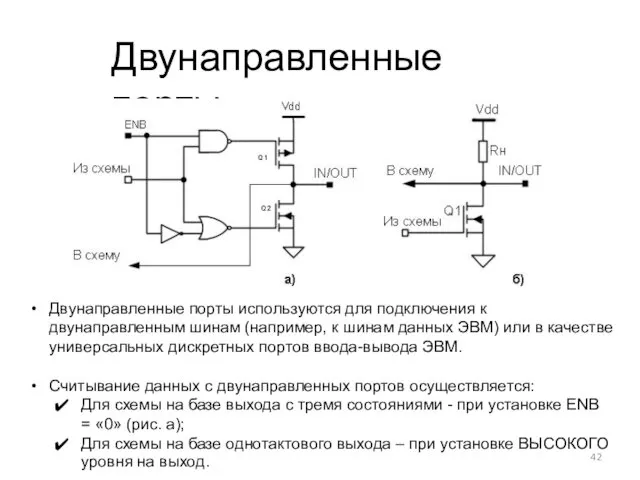

- 21. Двунаправленные порты Двунаправленные порты используются для подключения к двунаправленным шинам (например, к шинам данных ЭВМ) или

- 22. Порт ввода с триггером Шмитта Триггер Шмитта – повторитель сигнала, с неодинаковыми (смещенными) диапазонами ВЫСОКОГО и

- 23. Подтягивающие и понижающие резисторы Подтягивающий (pull up) - резистор между сигналом и линией питания +Uпит (Vss,

- 24. Подтягивающие и понижающие резисторы. Применение (2). а) Для установки уровня «по умолчанию» для цифровых сигналов: установка

- 25. Специальные варианты использования портов Монтажная (проводная) логика Организация шин: На базе открытых выходов; На базе выходов

- 26. Электропитание цифровых схем Условное обозначение: Vee или Vss – общая или нулевая шина питания: к ней

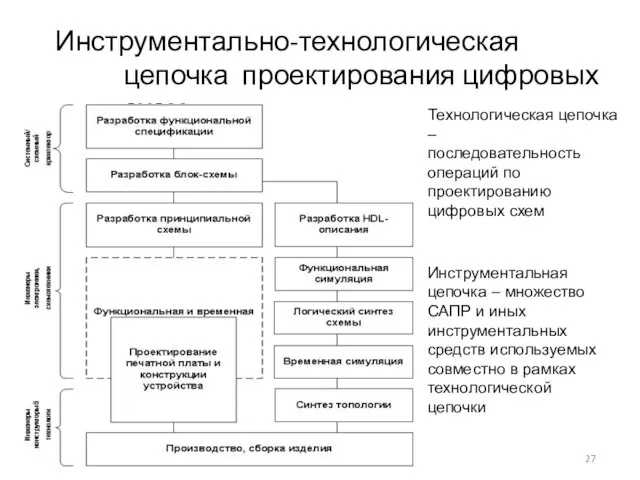

- 27. Инструментально-технологическая цепочка проектирования цифровых схем Технологическая цепочка – последовательность операций по проектированию цифровых схем Инструментальная цепочка

- 29. Скачать презентацию

Свет и цвет в фотографии

Свет и цвет в фотографии Вимірювання обертального моменту валу електродвигуна на основі тензорезистора

Вимірювання обертального моменту валу електродвигуна на основі тензорезистора Структуры осадочных пород

Структуры осадочных пород гр.Улыбка вторник 14.04

гр.Улыбка вторник 14.04 Презентация: Использование информационно-просветительских форм работы с родителями по правилам дорожного движения

Презентация: Использование информационно-просветительских форм работы с родителями по правилам дорожного движения Проект организации перевалки сельскохозяйственных грузов Генезис

Проект организации перевалки сельскохозяйственных грузов Генезис Презентация Тула - моя малая Родина

Презентация Тула - моя малая Родина Воспитательный потенциал современной семьи

Воспитательный потенциал современной семьи Подготовительный этап коррекционно-логопедической работы по преодолению нарушений произношения звуков Х и Х'

Подготовительный этап коррекционно-логопедической работы по преодолению нарушений произношения звуков Х и Х' Дети-герои Великой Отечественной войны

Дети-герои Великой Отечественной войны Клиническая трансфузиология

Клиническая трансфузиология Радиостанция комплекса Vertex VX-4200. (Тема 4.7)

Радиостанция комплекса Vertex VX-4200. (Тема 4.7) Презентация к уроку по теме Природные ресурсы Западной Сибири (8 класс)

Презентация к уроку по теме Природные ресурсы Западной Сибири (8 класс) A_B_klassy_01_03_2021

A_B_klassy_01_03_2021 Аппаратные и программные средства видеонаблюдения

Аппаратные и программные средства видеонаблюдения Растворы. Растворимость

Растворы. Растворимость Особенности функциональной специализации полушарий у детей с ОНР

Особенности функциональной специализации полушарий у детей с ОНР ПрезентацияСвященные сооружения

ПрезентацияСвященные сооружения Безусловная оптимизация методом классического математического анализа. Определение оптимального времени пребывания

Безусловная оптимизация методом классического математического анализа. Определение оптимального времени пребывания Ах, эти кошки… Викторина

Ах, эти кошки… Викторина МОЯ ВИЗИТНАЯ КАРТОЧКА

МОЯ ВИЗИТНАЯ КАРТОЧКА Мікропроцесорні системи

Мікропроцесорні системи презентация 70 лет Сталинградской битве

презентация 70 лет Сталинградской битве Презентация. История герба города Погара.

Презентация. История герба города Погара. Виртуальная экскурсия по городу Псков. Псковский Кром (Кремль)

Виртуальная экскурсия по городу Псков. Псковский Кром (Кремль) Пищеварение в ротовой полости

Пищеварение в ротовой полости Хамантова Г. Ю. МБУ ДО Полазненская ДШИ, Рециклинг

Хамантова Г. Ю. МБУ ДО Полазненская ДШИ, Рециклинг Макет рабочей программы воспитания при разработке и обновлении образовательных программ среднего профессионального образования

Макет рабочей программы воспитания при разработке и обновлении образовательных программ среднего профессионального образования