Содержание

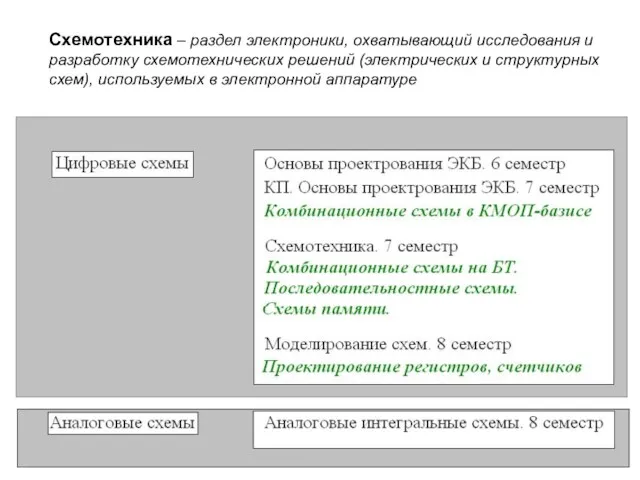

- 2. Схемотехника – раздел электроники, охватывающий исследования и разработку схемотехнических решений (электрических и структурных схем), используемых в

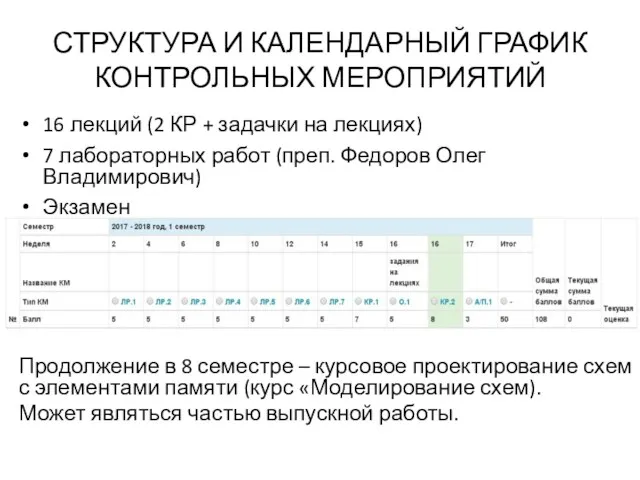

- 3. СТРУКТУРА И КАЛЕНДАРНЫЙ ГРАФИК КОНТРОЛЬНЫХ МЕРОПРИЯТИЙ 16 лекций (2 КР + задачки на лекциях) 7 лабораторных

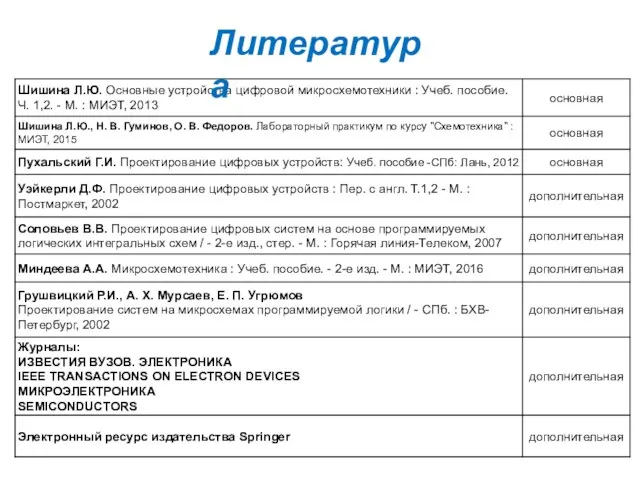

- 4. Литература

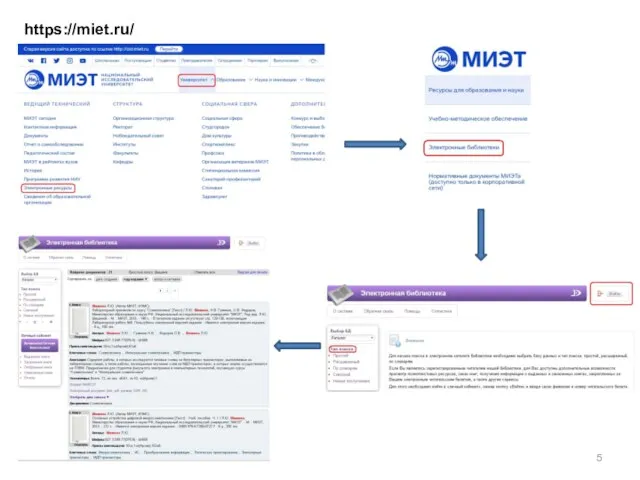

- 5. https://miet.ru/

- 6. Лекция 1 Введение в предмет курса МДП-инверторы с транзисторами одинакового типа проводимости КМДП- схемы

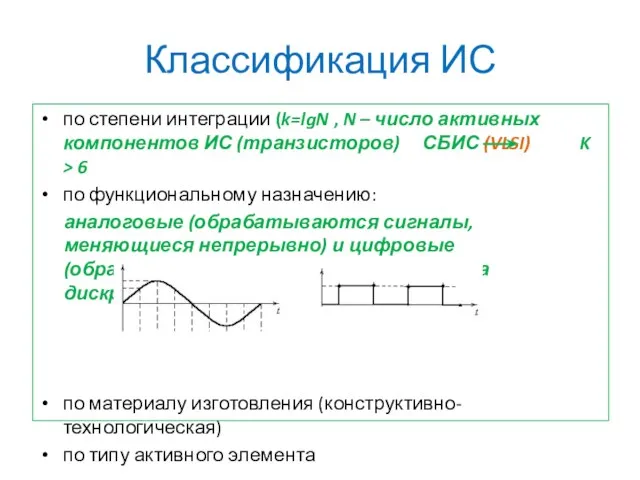

- 7. Классификация ИС по степени интеграции (k=lgN , N – число активных компонентов ИС (транзисторов) СБИС (VLSI)

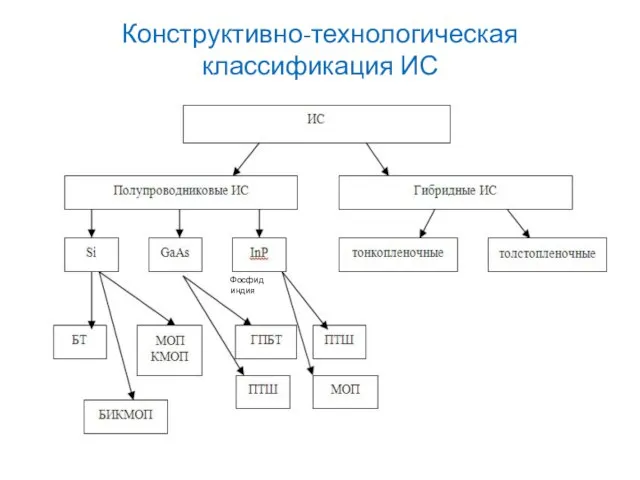

- 8. Конструктивно-технологическая классификация ИС Фосфид индия

- 9. Классификация ИС по типу активного элемента Микросхемы на униполярных (полевых) транзисторах — самые экономичные (по потреблению

- 10. Основные характеристики цифровых ИС выполняемая функция; вид элементной базы (технология основного ЛЭ); плотность упаковки (элементов/кристалл или

- 11. Основные элементы ИС: активные элементы биполярных ИС – транзисторы пассивные элементы – резисторы, конденсаторы и диоды

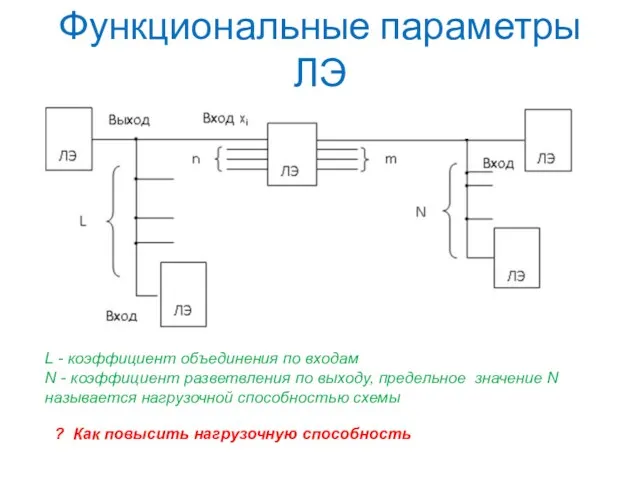

- 12. Функциональные параметры ЛЭ L - коэффициент объединения по входам N - коэффициент разветвления по выходу, предельное

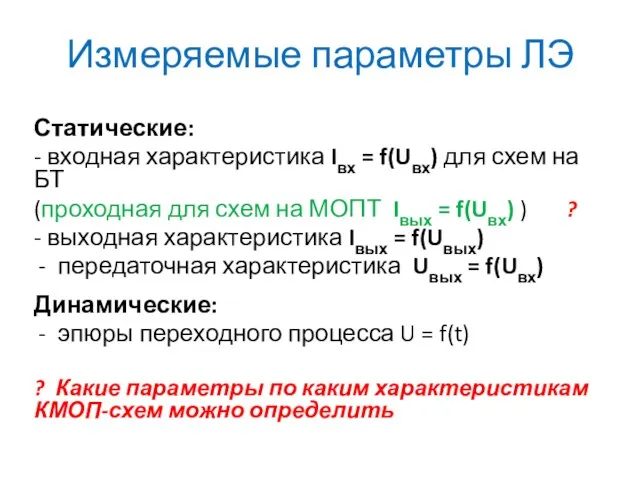

- 13. Измеряемые параметры ЛЭ Статические: - входная характеристика Iвх = f(Uвх) для схем на БТ (проходная для

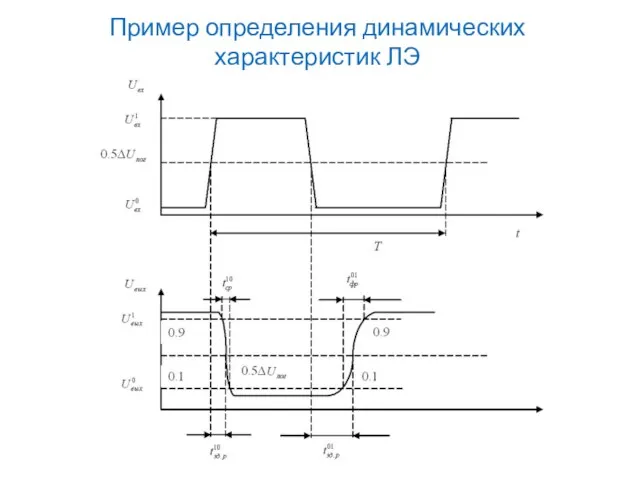

- 14. Пример определения динамических характеристик ЛЭ

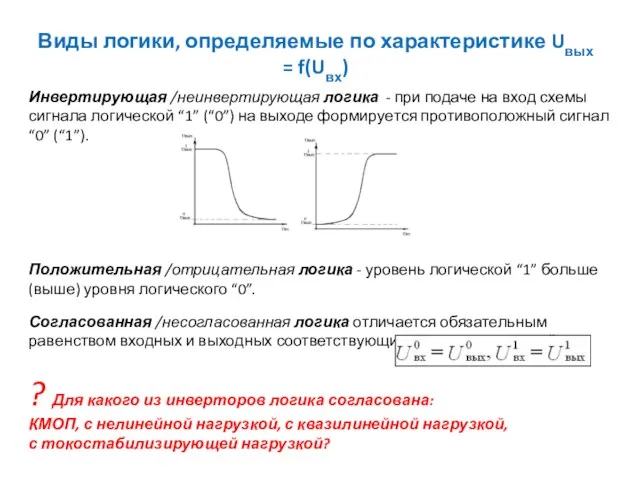

- 15. Виды логики, определяемые по характеристике Uвых = f(Uвх) Инвертирующая /неинвертирующая логика - при подаче на вход

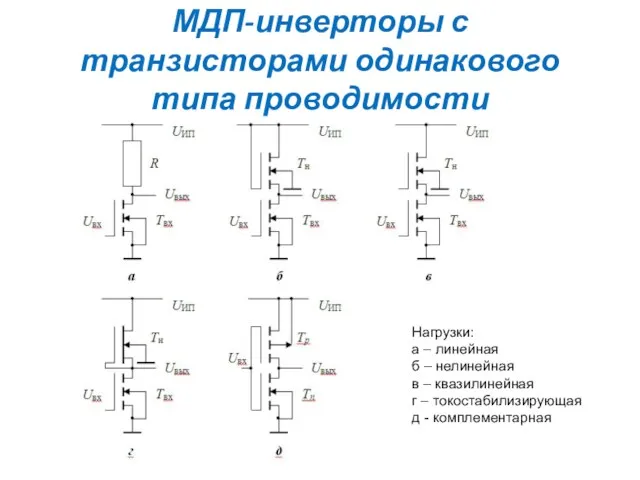

- 16. МДП-инверторы с транзисторами одинакового типа проводимости Нагрузки: а – линейная б – нелинейная в – квазилинейная

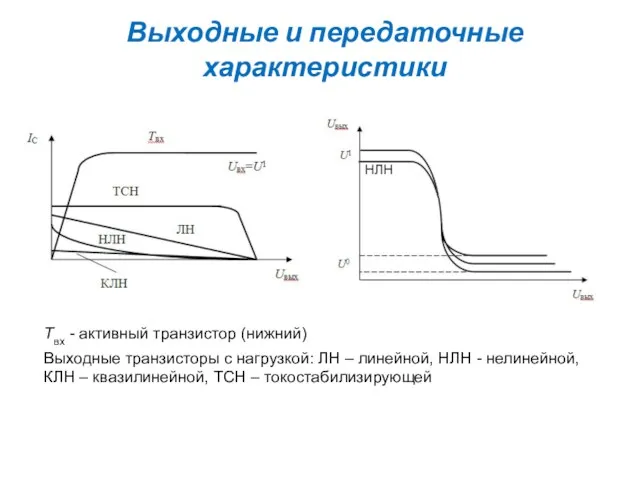

- 17. Выходные и передаточные характеристики Твх - активный транзистор (нижний) Выходные транзисторы с нагрузкой: ЛН – линейной,

- 18. КМДП- схемы КМДП- инверторы. Структура. Принцип работы, реализация логических функций. Передаточная характеристика в КМДП- схеме. Напряжение

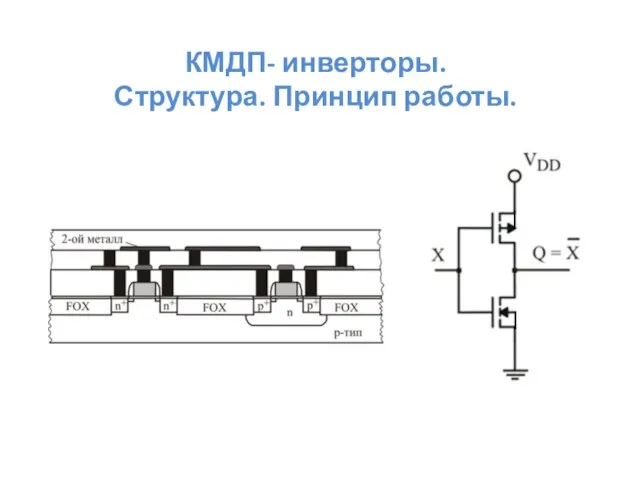

- 19. КМДП- инверторы. Структура. Принцип работы.

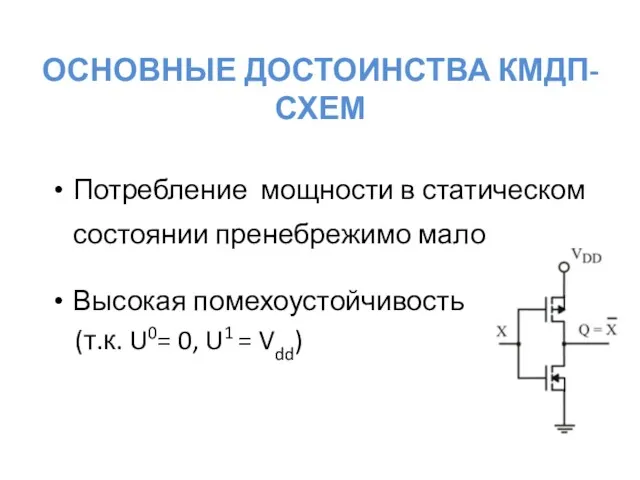

- 20. ОСНОВНЫЕ ДОСТОИНСТВА КМДП-СХЕМ Потребление мощности в статическом состоянии пренебрежимо мало Высокая помехоустойчивость (т.к. U0= 0, U1

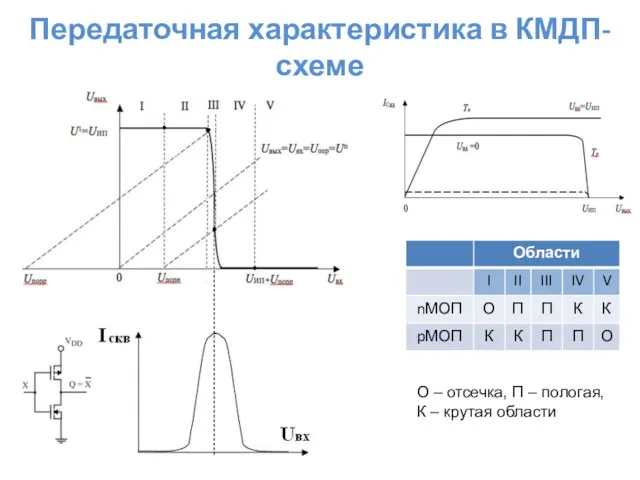

- 21. Передаточная характеристика в КМДП-схеме О – отсечка, П – пологая, К – крутая области

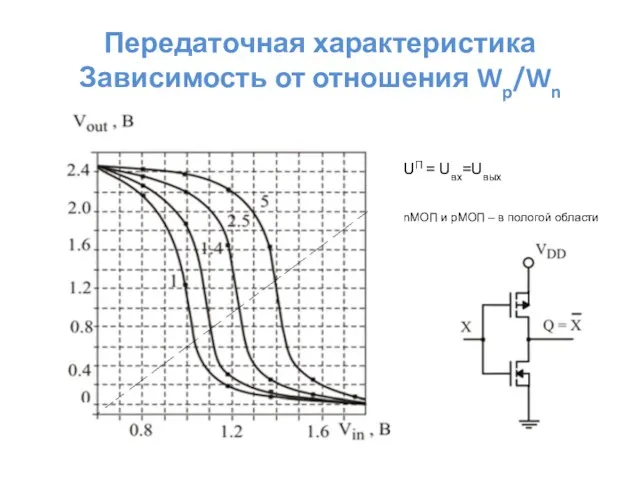

- 22. Передаточная характеристика Зависимость от отношения Wp/Wn UП = Uвх=Uвых nМОП и pМОП – в пологой области

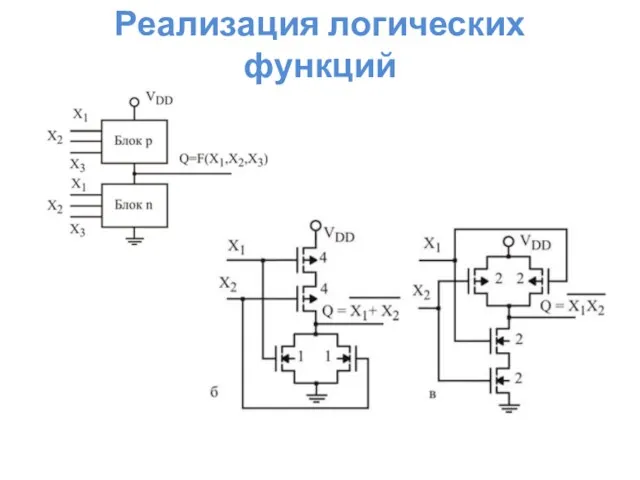

- 23. Реализация логических функций

- 24. Эффект защелки в КМДП- схемах (тиристорный эффект)

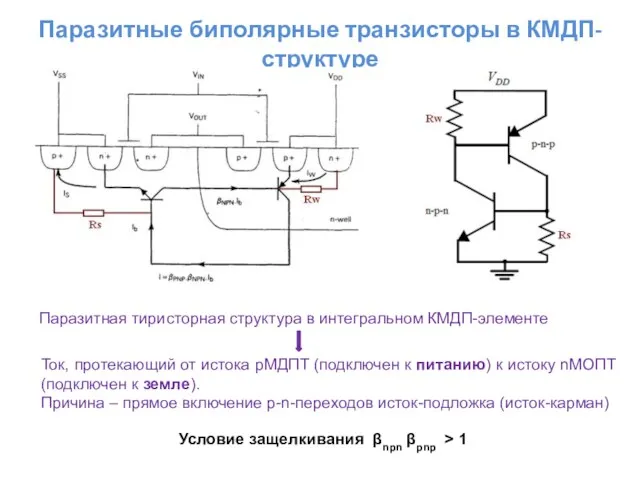

- 25. Паразитные биполярные транзисторы в КМДП-структуре Паразитная тиристорная структура в интегральном КМДП-элементе Условие защелкивания βnpn βpnp >

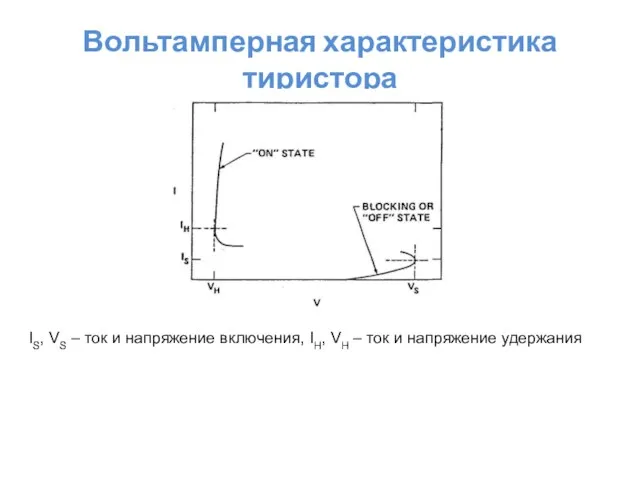

- 26. Вольтамперная характеристика тиристора IS, VS – ток и напряжение включения, IH, VH – ток и напряжение

- 27. Испытания на устойчивость к защелкиванию в статическом режиме (отрицательная помеха) Схема включения тиристора открыванием n+-p перехода

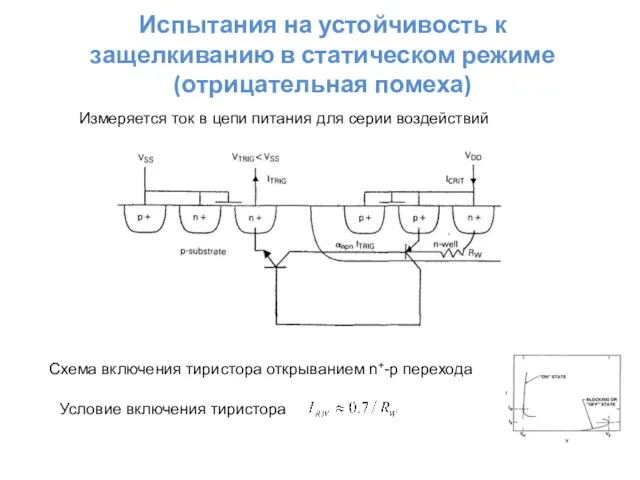

- 28. Испытания на устойчивость к защелкиванию в статическом режиме (положительная помеха) Схема включения тиристора открыванием p+-n перехода

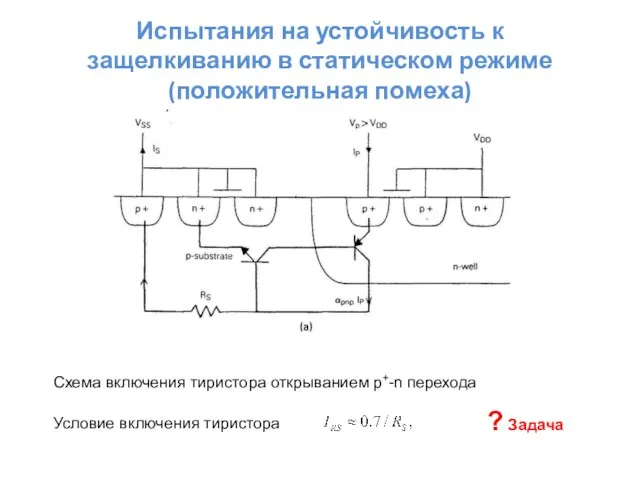

- 29. Методы подавления защелкивания Технологические : уменьшение коэффициентов β паразитных биполярных транзисторов использование ретроградного кармана использование эпитаксиальных

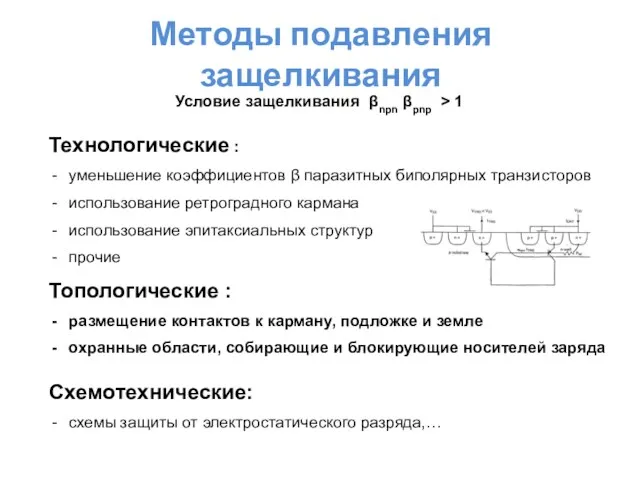

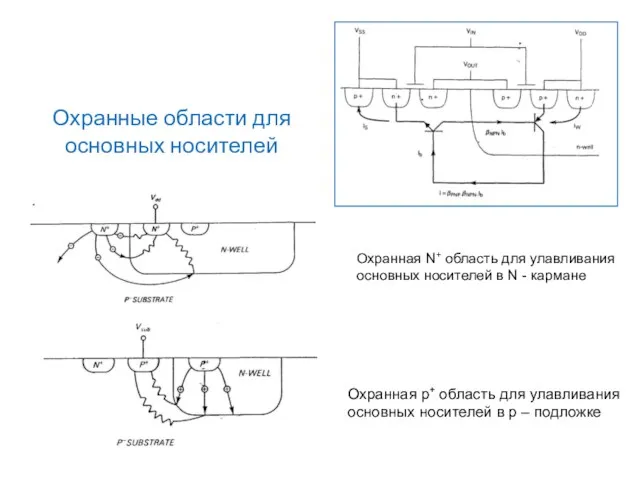

- 30. Охранные области для основных носителей Охранная p+ область для улавливания основных носителей в p – подложке

- 32. Скачать презентацию

Памятник площадь партизан г. Брянск

Памятник площадь партизан г. Брянск Предметно развивающая среда младшей группы.

Предметно развивающая среда младшей группы. Информационные угрозы

Информационные угрозы Урок мужества Что мы знаем о войне.

Урок мужества Что мы знаем о войне. Имидж делового человека

Имидж делового человека Реформация в Европе

Реформация в Европе Мониторинг эффективности команды

Мониторинг эффективности команды Н. Артюхова, рассказ Саша-дразнилка

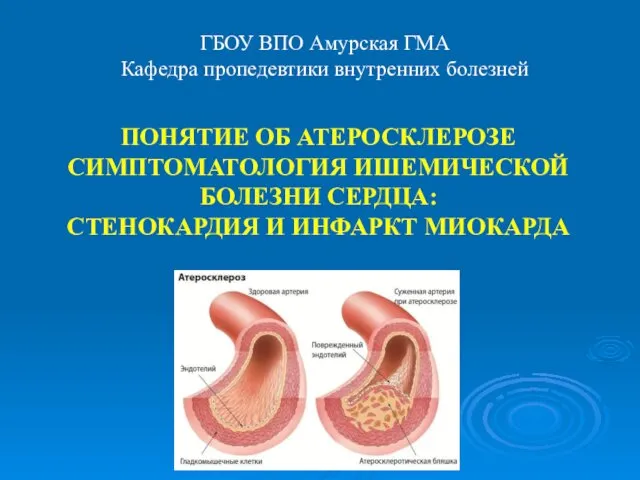

Н. Артюхова, рассказ Саша-дразнилка Атеросклероз. Ишемическая болезнь сердца. Стенокардия и инфаркт миокарда

Атеросклероз. Ишемическая болезнь сердца. Стенокардия и инфаркт миокарда Профессия монтаж и техническая эксплуатация промышленного оборудования

Профессия монтаж и техническая эксплуатация промышленного оборудования Презентация к классному часу в 3 в классе, посвященный Дню Победы 9 мая Застыл солдат у школьного порога.

Презентация к классному часу в 3 в классе, посвященный Дню Победы 9 мая Застыл солдат у школьного порога. Продукция прокатного производства

Продукция прокатного производства Презентация к занятию Мой любимый Волгодонск

Презентация к занятию Мой любимый Волгодонск Биполярные транзисторы

Биполярные транзисторы Презентация Арбуз- ягода

Презентация Арбуз- ягода Тема урока: Коробка

Тема урока: Коробка Поэтическая тетрадь 2. Тест. 3 класс

Поэтическая тетрадь 2. Тест. 3 класс Рак молочной железы при лактации

Рак молочной железы при лактации С Рождеством Христовым!

С Рождеством Христовым! Цифровая безопасность: электронно-обучающая среда для детей и подростков

Цифровая безопасность: электронно-обучающая среда для детей и подростков Транзисторы. Реальная структура транзистора

Транзисторы. Реальная структура транзистора Мобільний зв’язок

Мобільний зв’язок Облікова реєстрація та узагальнення даних бухгалтерського обліку

Облікова реєстрація та узагальнення даних бухгалтерського обліку Строение водорослей

Строение водорослей The solution for Cement Grinding

The solution for Cement Grinding Отчет о проведении дня опытов и экспериментов

Отчет о проведении дня опытов и экспериментов Ко Дню Матери.

Ко Дню Матери. Коммуникативные игры

Коммуникативные игры