Содержание

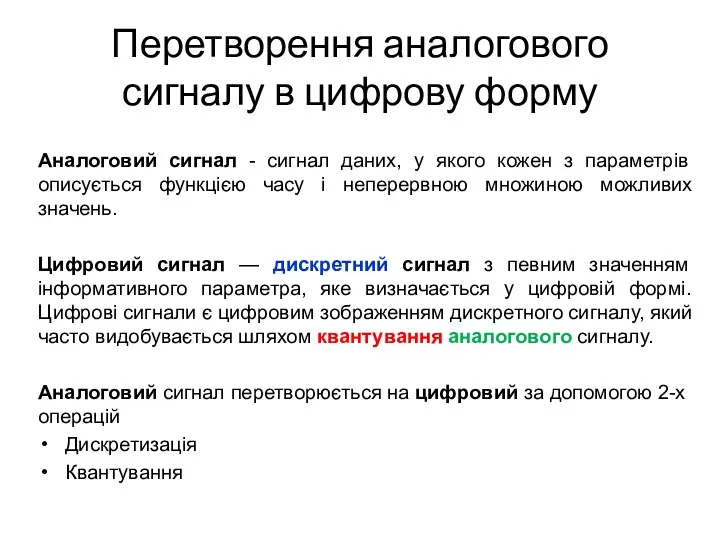

- 2. Перетворення аналогового сигналу в цифрову форму Аналоговий сигнал - сигнал даних, у якого кожен з параметрів

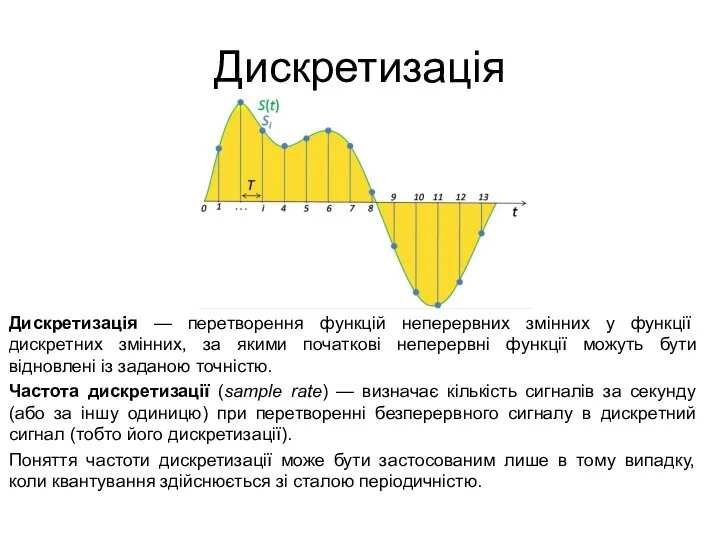

- 3. Дискретизація Дискретизація — перетворення функцій неперервних змінних у функції дискретних змінних, за якими початкові неперервні функції

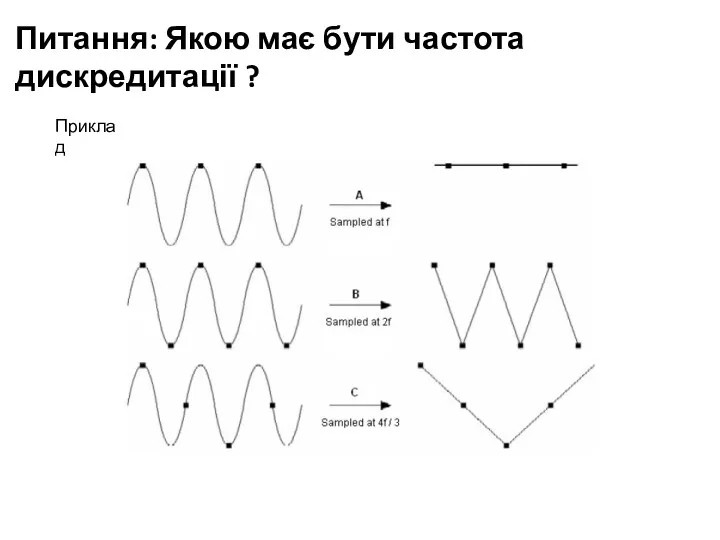

- 4. Питання: Якою має бути частота дискредитації ? Приклад

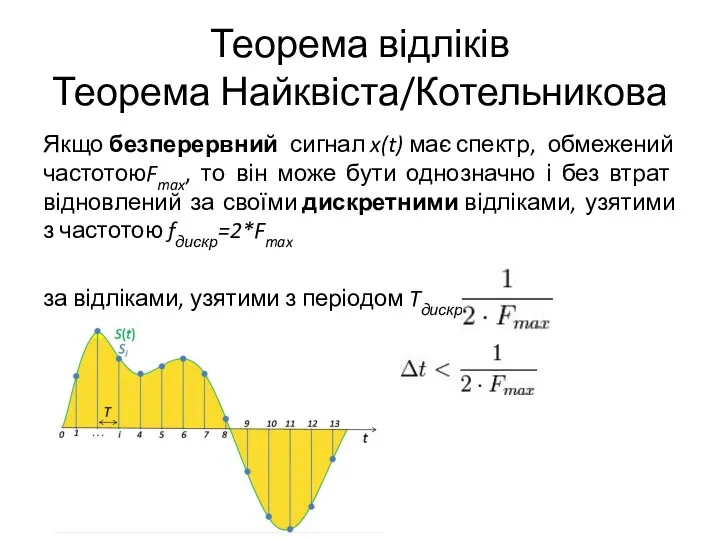

- 5. Теорема відліків Теорема Найквіста/Котельникова Якщо безперервний сигнал x(t) має спектр, обмежений частотоюFmax, то він може бути

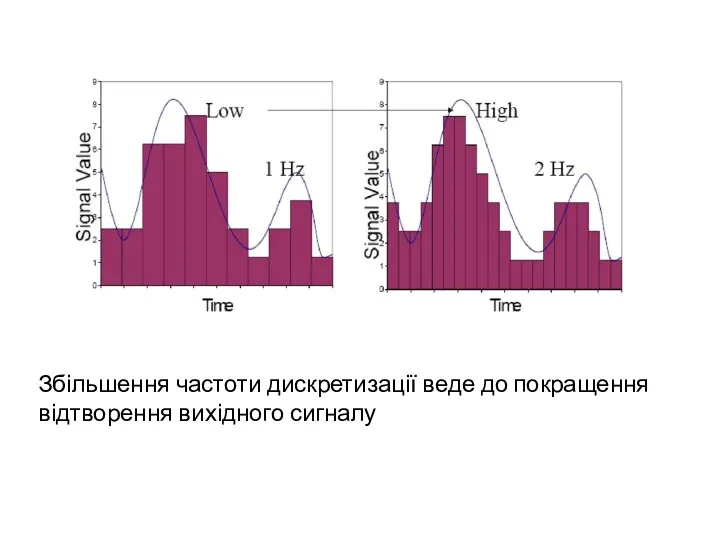

- 6. Збільшення частоти дискретизації веде до покращення відтворення вихідного сигналу

- 7. Аліасінг Питання: Що буде якщо частота дискретизації буде менша ніж подвоєна частота Найквіста Якщо частота дискретизації

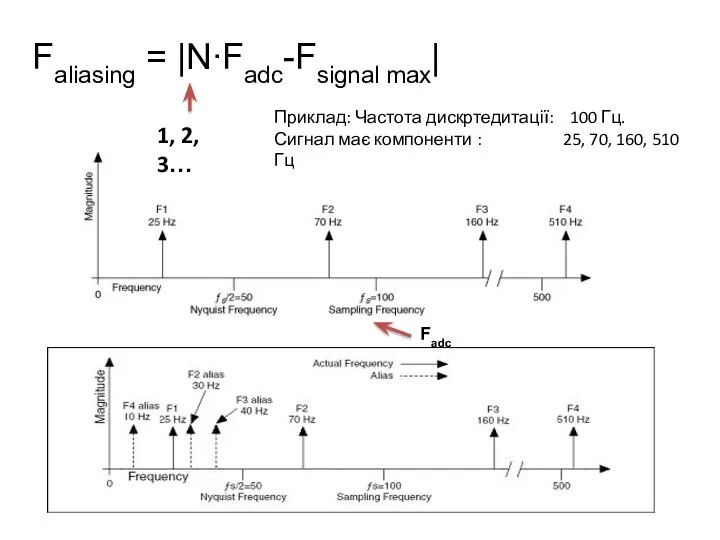

- 8. Faliasing = |N∙Fadc-Fsignal max| 1, 2, 3… Приклад: Частота дискртедитації: 100 Гц. Сигнал має компоненти :

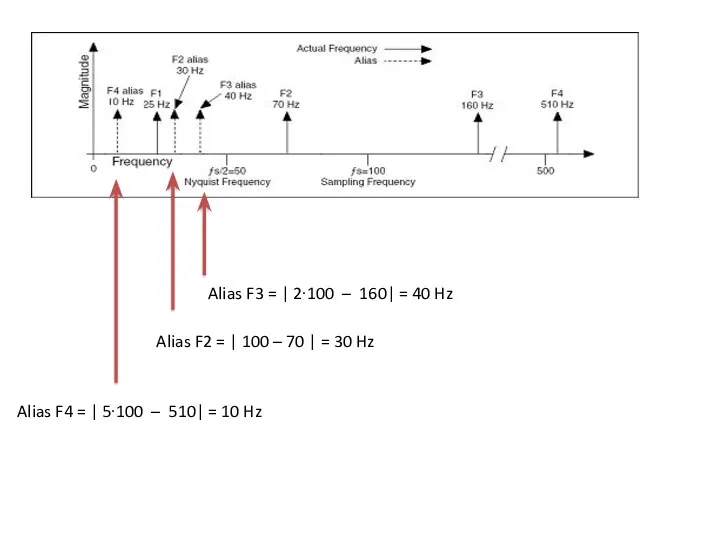

- 9. Alias F4 = | 5∙100 – 510| = 10 Hz Alias F3 = | 2∙100 –

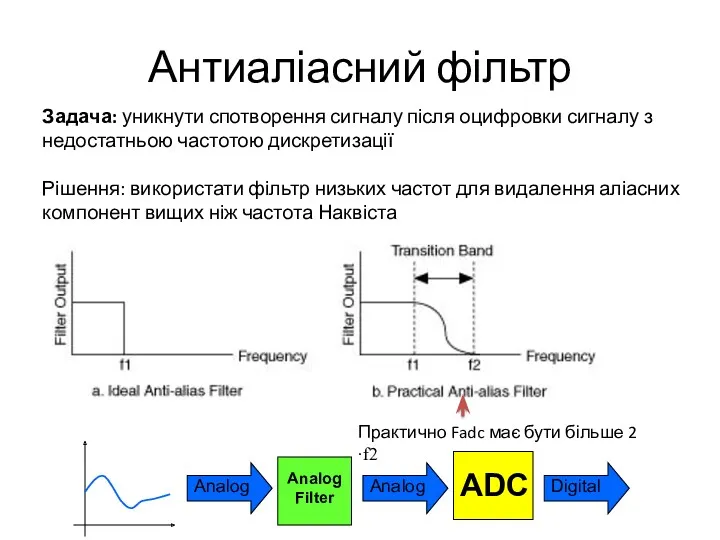

- 10. Антиаліасний фільтр Задача: уникнути спотворення сигналу після оцифровки сигналу з недостатньою частотою дискретизації Рішення: використати фільтр

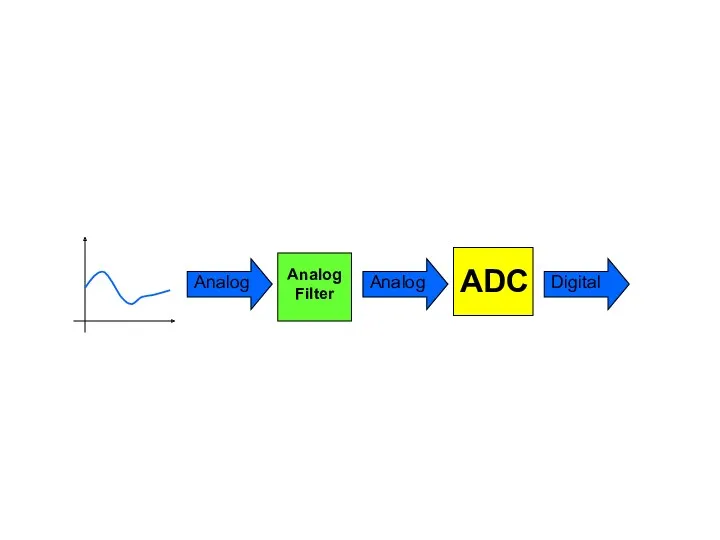

- 11. ADC Analog Digital Analog AnalogFilter

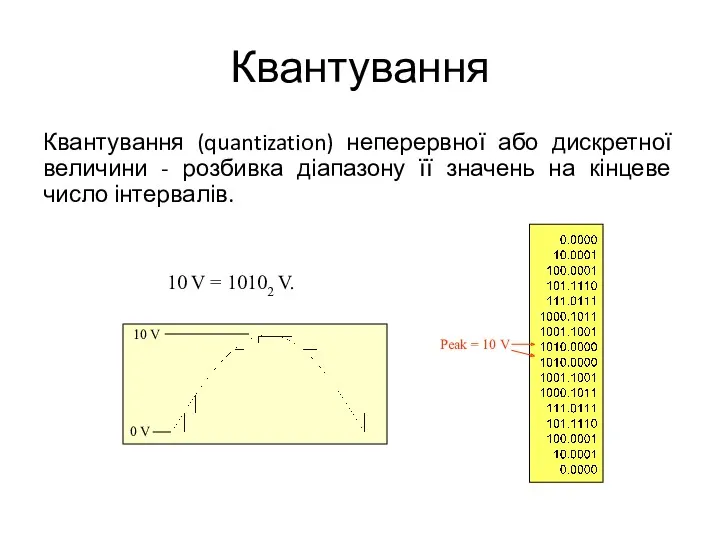

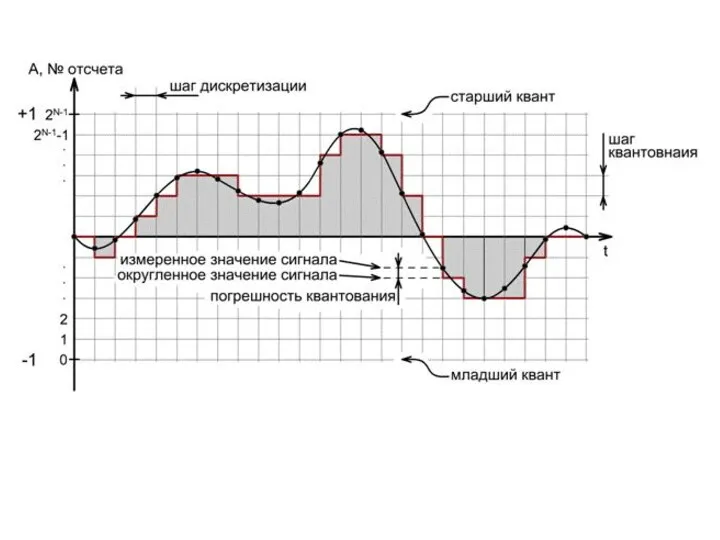

- 12. Квантування Квантування (quantization) неперервної або дискретної величини - розбивка діапазону її значень на кінцеве число інтервалів.

- 13. Цифровий сигнал

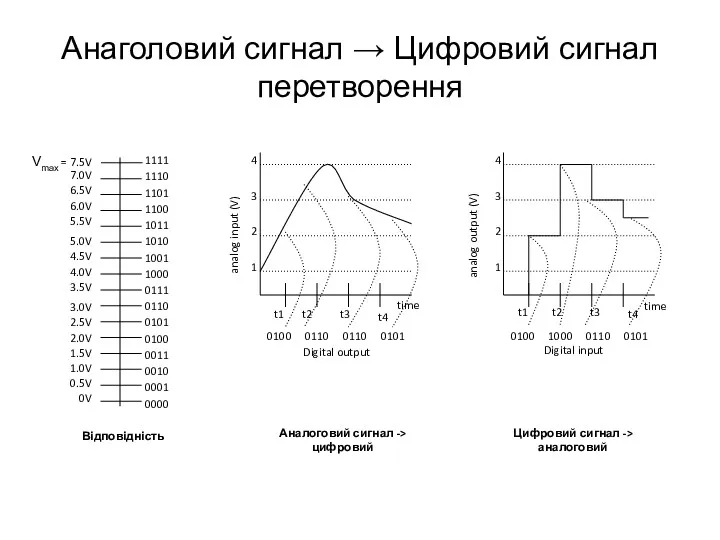

- 14. Анаголовий сигнал → Цифровий сигнал перетворення

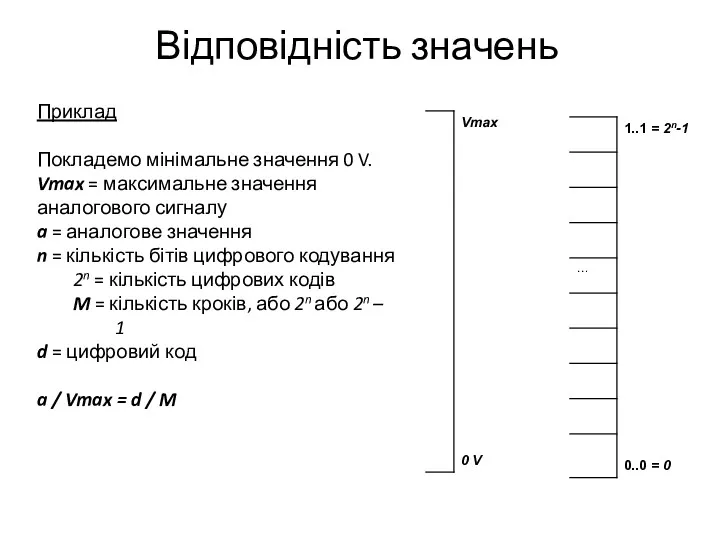

- 15. Відповідність значень Приклад Покладемо мінімальне значення 0 V. Vmax = максимальне значення аналогового сигналу a =

- 16. Роздільна здатність Покладемо n = 2 M = кількість кроків M = 2n – 1 3

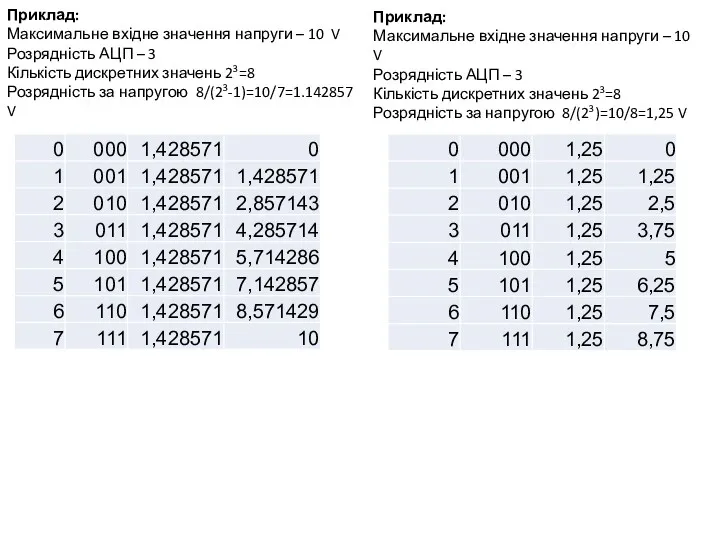

- 17. Приклад: Максимальне вхідне значення напруги – 10 V Розрядність АЦП – 3 Кількість дискретних значень 23=8

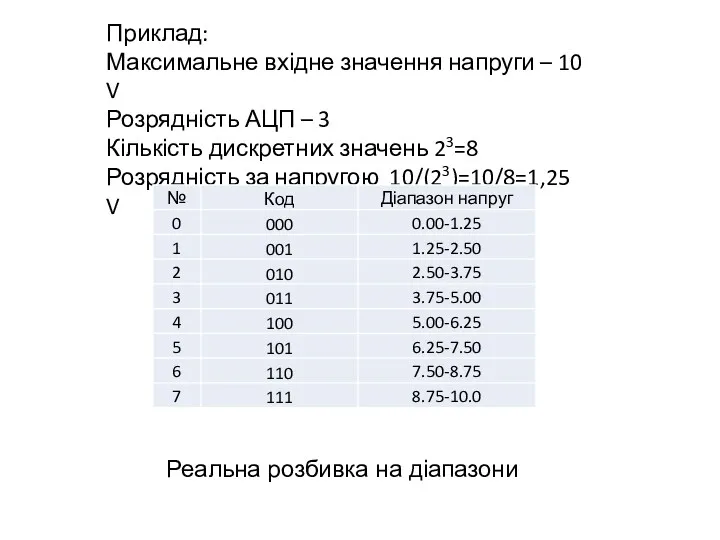

- 18. Приклад: Максимальне вхідне значення напруги – 10 V Розрядність АЦП – 3 Кількість дискретних значень 23=8

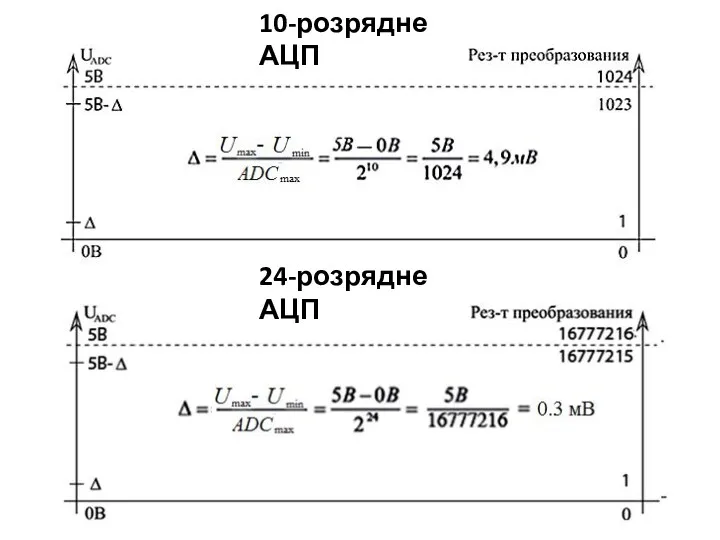

- 19. 10-розрядне АЦП 24-розрядне АЦП

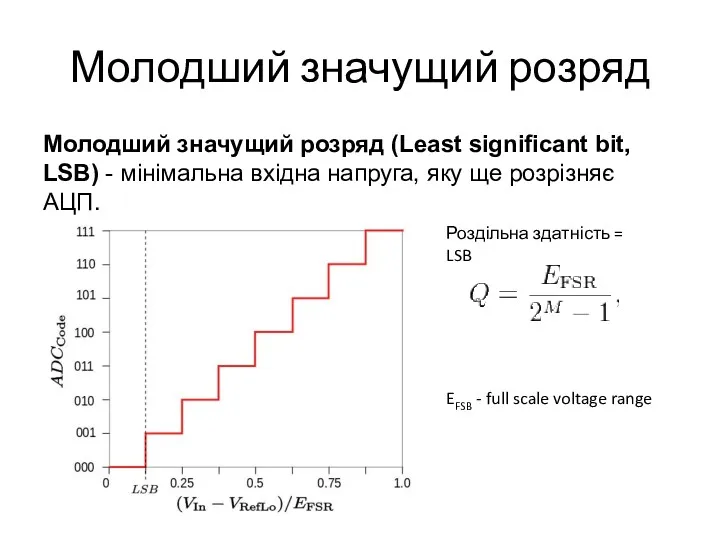

- 20. Молодший значущий розряд Молодший значущий розряд (Least significant bit, LSB) - мінімальна вхідна напруга, яку ще

- 21. Практична роздільна здатність На практиці роздільна здатність АЦП обмежена відношенням сигнал / шум вхідного сигналу. При

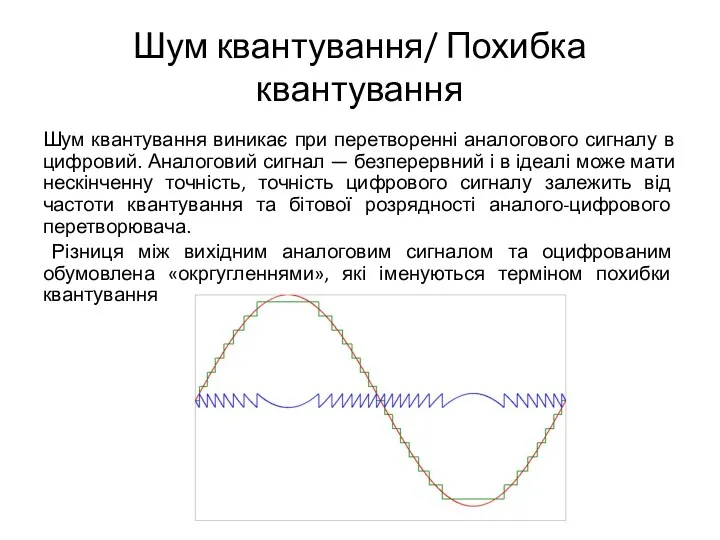

- 22. Шум квантування/ Похибка квантування Шум квантування виникає при перетворенні аналогового сигналу в цифровий. Аналоговий сигнал —

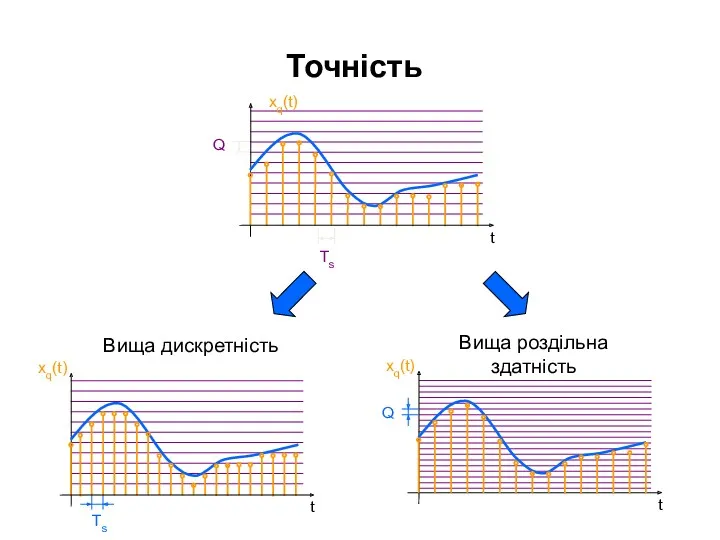

- 24. t xq(t) Точність

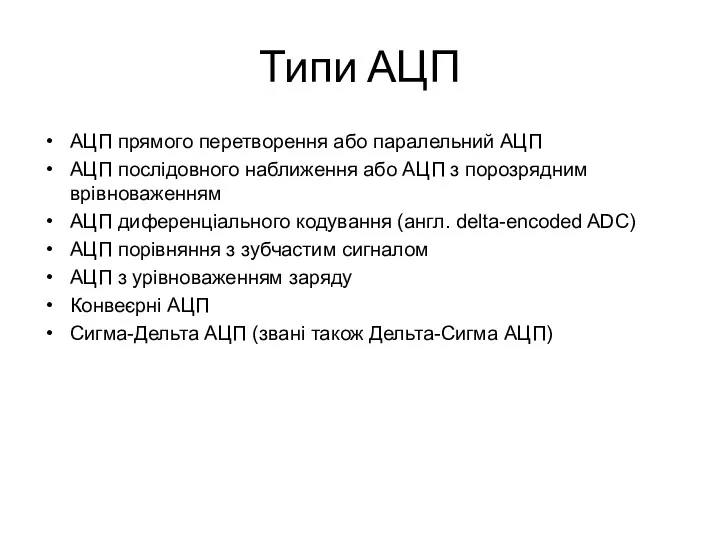

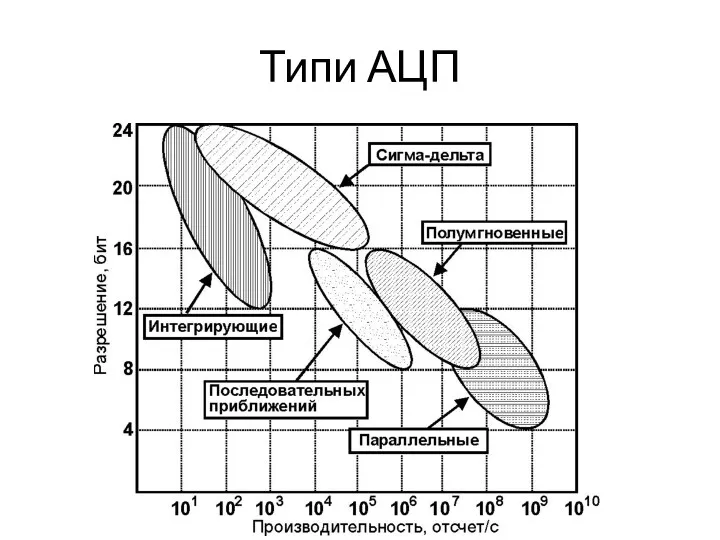

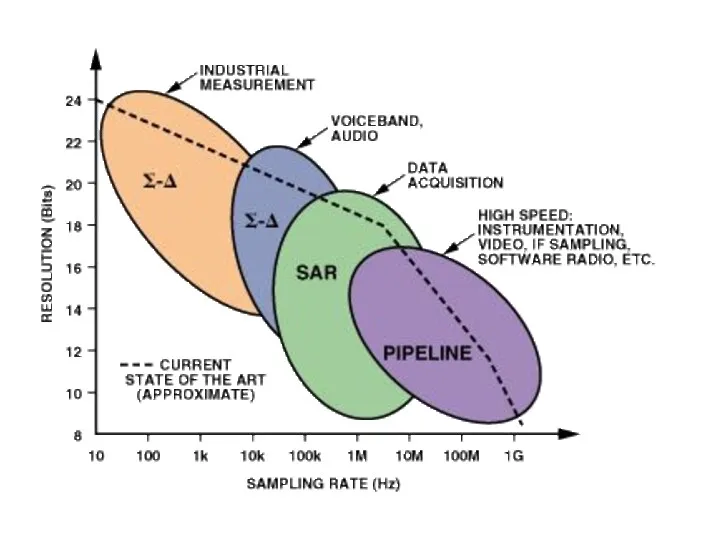

- 25. Типи АЦП АЦП прямого перетворення або паралельний АЦП АЦП послідовного наближення або АЦП з порозрядним врівноваженням

- 26. Типи АЦП

- 28. АЦП прямого перетворення або паралельний АЦП Як тільки напруга на аналоговому вході перевищує опорну напругу на

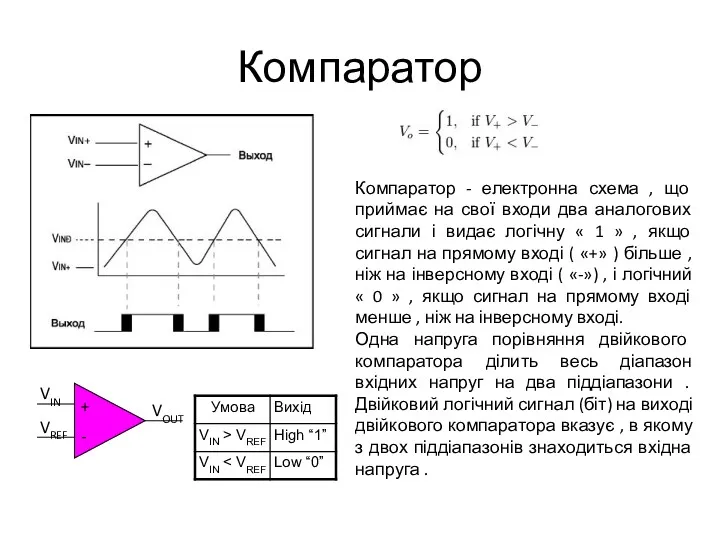

- 29. Компаратор Компаратор - електронна схема , що приймає на свої входи два аналогових сигнали і видає

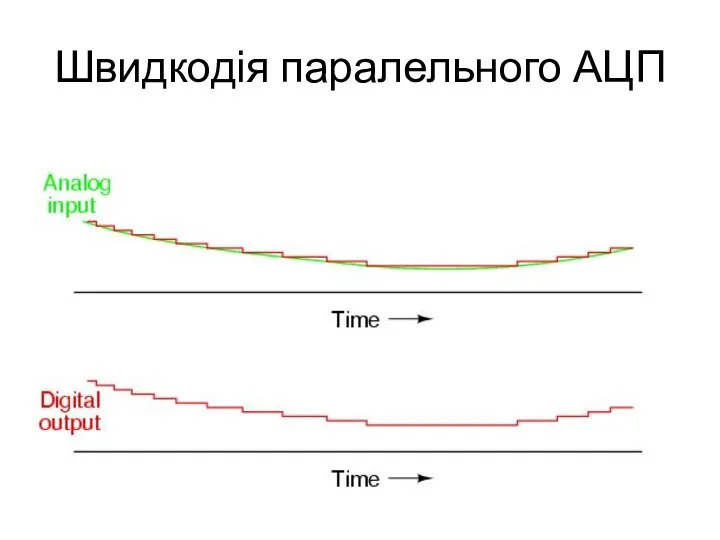

- 30. Швидкодія паралельного АЦП

- 31. Переваги і недоліки паралельного АЦП

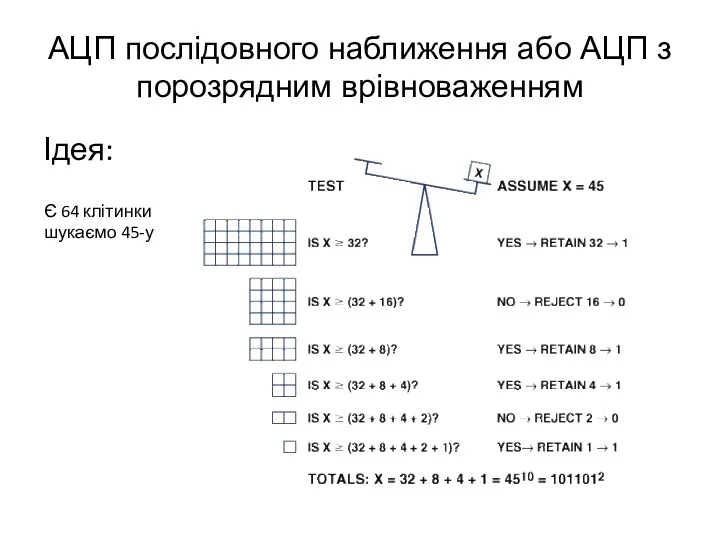

- 32. АЦП послідовного наближення або АЦП з порозрядним врівноваженням Ідея: Є 64 клітинки шукаємо 45-у

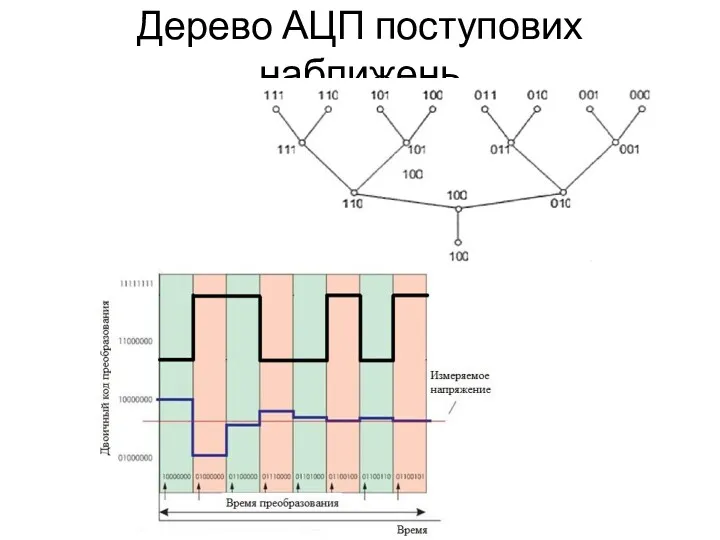

- 33. Дерево АЦП поступових наближень

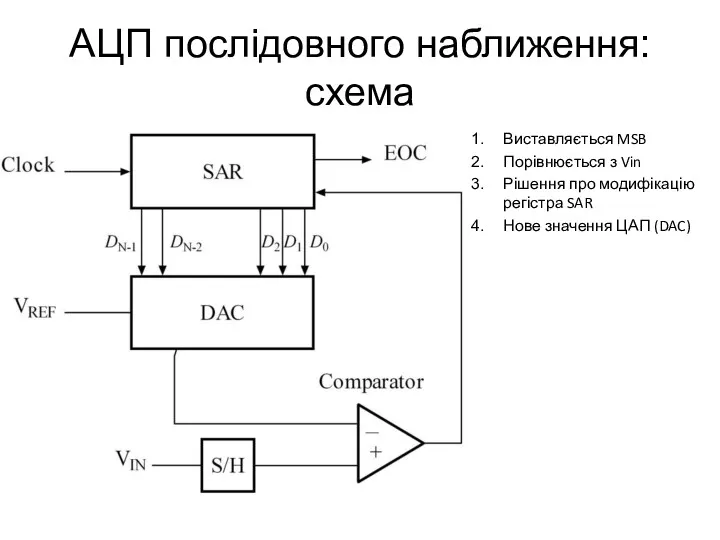

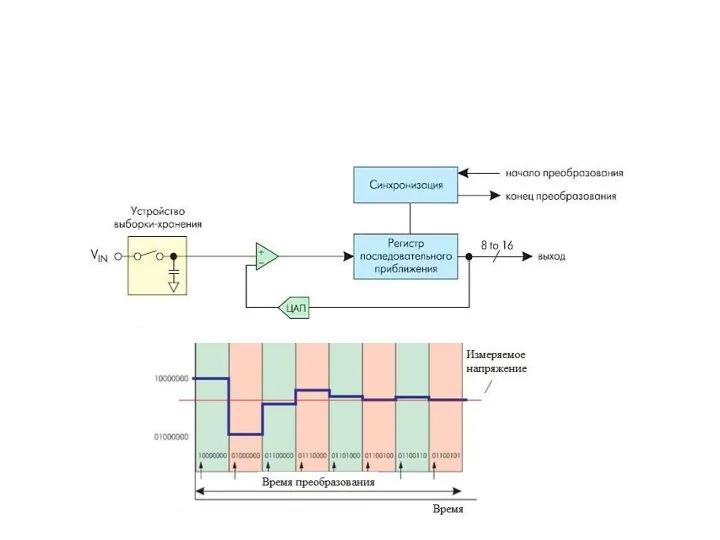

- 34. АЦП послідовного наближення: схема Виставляється MSB Порівнюється з Vin Рішення про модифікацію регістра SAR Нове значення

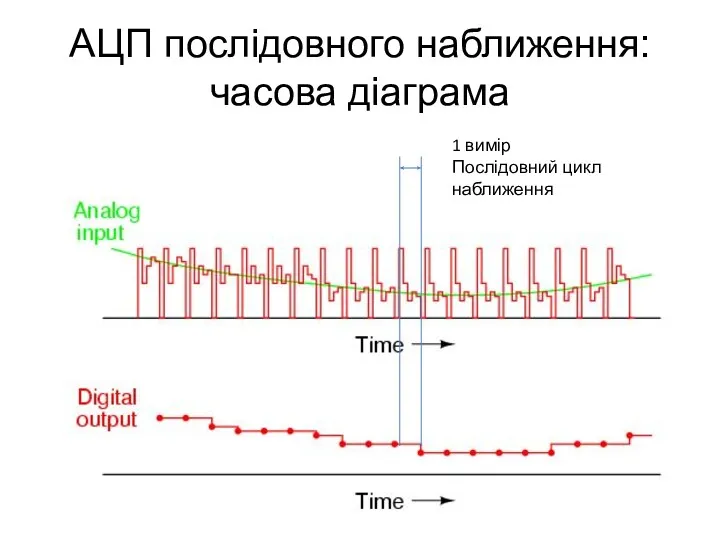

- 36. АЦП послідовного наближення: часова діаграма 1 вимір Послідовний цикл наближення

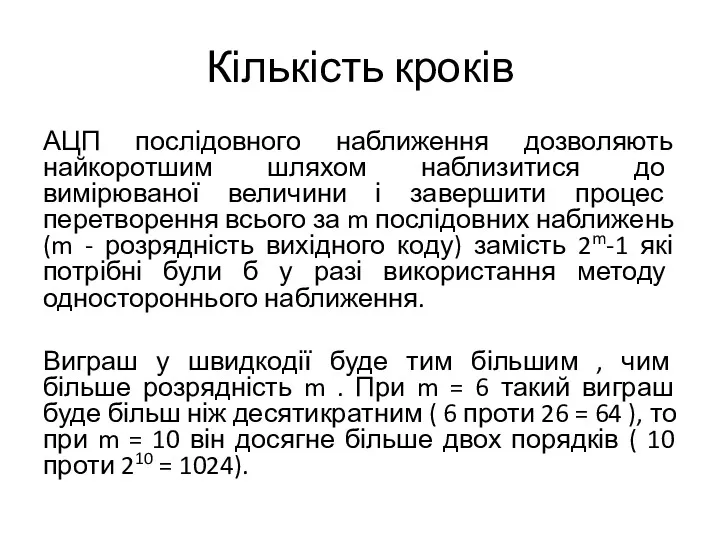

- 37. Кількість кроків АЦП послідовного наближення дозволяють найкоротшим шляхом наблизитися до вимірюваної величини і завершити процес перетворення

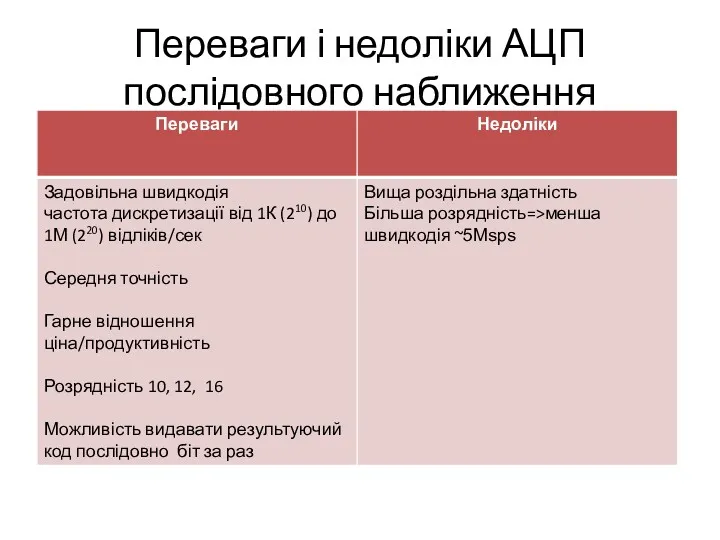

- 38. Переваги і недоліки АЦП послідовного наближення

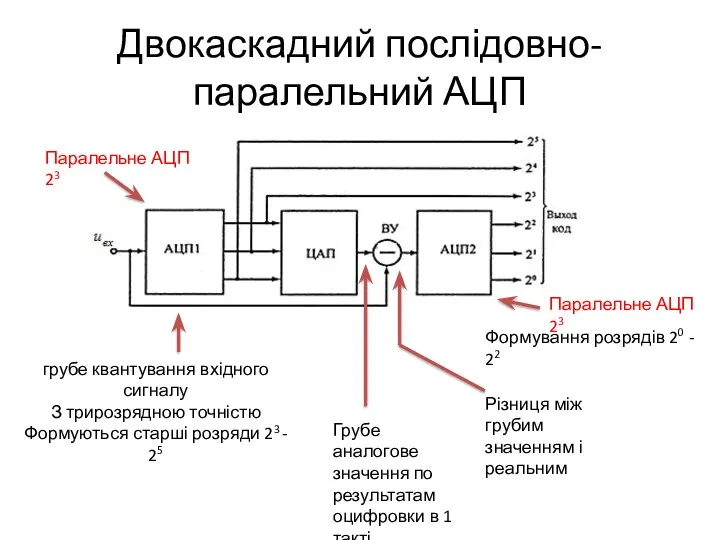

- 39. Двокаскадний послідовно-паралельний АЦП грубе квантування вхідного сигналу З трирозрядною точністю Формуються старші розряди 23 - 25

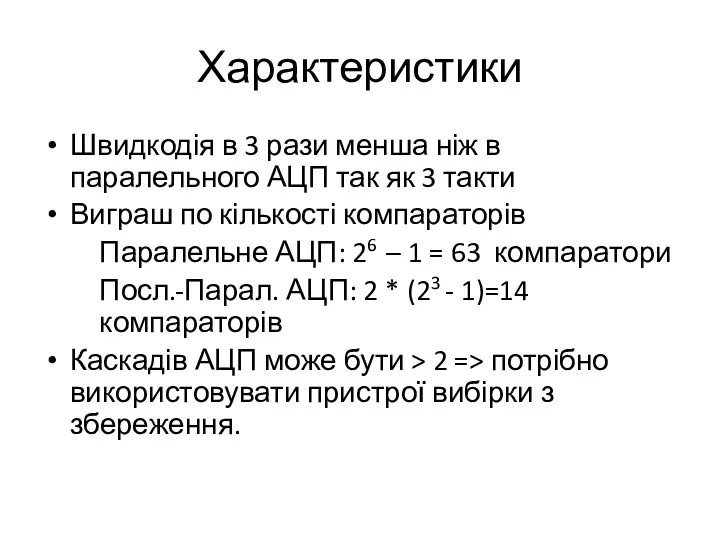

- 40. Характеристики Швидкодія в 3 рази менша ніж в паралельного АЦП так як 3 такти Виграш по

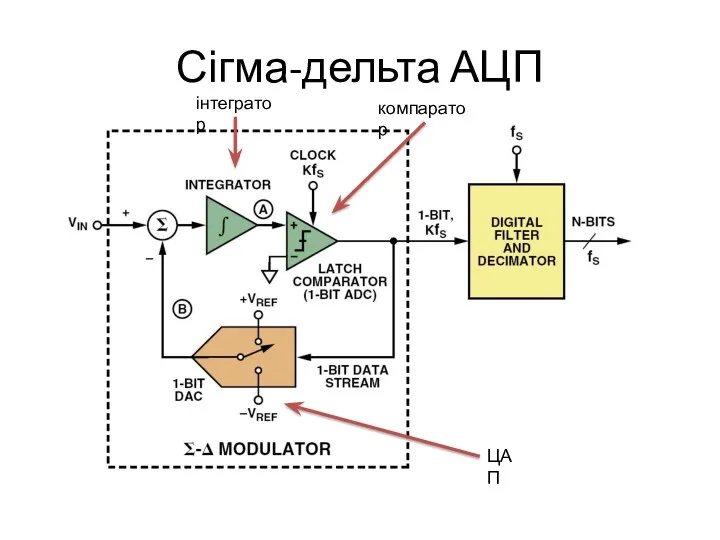

- 41. Сігма-дельта АЦП інтегратор компаратор ЦАП

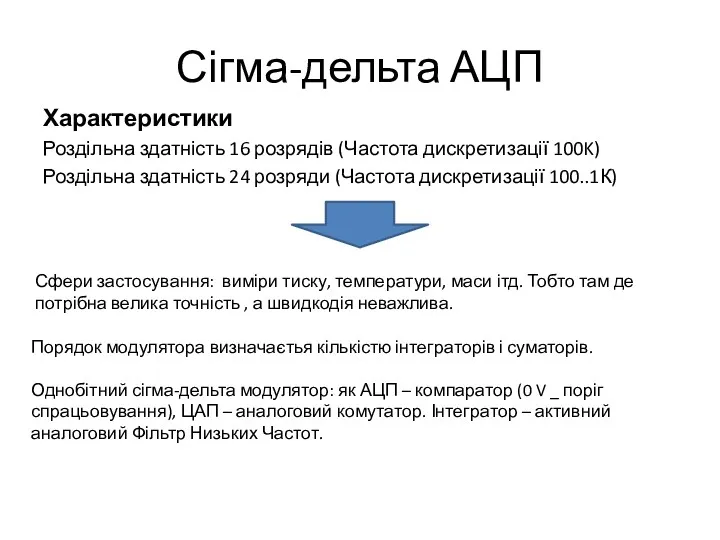

- 42. Сігма-дельта АЦП Характеристики Роздільна здатність 16 розрядів (Частота дискретизації 100K) Роздільна здатність 24 розряди (Частота дискретизації

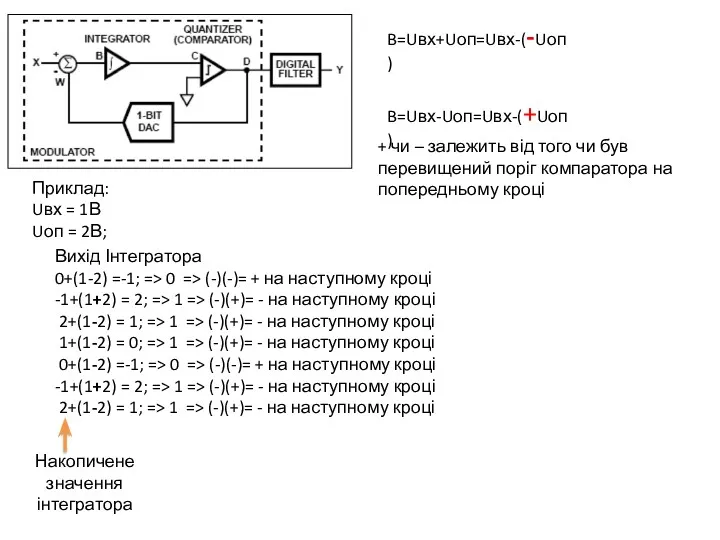

- 43. B=Uвх+Uоп=Uвх-(-Uоп) B=Uвх-Uоп=Uвх-(+Uоп) + чи – залежить від того чи був перевищений поріг компаратора на попередньому кроці

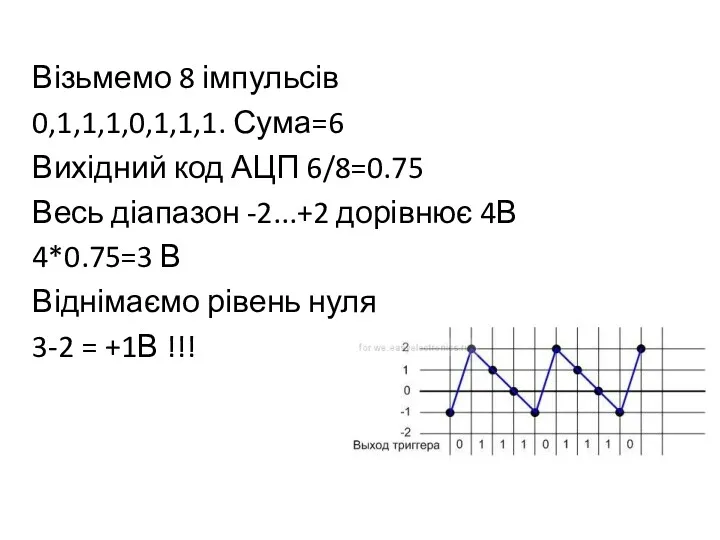

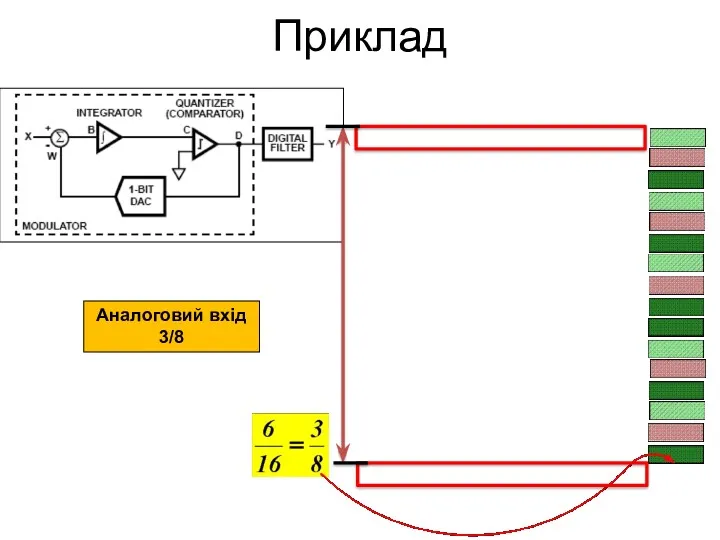

- 44. Візьмемо 8 імпульсів 0,1,1,1,0,1,1,1. Сума=6 Вихідний код АЦП 6/8=0.75 Весь діапазон -2...+2 дорівнює 4В 4*0.75=3 В

- 45. Часова діаграма: cігма-дельта модулятор Завдяки негативному зворотньому зв’язку навколо інтегратора середнє значення сигналу в точці B

- 47. Приклад Аналоговий вхід 3/8

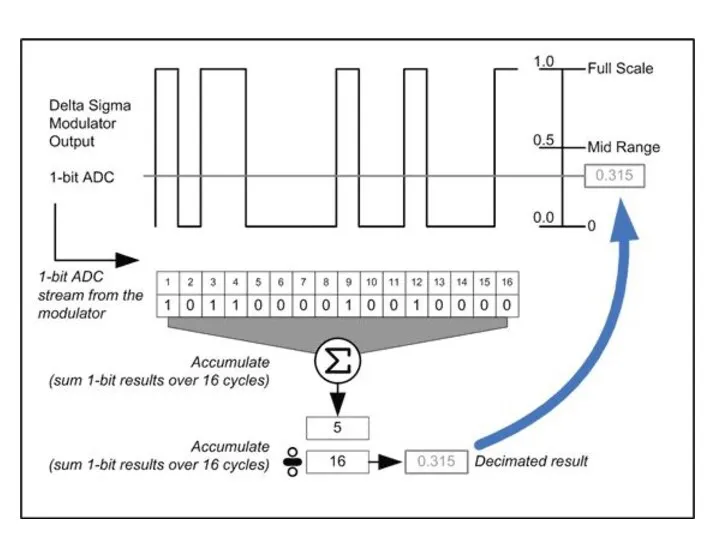

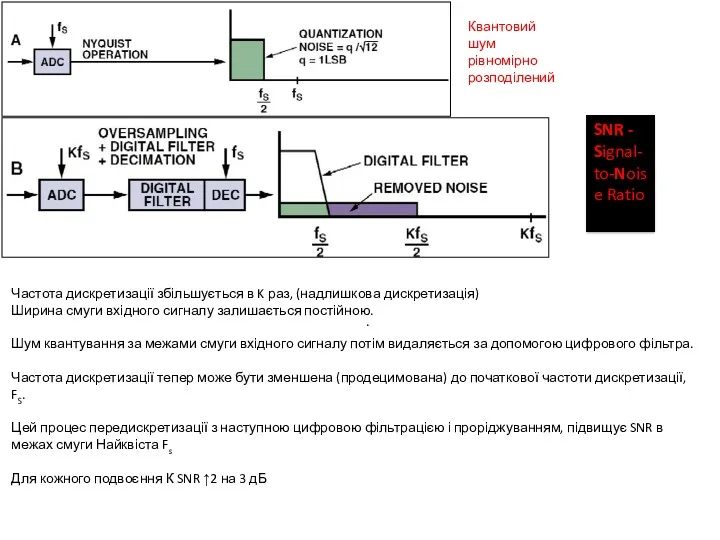

- 48. Квантовий шум рівномірно розподілений . Частота дискретизації збільшується в K раз, (надлишкова дискретизація) Ширина смуги вхідного

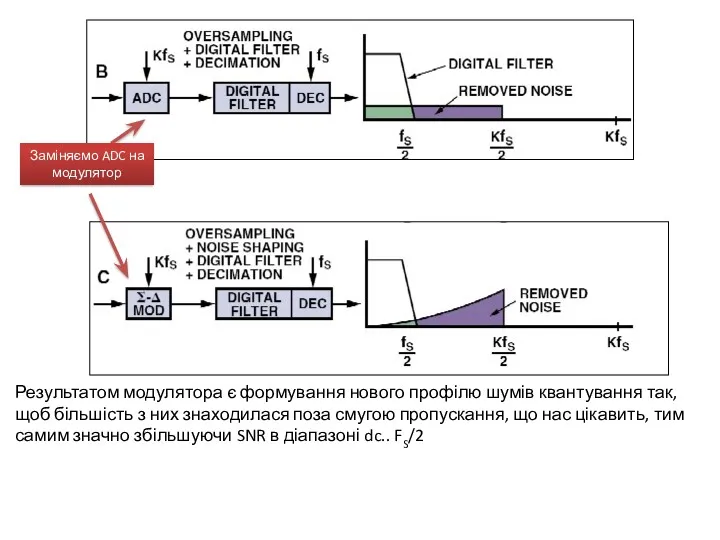

- 49. Заміняємо ADC на модулятор Результатом модулятора є формування нового профілю шумів квантування так, щоб більшість з

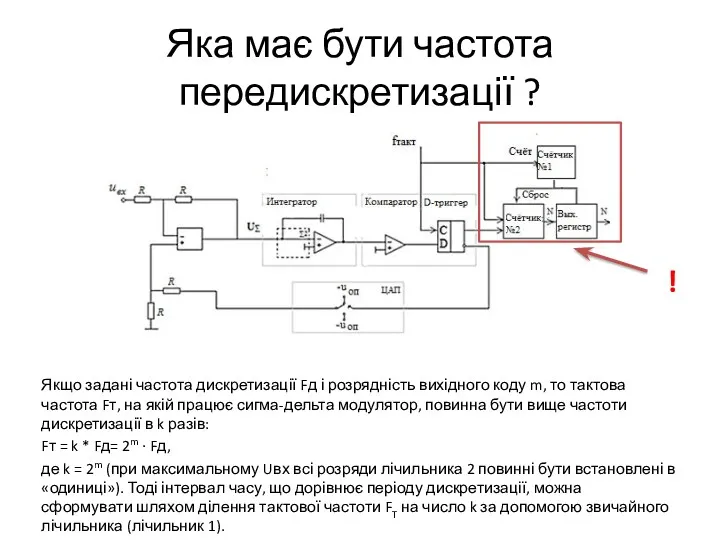

- 50. Яка має бути частота передискретизації ? Якщо задані частота дискретизації Fд і розрядність вихідного коду m,

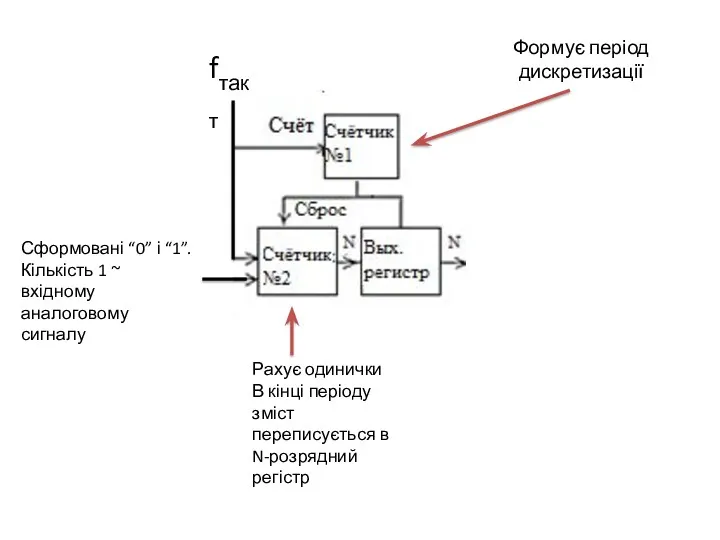

- 51. Сформовані “0” і “1”. Кількість 1 ~ вхідному аналоговому сигналу Формує період дискретизації Рахує одинички В

- 52. Елементи АЦП: лічильник

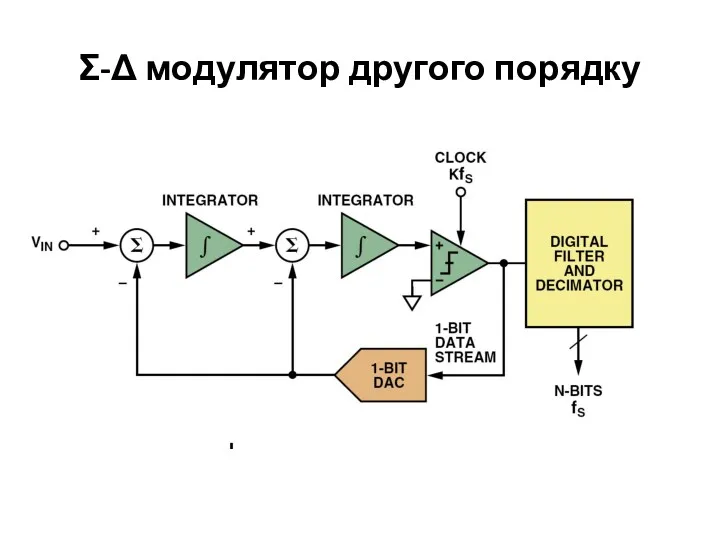

- 53. Σ-Δ модулятор другого порядку

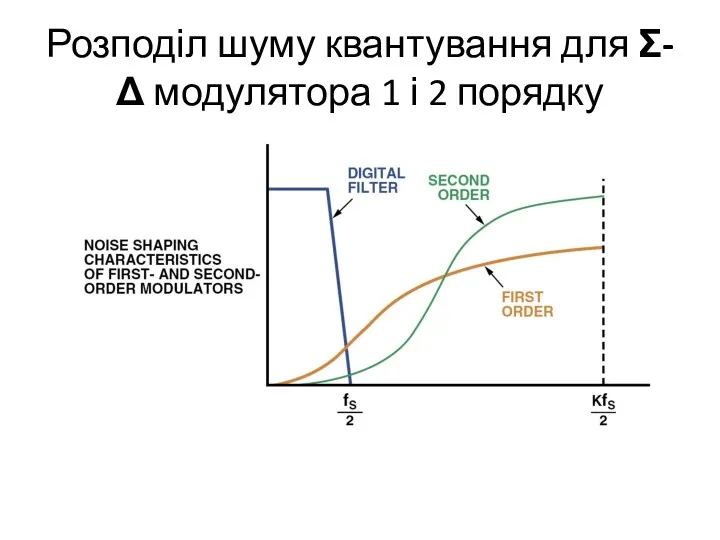

- 54. Розподіл шуму квантування для Σ-Δ модулятора 1 і 2 порядку

- 55. АЦП з динамічною компенсацією Послідовне наближення до напруги, що вимірюється Лічильник рахує кількість імпульсів Час перетворення

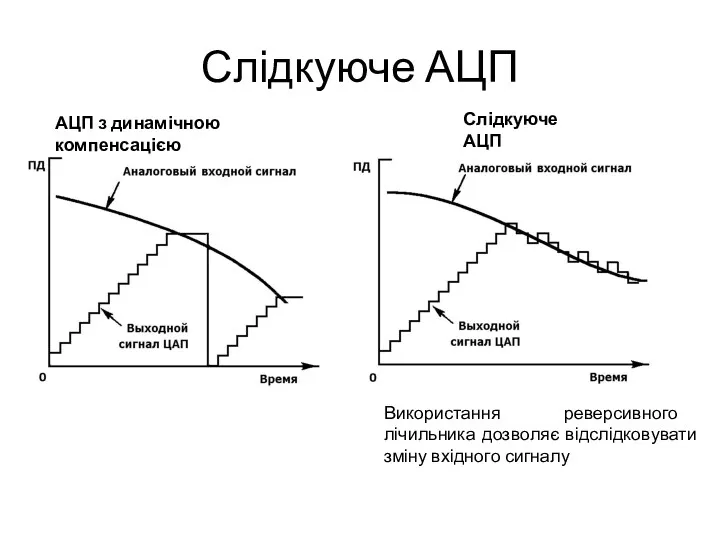

- 56. Слідкуюче АЦП АЦП з динамічною компенсацією Слідкуюче АЦП Використання реверсивного лічильника дозволяє відслідковувати зміну вхідного сигналу

- 57. АЦП з перетворенням напруги в частоту Перетворювач Напруга-Частота Передаючи пристрій Приймаючий пристрій … Лічильник Таймер Цифровий

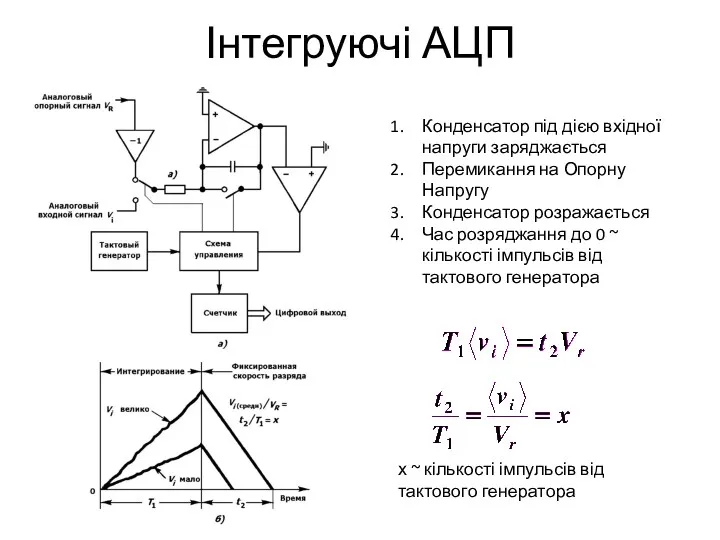

- 58. Інтегруючі АЦП Конденсатор під дією вхідної напруги заряджається Перемикання на Опорну Напругу Конденсатор розражається Час розряджання

- 59. Інтегруючі АЦП АЦП даного типу нечутливі до імпульсних перешкод . АЦП даного типу нечутливі до періодичних

- 61. Скачать презентацию

IDU0075 Veebiteenused. (L3)

IDU0075 Veebiteenused. (L3) Компьютерные сети. Основные задачи построения сетей. Лекция 3

Компьютерные сети. Основные задачи построения сетей. Лекция 3 Периферийные устройства

Периферийные устройства MS Word программасында құжатқа сурет кірістіру

MS Word программасында құжатқа сурет кірістіру Поняття користувача й сеансу користувача. Урок 27

Поняття користувача й сеансу користувача. Урок 27 Показательный урок по информатике и ИКТ Системы счисления

Показательный урок по информатике и ИКТ Системы счисления Язык программирования С

Язык программирования С Интерактивное ТВ 2 0. Описание продукта для дилеров

Интерактивное ТВ 2 0. Описание продукта для дилеров Проектирование программных средств

Проектирование программных средств Основы социальной информатики. Информационные ресурсы

Основы социальной информатики. Информационные ресурсы Преобразование логических выражений. Элементы теории множеств и алгебры логики

Преобразование логических выражений. Элементы теории множеств и алгебры логики Презентация к уроку Основные этапы разработки и исследования моделей на компьютере

Презентация к уроку Основные этапы разработки и исследования моделей на компьютере Логические основы компьютера. Базовые логические элементы. Построение логических схем

Логические основы компьютера. Базовые логические элементы. Построение логических схем Социальные сети

Социальные сети 9 класс. Алгоритмизация.

9 класс. Алгоритмизация. Решение задач части В демоверсии ЕГЭ-2013 по информатике

Решение задач части В демоверсии ЕГЭ-2013 по информатике Форматирование и редактирования текса Microsoft Word. Технология обработки текстовой информации

Форматирование и редактирования текса Microsoft Word. Технология обработки текстовой информации АО ТАСКОМ. Личный Кабинет. Инструкция по оформлению заявок

АО ТАСКОМ. Личный Кабинет. Инструкция по оформлению заявок Big Data

Big Data Программирование разветвляющихся алгоритмов

Программирование разветвляющихся алгоритмов Информационные ресурсы и сервисы интернета коммуникационные технологии

Информационные ресурсы и сервисы интернета коммуникационные технологии Информационный бизнес. Тема 1

Информационный бизнес. Тема 1 Действия с информацией. Хранение информации

Действия с информацией. Хранение информации Дистанційне навчання

Дистанційне навчання Автоматизированное проектирование ИС. (Лекция 5)

Автоматизированное проектирование ИС. (Лекция 5) Процедуры и функции. Lambda function. *args, **kwargs в Python

Процедуры и функции. Lambda function. *args, **kwargs в Python Android компоненттері

Android компоненттері Основы веб-разработки. CSS. Введение. (Тема 6)

Основы веб-разработки. CSS. Введение. (Тема 6)